К сожалению, с помощью тренажера Emona DATEx реализовать и QPSK модулятор и полный демодулятор не представляется возможным. Однако, можно продемонстрировать, как методом фазовой дискриминации, используемой в QPSK модуляторе, извлечь один из BPSK сигналов из QPSK сигнала. В этой части эксперимента именно это и предлагается выполнить.

41. Закройте программу анализатора спектра (NI ELVIS Dynamic Signal Analyzer VI).

42. Найдите модуль PHASE SHIFTER (Фазовращатель) на программной панели управления DATEx и установите виртуальный регулятор фазового сдвига (PHASE Change) в положение 0°. Установите регулятор Frequency частоты среза перестраиваемого ФНЧ в крайнее правое положение, а регулятор коэффициента усиления GAIN в среднее положение.

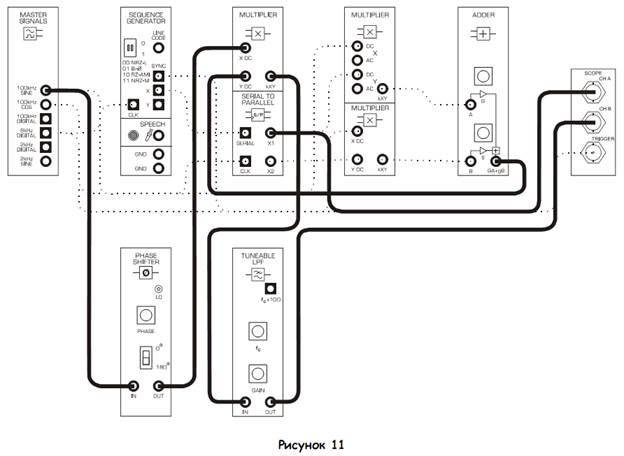

43. Внесите изменения в схему согласно рисунку 11.

Примечание: Чтобы не запутаться, рекомендуется помечать каждое соединение при

его добавлении.

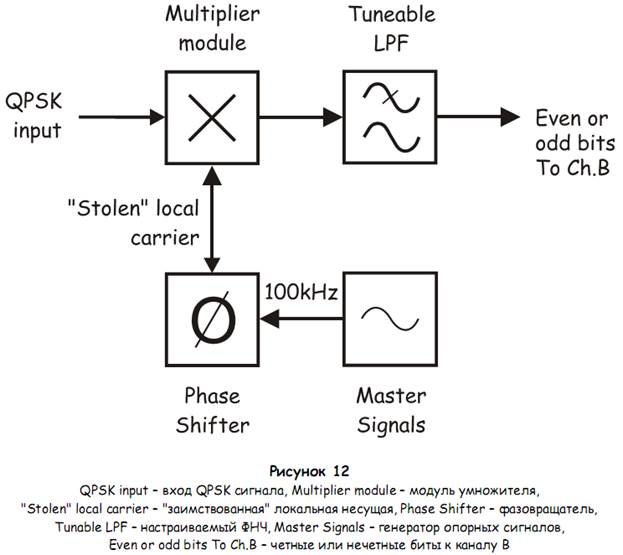

Дополнительные соединения могут быть представлены блок-схемой, приведенной на рисунке 12. Если вы сравните ее с блок-схемой, приведенной на рисунке 2 (предварительное обсуждение), то заметите, что здесь реализованы основные узлы одного из плеч QPSK демодулятора (I или Q).

44. Снова запустите осциллограф однократным нажатием на кнопку RUN.

45. Сравните четные биты на выходе X1 последовательно-параллельного преобразователя с данными на выходе ФНЧ.

46. Вращая вправо-влево виртуальный регулятор подстройки фазового сдвига Phase Adjust, наблюдайте, что происходит с демодулированным сигналом.

47. Установите виртуальный регулятор Phase Change в положение 180° и повторите п. 46.

Вопрос 7

Что произойдет в результате регулировки фазы восстанавливаемого сигнала – он будет состоять из 3 или 4 логических уровней вместо ожидаемых 2?

Рассогласование по фазе приводит к появлению сигналов с промежуточными уровнями.

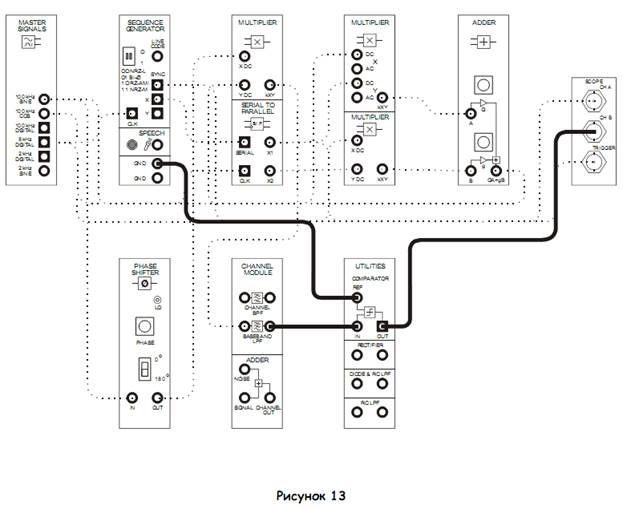

48. Измените схему, как показано на рисунке 13.

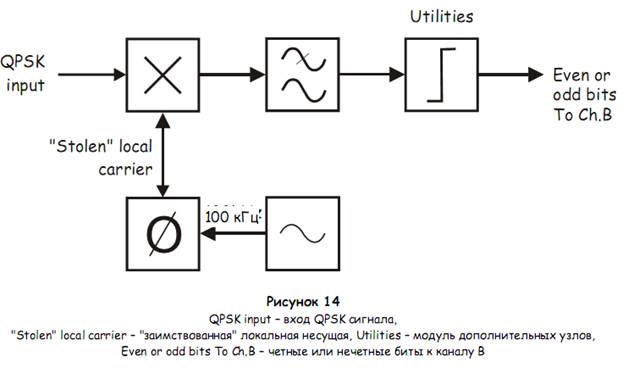

Дополнение компаратором из модуля вспомогательных блоков (UTILITIES) отражено в блок-схеме на рисунке 14. Если сравните эту блок-схему с той, что приведена на рисунке 2, то увидите, что внесенное изменение полностью реализует одно плечо QPSK демодулятора.

49. Снова установите фазовый сдвиг 0° в модуле Phase Shifter с помощью виртуального регулятора Phase Change.

50. Сравните четные биты на выходе X1 последовательно-параллельного преобразователя и на выходе ФНЧ.

51. С помощью виртуального регулятора Phase Adjust подстраивайте фазовый сдвиг до тех пор, пока четные биты не будут восстановлены (фазовый сдвиг игнорируйте).

Вопрос 8

Чему равен фазовый сдвиг между локальной несущей и несущей, используемой для генерации сигналов PSKI и PSKQ?

Составляющая PSKI находится в фазе с локальной несущей, а PSKQ – сдвинута на 90º.

52. Отключите вход канала A осциллографа от выхода X1 последовательно-параллельного преобразователя и подключите его к выходу X2 для наблюдения нечетных битов.

53. Сравните нечетные биты с восстановленными данными. Они должны отличаться.

54. Установите виртуальный регулятор Phase Change в положение180°.

55. С помощью виртуального регулятора Phase Adjust подстраивайте фазовый сдвиг до тех пор, пока не будут восстановлены нечетные биты (фазовый сдвиг игнорируйте).

Вопрос 9

Чему теперь равен фазовый сдвиг между локальной несущей и несущей,

используемой для генерации сигналов PSKI и PSKQ?

Составляющая PSKQ находится в фазе с локальной несущей, а PSKI – сдвинута на 90º.

Вопрос 10

Почему рассматриваемый демодулятор является только половиной полноценного QPSK приемника?

Исходный поток данных разделяется и передается по два бита одновременно, а имеющийся приемник может восстановить только один из наборов бит.

2015-07-04

2015-07-04 750

750