Регистры и Счетчики на основе триггеров. Анализ и синтез

Цель работы

1. Знакомство с принципом действия регистров и счетчиков различных типов.

2. Овладение методикой синтеза параллельных и последовательных регистров и их комбинаций; синхронных прямых, обратных (с произвольным модулем счета) и реверсивных счетчиков.

3.Ознакомление с особенностями работы типовых схем регистров и счетчиков в интегральном исполнении на разных типах микросхем.

Основные положения

3.2.1 Послідовністні схеми регістрів виконуються на основі тригерів і мають такі основні типи:

1. З паралельним входом і виходом-регістр пам`яті (Р.Пар.Вх.Пар.Вих.-інформація при завантаженні, розвантаженні регістру на його входи, виходи надходить одночасно-паралельно);

2. З паралельним входом і послідовним виходом (Р.Пар.Вх.Посл.Вих.-інформація при завантаженні регістру на його усі входи надходить одночасно-паралельно, а при розвантаженні надходить з одного виходу послідовно-біт за бітом);

3. З послідовним входом і паралельним виходом (Р.Посл.Вх.Пар.Вих.-інформація при завантаженні на один вхід надходить послідовно, а при розвантаженні проводится одночасно-паралельно з усіх його розрядів-виходів);

4. З послідовними входом і виходом (Р.Посл.Вх.Вих.-інформація на один вхід при його завантаженні та з одного виходу при його розвантаженні надходить послідовно-біт за бітом);

5. Комбінаційні з різними засобами приймання/видавання інформації. Вони поділяються на однофазні (сигнал передається по одному каналу) і парофазні-по двох каналах (прямий, обратний код).

Функція регистрів- зберігання, зсув даних і отримання прямих, обернених і дадаткових їх кодів.

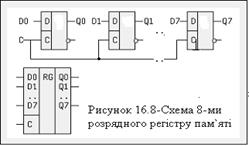

Аналіз паралельних регістрів (1,2 варіант). Регістри з паралельним входом, виходом (тип1) називаються регістрами пам’яті і використовуются, як прозорі тригери типу «затвор» та тригери з динамічним керуванням. На рис.16.8 приведена схема 8-ми розрядного паралельного регістру пам’яті, (виконан на 8-ми D-тригерах: схеми 7477, 7475) із загальним входом керування записом інформації і його умовне позначення. Високий рівень на вході C переписує інформацію з входу D на вихід Q ( ), низький рівень- зберігає дані за «затвором». Дані зберігаються або зчитуються з виходів

), низький рівень- зберігає дані за «затвором». Дані зберігаються або зчитуються з виходів  тригерів на наступному кроці виконання алгоритму-наприклад «додати до суматора зміст регистру А». Оберненний код даних в регистрі присутній по виходах

тригерів на наступному кроці виконання алгоритму-наприклад «додати до суматора зміст регистру А». Оберненний код даних в регистрі присутній по виходах  . До регистрів типу 2 відноситься 8-ми розрядний регістр, реалізований на схемі 74165 (3,4 варіант)..

. До регистрів типу 2 відноситься 8-ми розрядний регістр, реалізований на схемі 74165 (3,4 варіант)..

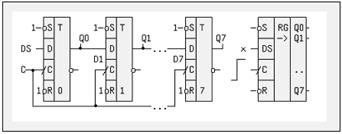

Аналіз послідовних регістрів (3,4 варіант). Такі регістри зсуву (рис.16.9, тип 3,4) виконуються на основі тригерів із динамічною синхронізацією (справедливо для регістрів з одним тактовим сигналом). У двотактних можна використати і прозорі регістри типу «затвор». Функція запису в n-розрядному регістрі зсуву на D-тригерах задається у вигляді умов:  .

.

Рис.16.9. Варіант послідовного регістру, тип 2: DS-вхід послідовного запису, R і S-входи попередньої установки.

Із приходом чергового позитивного фронту синхроімпульсу C, сигнал із входу i-го тригера через час tзт.п. з’явиться на його виході і піде на вхід наступного ( )-го тригера. Однак, на його вихід ця інформація не перепишеться, тому що тривалість активного фронту

)-го тригера. Однак, на його вихід ця інформація не перепишеться, тому що тривалість активного фронту  менше

менше  . На цьому процес зсуву даних на один розряд закінчиться до приходу наступного позитивного фронту тактового сигналу. Звідси зрозуміло, чому не можна використати тригери зі статичним керуванням. Щораз при

. На цьому процес зсуву даних на один розряд закінчиться до приходу наступного позитивного фронту тактового сигналу. Звідси зрозуміло, чому не можна використати тригери зі статичним керуванням. Щораз при  весь ланцюжок виявиться прозорим від входу DS до виходу Q7 і значення

весь ланцюжок виявиться прозорим від входу DS до виходу Q7 і значення  буде записано в усі тригери послідовного регістру. В умовних позначеннях регістрів зсуву напрямок стрілки, що вказує зсув, умовний. У різних довідниках її напрямок дається по-різному. Умовно приймається, що зсув робиться від молодшого розряду до старшого. Практичні схеми регістрів доповнюються схемами, що підключають до кожного тригера, які мають вхід паралельного запису Di, загальний вхід дозволу запису L і загальний асинхронний вхід скидання в 0 (R) всіх тригерів. Ці схеми підключаються до незадіяних входів Ri, Si тригерів. За подібною схемою виконан регистр 74164 (5,6 варіант). Уяву про універсальні регістри зсуву (тип 5) дає опис Generic 4-bit Universal Shift Register з БМ EWB ((7,8 варіант).

буде записано в усі тригери послідовного регістру. В умовних позначеннях регістрів зсуву напрямок стрілки, що вказує зсув, умовний. У різних довідниках її напрямок дається по-різному. Умовно приймається, що зсув робиться від молодшого розряду до старшого. Практичні схеми регістрів доповнюються схемами, що підключають до кожного тригера, які мають вхід паралельного запису Di, загальний вхід дозволу запису L і загальний асинхронний вхід скидання в 0 (R) всіх тригерів. Ці схеми підключаються до незадіяних входів Ri, Si тригерів. За подібною схемою виконан регистр 74164 (5,6 варіант). Уяву про універсальні регістри зсуву (тип 5) дає опис Generic 4-bit Universal Shift Register з БМ EWB ((7,8 варіант).

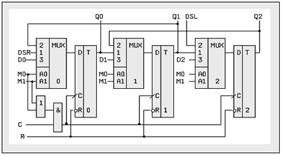

3.2.2 Реверсивний регістр зсуву даних. Зсув даних від розряду до розряду може робитися, як в одну сторону, так і в іншу. Одна з можливих схем реверсивного регістра зсуву на три розряди даних із двома послідовними інформаційними входами для зсуву інформації вліво DSL і вправо DSR, з паралельними входами запису  , входом синхроімпульсів C, входом R установки в 0 усіх тригерів і двома входами вибору режиму M1, M0, приведена на рис.16.10.

, входом синхроімпульсів C, входом R установки в 0 усіх тригерів і двома входами вибору режиму M1, M0, приведена на рис.16.10.

Рис. 16.10 Варіант реверсивного трирозрядного регістру зсуву (тип 5).

До D-входу будь-якого розряду, за винятком крайніх, підключені, через входи 1 і 2 мультиплексори, виходи лівого і правого сусідніх тригерів. Якщо  , а

, а  , то до входів D підключені перші входи мультиплексорів і інформація в кожний тригер, крім нульового, записується від лівого сусіда (відбувається зсув вправо). Вхід DSR служить, у цьому режимі, для послідовного введення інформації. Якщо

, то до входів D підключені перші входи мультиплексорів і інформація в кожний тригер, крім нульового, записується від лівого сусіда (відбувається зсув вправо). Вхід DSR служить, у цьому режимі, для послідовного введення інформації. Якщо  ,

,  , то до входів D підключені інші входи мультиплексів і інформація в кожний тригер, крім останнього, записується від правого сусіда, відбувається зсув вліво. Для послідовного введення даних у цьому режимі використовується вхід DSL. При

, то до входів D підключені інші входи мультиплексів і інформація в кожний тригер, крім останнього, записується від правого сусіда, відбувається зсув вліво. Для послідовного введення даних у цьому режимі використовується вхід DSL. При  робиться паралельний запис

робиться паралельний запис  позитивним фронтом тактового сигналу. Для зберігання інформації необхідно подати комбінацію

позитивним фронтом тактового сигналу. Для зберігання інформації необхідно подати комбінацію  . У цьому випадку до D-входів тригерів підключаться нульові входи мультиплексів (на схемі не показані). Щоб не відбулося несанкціонованого запису схеми 2АБО і 2І забороняє в цьому режимі (

. У цьому випадку до D-входів тригерів підключаться нульові входи мультиплексів (на схемі не показані). Щоб не відбулося несанкціонованого запису схеми 2АБО і 2І забороняє в цьому режимі ( ) проходження синхроімпульсів С. За такою схемою виконаний 8-розрядний регістр 1533ИР13.

) проходження синхроімпульсів С. За такою схемою виконаний 8-розрядний регістр 1533ИР13.

3.2.3 Счетчики. Счетчиком называют цифровое устройство (цифровой автомат), сигналы на выходе которого, в определенном коде, отображают число импульсов, поступивших на счетный вход. Кроме того, в счётчиках выполняются такие микрооперации, как установка в исходное состояние, хранение и выдача слов. По мере поступления входных сигналов счетчик последовательно меняет свои состояния, образованные комбинациями состояний триггеров со счетным входом. Число разрешенных состояний счетчика называют модулем счета, коэффициентом пересчета или емкостью M (в общем случае  , где n - число триггеров или двоичных разрядов счетчика). Счетчики классифицируют по значению модуля, направлению счета и способу организации межразрядных связей.

, где n - число триггеров или двоичных разрядов счетчика). Счетчики классифицируют по значению модуля, направлению счета и способу организации межразрядных связей.

По значению модуля счета различают: двоичные ( ), двоично-кодированные с произвольным модулем, с одинарным кодированием и др.

), двоично-кодированные с произвольным модулем, с одинарным кодированием и др.

По направлению счета: суммирующие (прямого счета - Up-counter), вычитающие (обратного счета - Down-counter) и реверсивные (Up-Down-counter).

По способу организации межразрядных связей различают счетчики с последовательным, параллельным и комбинированным переносами.

Кроме того, все перечисленные типы счетчиков принято делить на два вида: синхронные и асинхронные. При этом в асинхронных счетчиках изменение его состояния, вызванное воздействием очередного импульса, характеризуется последовательным во времени изменением состояний триггеров (как правило, это счетчики с последовательным переносом). В синхронных счетчиках смена состояний характеризуется одновременным во времени изменением состояний его триггеров. В этом качестве синхронные счетчики образуют один из видов синхронных автоматов, потому к ним может быть применена и стандартная методика синтеза этого класса автоматов.

Определим некоторые закономерности двоичных счётчиков. Соответствие между числом входных импульсов и состояниями 3-разрядного двоичного счетчика (прямой и обратный счет) представлено в табл.3.1. Рассматривая ее для прямого счета, можно отметить две закономерности:

1. Значение переменной Qi изменяется тогда, когда переменная в соседнем младшем разряде Qi- 1 переходит из состояния «1» в состояние «0».

Таблица 3.1

|

2. Значение выходной переменной Qi изменяется при поступлении очередного импульса сче-та в том случае, когда переменные во всех младших разрядах Qi- 1 ,…Q 1 находятся в состоянии «1».

Первая закономерность указывает на возможность реализации счетчика асинхронного типа, вторая позволяет построить синхронный счетчик. Для вычитающего счетчика аналогичные закономерности можно сформулировать так:

1. Значение выходной переменной Qi изменяется, когда переменная в соседнем младшем разряде Qi- 1 переходит из состояния «0» в «1».

2.Значение выходной переменной Qi изменяется при поступлении очередного импульса счета в случае, когда все переменные в предыдущих младших разрядах Qi- 1 ,...Q 1находятся в состоянии «0».

3.2.3.1 Асинхронные последовательные счетчики- строятся в виде цепочки триггеров со счетным входом (JK - триггер с J=K =1 или D - триггер с инверсной обратной связью,  ), когда тактовый вход каждого последующего подключен к выходу Q или

), когда тактовый вход каждого последующего подключен к выходу Q или  предыдущего, что зависит как от направления счета, так и от типа тактирующего входа триггера.Схема суммирующего счетчика на JK - триггерах и временная диаграмма его работы приведены на рис. 3.1. Если тактовые входы JK - триггеров соединить с инверсными выходами предыдущих триггеров, то получится схема вычитающего счетчика. Аналогично, если в схеме вычитающего счетчика на D - триггерах (рис. 3.2.) тактовые входы триггеров соединить с инверсными выходами предыдущих триггеров, то счетчик станет суммирующим.

предыдущего, что зависит как от направления счета, так и от типа тактирующего входа триггера.Схема суммирующего счетчика на JK - триггерах и временная диаграмма его работы приведены на рис. 3.1. Если тактовые входы JK - триггеров соединить с инверсными выходами предыдущих триггеров, то получится схема вычитающего счетчика. Аналогично, если в схеме вычитающего счетчика на D - триггерах (рис. 3.2.) тактовые входы триггеров соединить с инверсными выходами предыдущих триггеров, то счетчик станет суммирующим.

Полученные счетчики называют последовательными, так как в них каждый триггер переключается выходным сигналом предыдущего. Эти счетчики отличаются простой схемой, но низким быстродействием в режиме регистрации входных сигналов, так как в этом режиме нельзя подавать очередной входной сигнал, пока не зафиксировано предыдущее состояние счетчика. Время установления кода равно t уст = nt зд. тр, где t зд. тр - время задержки переключения триггера. Очевидно, что максимальная частота входных сигналов в режиме регистрации составляет f макс.рег=1/ t уст. Впрочем, в режиме деления входных импульсов максимальная частота их поступления будет ограничиваться быстродействием младшего триггера и составит f макс.дел=1/ t зд.тр.

а)

а)

|

б)

Рис. 3.1 Асинхронный суммирующий счетчик на JK- триггерах (а) и временная диаграмма его работы (б).

Рис..3. 2 Асинхронный вычитающий счетчик на D-триггерах- а, временная диаграмма его работы-б.

Второй недостаток состоит в том, что из-за накопления временных сдвигов в разрядах в процессе установления кода, в счетчике возникают на короткие промежутки времени ложные состояния. Поэтому если к выходным разрядам такого счетчика подключить дешифратор, то на его выходах могут появиться ложные сигналы, соответствующие промежуточным фазам перехода счетчика из одного состояния в другое. От названных недостатков свободны синхронные счетчики.

Синхронные двоичные счетчики

Рис. 3.3 Структурная схема синхронного счетчика

Схему синхронного счетчика можно представить обобщенной структурной схемой (рис. 3.3), включающей триггеры со счетным входом T и комбинационную схему, формирующую функции возбуждения fi для этих счетных входов. В JK - триггерах счетный вход организуется путем соединения входов J и K. Вход  управляет режимом работы схемы (

управляет режимом работы схемы ( - прямой счет,

- прямой счет,  - обратный счет), а выходной сигнал переноса/займа CR/BR (Carry/Borrow) может использоваться для наращивания разрядности счетчика.

- обратный счет), а выходной сигнал переноса/займа CR/BR (Carry/Borrow) может использоваться для наращивания разрядности счетчика.

Рис. 3.4 Двоичный счетчик с изменяемым направлением счета ( - прямой,

- прямой,  - обратный)

- обратный)

Как следует из анализа табл.3.1 (правило 2), переключение триггера младшего разряда осуществляется с приходом счетного сигнала CLK, а остальных триггеров-только в том случае, когда все триггеры младших разрядов установлены в «1» (прямой счет) или в «0» (обратный счет).

Следовательно, в общем случае, функция возбуждения триггера fi для синхронного двоичного счетчика может быть определена выражением:  ,

,  (1)

(1)

Для младшего разряда: f 1=1.Сигнал переноса/заёма может формироваться в двух случаях, а именно, когда в счетчике хранится максимальное значение кода  при

при  и минимальное значение

и минимальное значение  при

при  :

:  . (2)

. (2)

Рис. 3.5 Диаграмма формирования переноса и займа в 4-разрядном синхронном счетчике (CE =1)

На рис. 3.4 представлена схема 4-разрядного синхронного двоичного счетчика с изменяемым направлением счета, построенного в соответствии с выражениями (1) и (2) с тем отличием, что в схему введен дополнительный управляющий вход CE (Count Enable - разрешение счета). Временные диаграммы работы счетчика (рис. 3.5) поясняют особенности формирования переноса в режиме прямого счета и заёма - в обратном с учетом запаздывания в их формировании относительно счетного (тактового) сигнала CLK.

Каскадировать счетные группы можно двумя способами: с использованием последовательного или параллельного переносов. При параллельном переносе (рис. 3.6) две счетные группы как бы объединяются в единую синхронную схему 8- разрядного счетчика. Наличие управляющего входа разрешения счета CE при таком способе объединения является просто обязательным. Иногда, когда высокая скорость не требуется, счетные группы можно соединить последовательно (рис. 3.7), при этом сигнал переноса (заёма) служит тактовым сигналом следующей старшей группы. В этом случае (см. диаграммы рис. 3.5) вместо выхода  целесообразно использовать тот же сигнал, только синхронизированный тактовым сигналом (CR/BR). Схему же счетчика при этом можно упростить, убрав вход разрешения счета CE.

целесообразно использовать тот же сигнал, только синхронизированный тактовым сигналом (CR/BR). Схему же счетчика при этом можно упростить, убрав вход разрешения счета CE.

Рис. 3.6 Каскадирование синхронных счетчиков с параллельным переносом

Рис. 3.7 Каскадирование синхронных счетчиков с помощью последовательного переноса

3.5. Синтез счетчиков с произвольным модулем. Различные области применения требуют использования счетчиков с разными модулями (например, в качестве делителей частоты импульсной последовательности используются счётчики с M< 2 n ), для работы в 10-ой системе счисления применяются декадные счетчики с M =10) и т. д.

Существующие методы построения счетчиков с произвольным модулем счета очень разнообразны и сводятся по существу к различным подходам в устранении избыточных состояний  , где 2 n -модуль счета n - разрядного двоичного счетчика [Л. 2...4, 8]. В лабораторной работе используются лишь два способа:

, где 2 n -модуль счета n - разрядного двоичного счетчика [Л. 2...4, 8]. В лабораторной работе используются лишь два способа:

-классический метод синтеза счетчика с произвольным модулем M, рассматривающий поведение счетчика как синхронного автомата с заданной таблицей переходов;

-метод исключения группы избыточных состояний.

Классический метод. Кратко перечислим основные этапы синтеза.

1. На основе заданного значения модуля M определяем число триггеров n, округлив до ближайшего большего целого величину  .

.

2. Выбираем (если он не является заданным) тип триггера, в котором имеется или легко реализуется счетный режим.

3. Выбираем естественный порядок счета, начиная с 0 (в диапазоне 0...M-1), или с α (в диапазоне от  до 2 n -1) и составляем таблицу переходов счетчика по форме табл. 3.2 (выбран JK - триггер и M =5).

до 2 n -1) и составляем таблицу переходов счетчика по форме табл. 3.2 (выбран JK - триггер и M =5).

Таблица 3.2

| Состояния счетчика | Функции возбуждения триггеров | ||||||||||

| Исходное (t) | Следующее (t+1) | ||||||||||

| Q 3 | Q 2 | Q 1 | Q 3 | Q 2 | Q 1 | J 3 | K 3 | J 2 | K 2 | J 1 | K 1 |

| * | * | * | |||||||||

| * | * | * | |||||||||

| * | * | * | |||||||||

| * | * | * | |||||||||

| * | * | * |

4. Составляем карты Карно для каждой из функций возбуждения  от аргументов

от аргументов  и находим соответствующие минимальные формы:

и находим соответствующие минимальные формы:

J3=Q2Q1, J2=Q1, J1 =  ,

,

K3=1, K2=Q1, K1=1.

5. На основе известных выражений для функций возбуждения строим схему синхронного счетчика с заданным модулем.

Метод исключения. Использование метода предполагает знание выражения для функции возбуждения счётного входа i -го разряда счётчика (1). Изложение метода проведём на конкретном примере синтеза суммирующего счётчика, для которого выражение (1) при  примет вид

примет вид  ,

,  . (3)

. (3)

Для младшего i =1 разряда f1= 1. Значение модуля счёта M=6. В качестве триггера, Т-триггер.

1. На основе заданного значения модуля M определяем число триггеров n, округлив до ближайшего большего целого величину  , т. е. n =3.

, т. е. n =3.

2. Составляется таблица состояний счётчика по модулю 2n

3. Исключается из таблицы группа избыточных состояний с выделением в таблице следующих кодовых комбинаций (наборов): A, B, C. При этом: А – состояние предшествующее группе избыточных состояний, В – первое в группе избыточных состояний, а С – следующее за группой избыточных состояний.

| Состояния счётчика –––––––– Q3 Q2 Q1 –––––––– 0 0 0 C 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 A ––––––– 1 1 0 B 1 1 1 |

4. Выполняется функция коррекции поразрядных функций возбуждения fi (i =1, 2, 3) по следующим правилам

а) Если i - ые разряды для состояний В и С совпадают, то коррекция не требуется:Qi(B) = Qi(C), тогда fi*= fi..

Здесь fi* - откорректированное значение поразрядной функции возбуждения. В данном примере f 1 *= f 1=1. (4)

Здесь fi* - откорректированное значение поразрядной функции возбуждения. В данном примере f 1 *= f 1=1. (4)

Если i - ые разряды для состояний В и С не совпадают, то коррекция производится по правилам.

б) Qi(А) ≠ Qi(C) - имеет место переключение состояния триггера для вновь установленных смежных состояний. Тогда fi*= fi V φА, где функция φА = 0 для всех наборов, за исключением набора А, для которого φА = 1. Следовательно, и fi* =1, что обеспечит переключение триггера i- го разряда при переходе с набора состояний А к В.

в) Qi(А) = Qi(C) – отсутствует переключение состояния триггера для вновь установленных смежных состояний. Тогда fi*=  , в этом случае значение поразрядной функции возбуждения fi*= 0 будет блокировать переключение триггера i- го разряда при переходе с набора состояний А к В.

, в этом случае значение поразрядной функции возбуждения fi*= 0 будет блокировать переключение триггера i- го разряда при переходе с набора состояний А к В.

Поскольку избыточные состояния исключены из состояний счётчика, то выражение для функции φА можно минимизировать с учётом этих избыточных состояний. В этом случае, как это нетрудно получить, будем иметь φА = Q 3 Q 1. В рассматриваемом примере синтеза счётчика имеет место коррекция как по правилу (4, б): f3*=f3 V φА=Q 1 Q 2 V Q 3 Q 1, (5)

Поскольку избыточные состояния исключены из состояний счётчика, то выражение для функции φА можно минимизировать с учётом этих избыточных состояний. В этом случае, как это нетрудно получить, будем иметь φА = Q 3 Q 1. В рассматриваемом примере синтеза счётчика имеет место коррекция как по правилу (4, б): f3*=f3 V φА=Q 1 Q 2 V Q 3 Q 1, (5)

так и по правилу (4, с): f2*=  = Q 1*

= Q 1*  =

=  (6)

(6)

В выражениях (5) и (6) f2=Q 1и f3= Q 1 Q 2 представляют поразрядные функции возбуждения для 2 го и 3-го разрядов соответственно.На рис 3.8 изображена схема счётчика, построенная в соответст

|

вии с выражениями (4) - (6).

Индивидуальные задания для синтеза синхронных счетчиков с произвольным модулем сведены в табл. 3.3.

Таблица 3.3

| № варианта | Модуль M | Порядок счета | Тип триггера | Метод синтеза |

| 0...М-1 | JK | Классический или исключение избыточных состояний (α равно 1 или 2 в зависимости от нечетнго/ четного варианта 1-8) | ||

| α...2n | D | |||

| 0...М-1 | ||||

| α...М-1 | Т |

2017-11-01

2017-11-01 1124

1124