Задание 1. Собрать схему шифратора, приведеннуцю на рис. 6.1, с помощью которого сигнал, поступающий в результате нажатой на пульте управления кнопки, соответствующей значению в диапазоне от 1 до 9, превращается в двоичный код. В схеме использовать макрос "SH" (рис. 6.2).

В зависимости от номера в журнале реализовать преобразования сигналов и формирование двоичного кода в результате поочередного нажатия заданных двух кнопок на пульте в соответствии с нижеприведенными вариантами. Проанализировать полученные результаты.

| 1 вариант – 2, 5 2 вариант – 3, 8 3 вариант – 5, 7 4 вариант – 4, 6 5 вариант – 2, 9 6 вариант – 1, 4 7 вариант – 7, 8 | 8 вариант – 2, 9 9 вариант – 6, 8 10 вариант – 1, 7 11 вариант – 2, 4 12 вариант – 6, 7 13 вариант – 5, 6 14 вариант – 2, 5 | 15 вариант – 1, 3 16 вариант – 3, 6 17 вариант – 7, 9 18 вариант – 5, 1 19 вариант – 7, 3 20 вариант – 9, 5 |

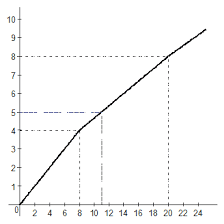

Рисунок 6.1 – Схема шифратора для пульта управления

Рисунок 6.2 – Внутренняя структура макроса «SH»

Задание 2. Собрать в EWB дешифратор (рис. 6.3). В зависимости от номера в журнале, реализовать преобразование заданного кода сигнал на одном из его выходов в соответствии со следующими вариантами.

| 1, 2 варианты – 01, 10 3, 4 варианты – 10, 11 5, 6 варианты – 00, 10 7, 8 варианты – 01, 11 9, 10 варианты – 00, 11 | 11, 12 варианты – 10, 00 13, 14 варианты – 11, 01 15, 16 варианты – 01, 00 17, 18 варианты – 00, 11 19, 20 варианты – 10, 00 |

Рисунок 6.3 – Схема дешифратора в EWB

Задание 3. Исследование дешифратора в статическом режиме.

Собрать схему, которая представлена на рис.6.4. Создать в пакете EWB «макрос» для этой схемы с именем ”PS”.

Рисунок 6.4 – Схема дешифратора А

Собрать схему, которая представлена на рисунке 6.5. Создать в пакете EWB «макрос» для этой схемы с именем ”VS”.

Рисунок 6.5 – Схема дешифратора B

Собрать схему, представленную на рисунке 6.6.

Рисунок 6.6 – Подключение составного дещифратора

Согласно логическим выражениям составить таблицу состояний (ТС). Занести эту ТС в генератор слов и исследовать работу дешифратора (привести временную диаграмму).

Задание 4. Исследование дешифратора в динамическом режиме.

Собрать схему, представленную на рисунке 6.7:

Рисунок 6.7 – Подключение дешифратора в динамическом режиме

С помощью ГИ, ГС, ЛА, осциллографа выполнить следующие действия: подать на вход Х1 сигнал прямоугольной формы со следующими параметрами: Amplitude = 4V, Duty Cycle = 50, Frequency =10 kHz. С входа YN снять осциллограммы (N-порядковый номер студента или бригады).

Вопросы для самоконтроля

1. Какие устройства называют шифраторами?

2. Объясните принцип работы шифратора.

3. С помощью чего можно построить шифратор?

4. Приведите примеры применения шифратора.

5. Какие устройства называют дешифраторами?

6. Чем определяется число линейных дешифраторов у первой ступени прямоугольного дешифратора?

7. Укажите расхождения между полным и не полным дешифратором.

8. Докажите что на выходах элементов ИЛИ-НЕ первой ступени дешифратора получаются конъюнкции от сигналов на их входах.

9. В каких прямоугольных дешифраторах выходы инверсные, а у каких - прямые?

10. Укажите различия между дешифраторами с прямыми и инверсными выходами.

11. Запишите таблицу истинности полного дешифратора с заданной преподавателем разрядностью входных кодов.

12. Чем определяется число каскадов прямоугольного дешифратора?

13. Как сказывается увеличение числа каскадов дешифратора на его быстродействие?

14. Нарисуйте условное графическое изображение исследуемого в данной работе прямоугольного дешифратора.

15. Приведите методику выявления и локализации неисправности дешифратора.

16. Нарисуйте схему полного дешифратора, заданного преподавателем типа и разрядностью входных кодов.

17. Сравните дешифраторы различных типов по быстродействию.

18. Сравните дешифраторы различных типов по аппаратурным задержкам.

19. Достоинства и недостатки типа дешифратора, указанного преподавателем.

20. Как построить дешифратор кодов большой разрядности (разрядность задается преподавателем) на базе дешифраторов кодов меньшей разрядности (двухразрядних), изготовленных в виде интегральных схем.

21. Сформулировать функции, обратные по отношеню к функциям дешифратора.

22. Привести аналитические функции преобразования сигналов дешифратором.

23. Нарисуйте временные диаграммы заданного преподавателем дешифратора.

24. Чем определяется нагрузочная способность заданного преподавателем дешифратора.

Лабораторная работа 7

ФОРМИРОВАНИЕ И ГЕНЕРИРОВАНИЕ

ЦИФРОВЫХ СИГНАЛОВ

Цель занятия

Ознакомление с принципами построения и функционирования схем временной задержки, формирования и генерирования цифровых сигналов.

2018-03-09

2018-03-09 196

196