Различают алгоритмы арифметических и логических типов формирования дополнительных кодов. Алгоритмы первого типа требуют для реализации последовательностных цифровых схем, т.е. схем с элементами памяти. При этом для получения дополнительного n- разрядного двоичного кода до 2n необходимо выполнить инверсию этого кода и суммировать с единицей младшего разряда.

Подобные алгоритмы реализуют на параллельных регистрах в универсальных обработчиках информации. Альтернативой подобных алгоритмов для КЛС может служить алгоритм, синтезируемый с использованием следующей таблицы истинности:

| 10 эквив. | Двоичный код | Дополнительный код | 10 эквив. | ||||||

| В4 | В3 | В2 | В1 | D4 | D3 | D2 | D1 | ||

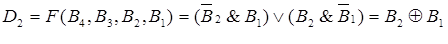

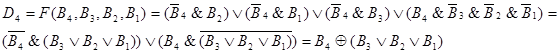

Синтез преобразователя двоичных кодов в дополнительный на базе КЛС выполним начиная с младшего разряда, для этого составим матицу Карно для функции D1=F(B4, B3, B2,B1).

| В4, В3 | ||||||||

| 00 01 11 10 | ||||||||

| В2,B1 | ||||||||

D1=B1

| В4, В3 | ||||||||

| 00 01 11 10 | ||||||||

| В2,B1 | ||||||||

| В4, В3 | |||||||||

| 00 01 11 10 00 | |||||||||

| В2,B1 | |||||||||

| В4, В3 | ||||||||

| 00 01 11 10 | ||||||||

| B2,B1 | ||||||||

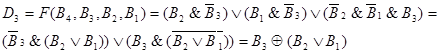

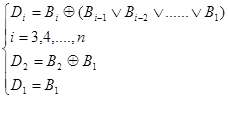

Логический алгоритм синтеза устройства для формирования n–разрядного дополнительного кода может быть представлен для любого разряда выражением вида:

Дополнив его выражениями для D1, D2, получим замкнутый алгоритм для получения дополнительного кода.

2014-02-02

2014-02-02 428

428