Endmodule

Else if(en)

Begin

Process(CLOCK, D, IQ)

Begin

Architecture na_vhdl_arch of na_vhdl is

Entity na_vhdl is

port (CLOCK, D: in STD_LOGIC;

Q: out STD_LOGIC_VECTOR(4 downto 0));

end na_vhdl;

signal IQ: STD_LOGIC_VECTOR(4 downto 0);

if (CLOCK'event and CLOCK='1') then

IQ <= D & IQ(4 downto 1);

end if;

Q <= IQ;

end process;

end na_vhdl_arch;

б) описание сдвигового регистра на языке VHDL

module Verilog (en, clock, reset, out);

parameter Width = 8;

input clock, reset, en;

output [Width-1:0] out;

reg [Width-1:0] out;

always @(posedge clock or negedge reset)

if(!reset)

out = 8'b0;

out =out +1;

в) описание сдвигового регистра на языке Verilog

Высокоуровневые языки описания аппаратуры позволяют при описании электронных компонентов задавать уровень абстракций (сокрытия деталей) – от функционального до полностью вентильного описания.

Использование различных уровней абстракции подобно использованию различных языков программирования для процессоров: если надо написать программу, отвечающую требованию очень короткого времени исполнения, то используют Ассемблер. Если же надо написать очень сложную программу, используют, например, языковую среду Delphi.

С помощью технологии описания аппаратуры возможно на программном уровне разрабатывать и синтезировать аппаратные проекты в широком диапазоне (от простых комбинационных схем до микропроцессорных систем).

Использование программного обеспечения для синтеза позволяет проектировщику устраниться от непосредственного участия в процессах трансляции и минимизации HDL-кода, а также от проверки соответствия временным ограничениям.

Существуют несколько различных видов синтеза:

1. Логический синтез: трансляция (и минимизация) булевых функций в вентильную схему.

2. RTL-синтез: трансляция в схему, содержащую не только вентили, но и триггеры и представляющую собой цифровой автомат.

3. Синтез на поведенческом уровне: может использовать один и тот же схемный компонент для более чем одной последовательной конструкции языка.

Обобщая, можно отметить, что процесс синтеза можно сравнить с компиляцией: HDL-код транслируется в принципиальную схему.

Среди систем автоматизированного проектирования и моделирования на основе языков описания аппаратуры известны следующие: Foundation Series (фирмы Xilinx, Aldec, Synopsys), Model Sim (фирмa Model Technology), StateCad (фирмa Visual Software Solutions), MAX+Plus II (фирмa Altera), IDS (фирмa Atmel), VHDL Simili (фирмa Symphony EDA) и другие.

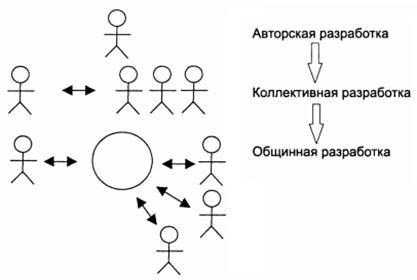

Все множество разработок в зависимости от количества участников и типов взаимоотношений между ними может быть сведено к триаде разработок:

2014-02-18

2014-02-18 1031

1031