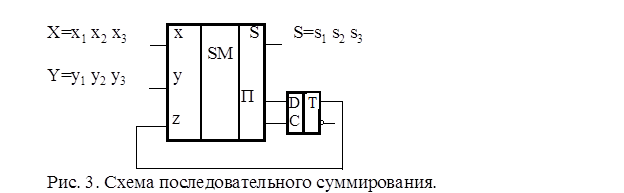

Сумматор – устройство, предназначенное для выполнения арифметического сложения чисел в двоичном коде. Простейший случай - это суммирование двух одноразрядных чисел.

Tc(посл) @ n  t,

t,  t-время задержки сигнала переноса на элементе задержки.

t-время задержки сигнала переноса на элементе задержки.

В этой схеме на входы x и y последовательно подаются попарно разряды слагаемых xi и yi. На выходе S формируются si разряды суммы. Триггер введен в схему для хранения значения переноса до следующего такта (следующей пары разрядов).

Параллельный сумматор.

старший разряд младший разряд

xn SM S x2 SM S x1 SM S

xn SM S x2 SM S x1 SM S

. ..

yn y2 y1

yn y2 y1

P P P

P P P

| |||

|

Рис. 4. Схема параллельного суммирования.

Рис. 4. Схема параллельного суммирования.

Тс(пар) @ ntлэ ,

Очевидно, Tc(посл) ≤ Тс(пар), так как

t @ (3,6) ktлэ,

t @ (3,6) ktлэ,

где k - коэффициент запаса, обеспечивающий полное окончание всех переходных процессов в сумматоре последовательного действия k Î [1,2, 1,3].

Недостатком такого параллельного суммирования является большое время распространения сигналов переноса Pi. Параллельные безрегистровые сумматоры обеспечивают наибольшую скорость суммирования, если снабжены схемой ускоренного переноса.

2015-04-01

2015-04-01 932

932