Архитектура

− SPARC архитектура версии V8;

− 8 регистровых окон и 8 глобальных регистров.

Целочисленные устройства

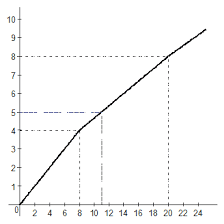

− 5-ти стадийный конвейер;

− 1-тактные целочисленные операции;

− 2-тактный LOAD из КЭШ данных первого уровня;

− 7-тактный LOAD из КЭШ данных второго уровня.

Подсистема памяти

− КЭШ данных первого уровня:

16К байт, 4-х колоночный, строка – 32 байта, сквозная запись, буфер записи – 16 байт;

− КЭШ команд:

8К байт, 2-х колоночный, строка – 32 байта;

− таблица преобразования виртуальных адресов в физические (TLB):

32-х входовая, полностью ассоциативная, аппаратный поиск по таблице страниц в памяти;

− поддержка когерентности КЭШей для многопроцессорных конфигураций.

Внешний интерфейс

− 64-х разрядная MBUS шина;

− 64-х разрядная шина внешнего КЭШа;

− JTAG –интерфейс для начальной отладки.

Тактовая частота – 150 МГц

Производительность – 140 MIPS, 60 MFLOPS

Количество транзисторов – 2,8 млн.

Технология – 0,35 мкм.

Площадь кристалла – 10мм х 10мм

Рассеиваемая мощность – 3,5 ВТ

Напряжение питания – 3,3 В

Корпус – BGA, 480 выводов

2015-05-13

2015-05-13 321

321