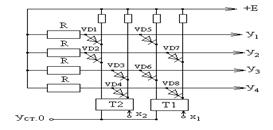

Схема дешифратора на діодній матриці.

У схемі 2 входи та 4 виходи. Діодна матриця виконує функції 4-х елементів І а два тригера Т1 та Т2, виконують функції елементів НІ.

Мал. 146. Схема дешифратора

на діодній матриці.

Якщо х1=0 та х2=0 (код 00), то обидва тригера в 0. У початковому положенні ліві входи тригерів мають високий рівень напруги (заперечування вхідного сигналу), а праві виходи - нульові. Тому VD1,2,5,6 заперті, а інші відчинені. Якщо хоч би один діод, приєднаний до якої небудь вхідної шини, відкритий, то потенціал цієї шини низький, так як практично вся напруга джерела +Е при протіканні струму через резистор R та відкритий діод падає на резисторі, опір якого значно більше опору діода в прямому напрямі. Через це високий потенціал, відповідаючи коду 1, виникає тільки на шині у1, до якої під’єднані одночасно закриті діоди VD1 та VD5. Таким чином, У1=1; У2=У3=У4=0.

Якщо на вхід дешифратора з регістра поступає двійковий код 11, то високі рівні напруги будуть на правих тригерах та закритими стають діоди VD3, VD4, VD7, VD8. В цьому випадку У4=1; У1=У2=У3=0. При коді 10 високий рівень напруги передається на шину У3, а при коді 01 - на шину У2.

При К входах будемо мати m=2k вихідних шин.

При великій кількості шин використовують багатоступінчасті дешифратори.

Є діодні, діодно-транзисторні та транзисторні дешифратори.

Трьохрозрядний дешифратор К223ИД1, К500И161М. К229И1-чотирьохвхідний двоступінчастий дешифратор.

Мультиплексери. Мультиплексором називається функціональний вузол, що забезпечує передачу інформації, що надходить по декільком вхідним лініям зв'язку, на одну вихідну лінію.

Вибори тієї або іншої вхідної лінії Ai здійснюється відповідно до адресного коду, що надходить, S0… S1...

При наявності n адресних входів можна реалізувати M=2n комбінацій адресних команд, кожна з який забезпечує вибір однієї з М вхідних ліній.

Мал. 148. Блок-схема мультиплексера.

Частіше усього використовують мультиплексери “із 4 у 1” (М=4; n=2). “із 8 у 1” (М=8; n=3). “із 16 у 1” (М=16; n=4).

Якщо припустити наявність надлишкових комбінацій адресних сигналів, то можна спроектувати мультиплексери з будь-яким числом вхідних ліній M£2n.

Табл. Істинність мультиплексера “із 4 у 1”.

| S0 | S1 | F |

| A0 | ||

| A1 | ||

| A2 | ||

| A3 |

Основа операції при виконанні арифметичних дій у сучасних цифрових системах є додавання.Тому основним блоком операційних устроїв звичайно є суматор.

Підсумовування багаторозрядных чисел провадитися шляхом їхнього поразрядного додавання з переносом між розрядами.

Вирахування - це підсумовування в оберненому при додатковому ході.

2014-02-02

2014-02-02 275

275