Основой для построения современной вычислительной техники являются цифровые интегральные схемы (ЦИС), сложность которых принято характеризовать степенью интеграции Kи.

Kи = lg Nэл,, (2.1)

где Nэл - число элементов И-НЕ либо ИЛИ-НЕ, расположенных на кристалле микросхемы.

По степени интеграции микросхемы подразделяют на:

- малые интегральные схемы (МИС) - это схемы 1...2 степени интеграции, содержащие от нескольких до 100 элементов, в состав которых входит один или несколько логических элементов И, ИЛИ, НЕ, триггеров и т.п.;

- средние интегральные схемы (CИС) - схемы 2...3 степени интеграции, содержащие от нескольких десятков до 1000 элементов, в состав которых входят один или несколько функциональных узлов типа регистр, счетчик, дешифратор и т.п.;

- большие интегральные схемы (БИС) - это схемы 3...4 степени интеграции, содержащие от нескольких сотен до 10000 элементов, в состав которых входит одно или несколько функциональных устройств (например, арифметико-логическое устройство, оперативное запоминающее устройство, программируемая логическая матрица и др.);

|

|

|

- сверхбольшие интегральные схемы (СБИС) - схемы 5...7 степени интеграции, представляющие собой законченные микроэлектронные изделия, способные выполнять функции аппаратуры.

По способу представления информации ИС делятся на потенциальные и импульсные. В потенциальных ИС значения “0” и “1” представляются двумя существенно различающимися уровнями электрического сигнала: высоким и низким. Чаще всего низкий потенциал принимают за “0” и обозначают U0 (UL), а высокий потенциал принимают за “1” и обозначают U1 (UH). Такое представление называется положительной логикой. При использовании отрицательной логики за “0” принимают высокий потенциал, за “0” - низкий потенциал.

В импульсных ЦИС одно из значений логического сигнала определяется наличием на выходе схемы импульсов определенной длительности и амплитуды, а другое значение - отсутствием импульсов. В положительной логике отсутствие импульсов соответствует “0”, а наличие - “1”.

Большинство типов современных ИС относится к классу потенциальных. Для характеристики потенциальных микросхем используется следующая система параметров:

- выходные напряжения низкого и высокого уровня (UOL, UOH) при заданных токах нагрузки;

- входные токи низкого и высокого уровня (IIL, IIH);

- порог переключения UTH;

- абсолютная помехоустойчивость по отношению к помехам положительной полярности UП+ и отрицательной полярности UП- -;

- мощность РCC или ток ICC, потребляемые от источника питания;

- времена задержек распространения сигнала от входа до выхода

при изменении сигнала на выходе из “0” в “1” (tPLH) и из “1” в “0” (tPHL);

|

|

|

- времена подготовки (tSU) и удержания (th) входных сигналов относительно тактовых сигналов.

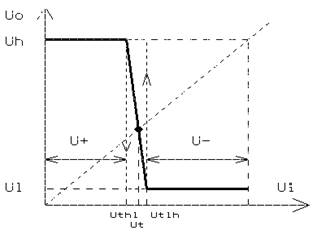

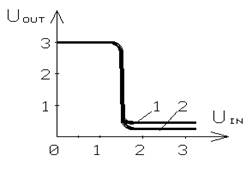

Параметры цифровых схем определяются по их статическим и переходным характеристикам. Основной статической характеристикой ИС является передаточная характеристика UO = f (UI). По типу передаточной характеристики различают инвертирующие и неинвертирующие ЦИС. Типичная передаточная характеристика инвертирующего логического элемента представлена нарис.2.1.

На передаточной характеристике можно выделить три ярко выраженных участка: I - соответствует состоянию Uвых=UL; II - соответствует состоянию Uвых=UH, III - промежуточному состоянию или зона неопределенности.

Максимально допустимая величина потенциальной помехи, не вызывающая логического переключения или сбоя, называется помехоустойчивость и определяется выражениями (2.2), (2.3).

UП+ = UП0 - U0, (2.2)

UП-- = U1 - UП1, (2.3)

где UП0, UП1 - порог переключения при изменении выходного напряжения из “ 1” в “0 ” и из “0 ” в “ 1” соответственно.

Рисунок 2.1 Типовая передаточная характеристика инвертирующего логического элемента

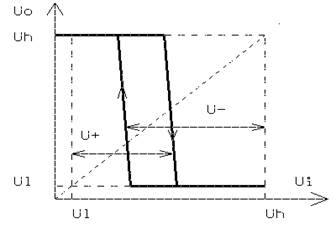

Эффективным средством повышения помехоустойчивости является получение гистерезиса на передаточной характеристике (рис.2.2).

Рисунок 2.2. Передаточная характеристика логического элемента с гистерезисом.

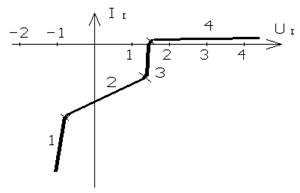

Входная характеристика логических схем II = f(UI) служит для определения значений входных токов IIL и IIH. Выходные характеристики UOL = f(IOL), UOH = f(IOL) позволяют определить зависимость выходных напряжений низкого и высокого уровней от токов нагрузки.

Ток потребления, соответственно и мощность потребления, зависят от логического состояния микросхемы (особенно для МИС и СИС) и частоты переключения. Поэтому различают статическую мощность потребления, которая определяется согласно выражению:

P = 0,5 VCC (I0СС + I1СС), (2.4)

где I0СС - ток потребления при Uвых = UL, I1СС - ток потребления при Uвых = UH, и динамическую мощность потребления, которая является функцией частоты переключения логического элемента.

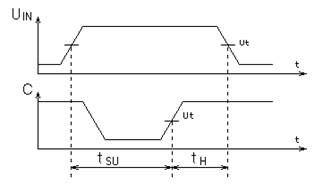

Задержки распространения сигналов от входов до выходов микросхемы характеризуют их быстродействие и определяются с помощью переходных характеристик, которые приведены нарис.2.3.

Времена задержек распространения сигналов определяются, как промежутки времени между моментами достижения входными и выходными потенциалами порога переключения. Значения tP существенно зависят от емкости нагрузки. Для характеристики быстродействия очень часто используют величину средней задержки равной:

tP = 0,5 (tPHL + tPLH). (2.5)

Рисунок 2.3. Переходные характеристики логических элементов

В ЦИС, содержащих элементы памяти, на подачу некоторых входных сигналов накладываются определенные временные ограничения, которые принято характеризовать временами подготовки (tSU) и удержания (th). Время подготовки - это интервал до поступления тактового сигнала, в течение которого информационный сигнал должен оставаться неизменным. Время удержания - это время после поступления тактового сигнала, в течение которого информационный сигнал не должен изменяться. Необходимые времена подготовки и удержания обеспечивают правильное восприятие элементом памяти подаваемой на него входной информации. На рис. 2.4 в качестве примера показаны времена подготовки и удержания относительно положительного фронта тактового сигнала.

Рисунок 2.4. Времена подготовки и удержания логических элементов с памятью

Понятия подготовки и удержания применимы не только к сигналам синхронизации и информационному, но распространяются и на процессы взаимодействия двух и более информационных сигналов.

Рассмотренная система параметров ЦИС полностью характеризует их электрические характеристики и, как правило, в той или иной мере указывается в справочной литературе.

|

|

|

^ ЛЕКЦИЯ 3. МИКРОСХЕМЫ ТИПА ТТЛ, ЭСЛ, КМОП

Все, выпускаемые в настоящее время, стандартные ЦИС малой и средней степени интеграции изготавливаются на основе биполярных или МОП транзисторов. По схемотехническому и конструктивно-технологическому исполнению биполярные микросхемы подразделяют на типы: транзисторно - транзисторные логические ИС (ТТЛ) и их модификации (ТТЛ с диодами Шоттки, Шоттки транзисторная логика и др.); эмиттерно-связанные логические ИС (ЭСЛ). ЦИС на МОП транзисторах подразделяются на:

p - канальные (p-МОП);

n - канальные (n-МОП);

комплементарные на взаимодополняющих n- и p-канальных транзисторах (КМОП).

^ Микросхемы ТТЛ являются основой для построения аппаратуры среднего и высокого быстродействия и в настоящее время получили наибольшее распространение.

Электрическая схема базового элемента ТТЛ со сложным инвертором приведена на рис.3.1.

Рисунок 3.1 Электрическая схема элемента ТТЛ.

Резистор R1 и транзистор VT1 реализуют логическую функцию И, транзистор VT2 с резистором R2 и цепочкой, образованной транзистором VT5 и резисторами R3 и R4, выполняют роль фазорасщепляющего каскада для выходного буферного каскада, построенного на транзисторах VT3...VT6. Резистор R5 предназначен для рассасывания объемного заряда из базы транзистора VT4 при выключении инвертора, а резистор R6 - ограничивает “сквозные” токи, протекающие в схеме при ее переключении. Диоды VD1 и VD2 - антизвонные и предназначены для ограничения амплитуды отрицательных выбросов на входах микросхемы, что позволяет предотвратить ее ложные срабатывания.

Входная характеристика базового элемента ТТЛ приведена на рис.3.2, а его передаточная характеристика - на рис. 3.3.

Рисунок 3.2. Входная характеристика ТТЛ- элемента.

Рисунок 3.3. Передаточная характеристика ТТЛ элемента.

На входной характеристике ТТЛ элемента можно выделить четыре участка: участок 1 определяется антизвонным диодом и характеризует способность микросхемы ограничивать выбросы отрицательной полярности; участок 2 представляет собой прямую линию, наклон которой может быть определен согласно выражению 3.1.

|

|

|

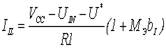

, (3.1)

, (3.1)

где VCC - напряжение питания; UIN - входное напряжение; U* - прямое падение напряжения на переходе база - эмиттер многоэмиттерного транзистора; MЭ - количество эмиттеров, на которые подано напряжение высокого уровня; bI - инверсный коэффициент усиления транзистора VT1.

Участок 3 соответствует моменту переключения тока базы МЭТ из эмиттера в коллектор и определяет напряжение порога переключения (UTH). Участок 4 входной характеристики определяет входной ток высокого уровня IIH, который может быть определен по формуле (3.2)

IIN = bIIR1, (3.2)

где  (3.3)

(3.3)

UIN - входное напряжение низкого уровня, поданное на остальные эмиттеры.

На передаточной характеристика условно показано выходное напряжение низкого уровня (UOL) для двух случаев: коэффициент разветвления Краз = 10 (участок 1) и Краз = 1 (участок 2). В общем случае выходное напряжение низкого уровня может быть определено по формуле 3.4, напряжение высокого уровня - в соответствии с выражением 3.5.

UOL = U0 + (rc + 4 mfT / bNI6) IL, (3.4)

UOH = Vcc - (R2 /(1 + bN)) IL - 2 U*, (3.5)

где bN - нормальный коэффициент усиления транзисторов VT3, VT4, включенных по схеме Дарлингтона; rc - объемное сопротивление тела коллектора транзистора VT6; mfT / bNI6 - динамическое сопротивление коллектор-эмиттер транзистора VT6 в режиме насыщения; I6 - ток базы транзистора VT6; IL - ток нагрузки.

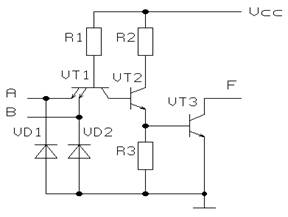

В настоящее время микросхемы ТТЛ выпускаются только с диодами Шоттки, использование которых позволяет существенно повысить быстродействие ЦИС при одновременном снижении потребляемой мощности. Имеется множество модификаций ТТЛ элементов, наибольший интерес среди которых представляют буферы с тремя состояниями и с открытым коллектором. Вентили с тремя состояниями (рис.3.4) являются основой для построения двунаправленных приемопередатчиков, широко используемых при проектировании микропроцессорных систем. Если на вход EZ подан высокий уровень напряжения, то буфер с тремя состояниями инвертирует информацию, поступающую на вход А. Если же на входе EZ низкий уровень напряжения, то выходные транзисторы VT4 и VT6 закрыты, что соответствует высокоимпедансному или третьему состоянию.

Электрическая схема логического элемента ТТЛ типа с открытым коллектором приведена на рис.3.5, важной особенностью которых является то, что они позволяют реализовывать логическую функцию “Монтажное И” и работать на нестандартную нагрузку.

Рисунок 3.4. Электрическая схема буфера с тремя состояниями

Рисунок 3.5. Электрическая схема вентиля с открытым коллектором

Работа этого элемента ничем не отличается от функционирования базового элемента за исключением того, что к коллектору выходного транзистора необходимо подключать сопротивление нагрузки, второй вывод которого подсоединен к положительному выводу источника питания.

При проектировании аппаратуры на элементах ТТЛ возникают вопросы, связанные с передачей сигналов между блоками и внутри них, режимом неиспользуемых входов и т.д. Существуют общие рекомендации по решению этих вопросов, которые и будут рассмотрены ниже.

Неиспользуемые входы элементов типа И рекомендуется подключать к положительному выводу источника питания через резистор с сопротивлением 1 кОм. Через один резистор можно подключать не более 20 входов.

Для устранения помех, возникающих в шинах питания и земли в следствии протекания сквозных токов в сложных инверторах, необходимо вблизи разъема и по площади печатной платы устанавливать блокировочные конденсаторы. Емкость конденсатора, устанавливаемого вблизи разъема, рассчитывается из соотношения: 0.1 мкФ на каждые 100 мА потребляемого тока. Дополнительно, на каждые 5 - 10 ЦИС устанавливается блокировочный конденсатор емкостью 0.047 - 0.1 мкФ по площади печатной платы.

При передаче коротких импульсов, длительностью менее 100 нс, с короткими фронтами даже в пределах печатной платы могут возникнуть существенные изменения в его форме. Для предотвращения искажений рекомендуется выход элемента, формирующего короткие импульсы, подключать к общей шине через резистор с сопротивлением 100 Ом. При передаче сигналов между блоками на расстояние до 3 м связи между ними рекомендуется выполнять витой парой, а при длине более 3 м - коаксиальным кабелем с волновым сопротивлением 100 Ом с применением согласующих сопротивлений на передающем и приемном концах.

2015-05-13

2015-05-13 2416

2416