Лабораторная работа №5

Тема: МОДЕЛИРОВАНИЕ ЦИФРОВЫХ УЗЛОВ С ИСПОЛЬЗОВАНИЕМ ПАКЕТОВ МНОГОЗНАЧНОЙ ЛОГИКИ.

Выполнили: группа А-06-15

Дряхлов Иван

Аксенов Алексей

Принял:

Оценка:

Москва,2017

Для двухступенчатого JK-триггера с асинхронными RS-входами построить

а) модельэтойсхемы;

entity INE_2 is port (

xl,x2:in bit; yl:inout bit);

end INE_2;

entity INE_3 is pert (

xl,x2,x3:in bit; yl: inout bit);

end INE_3;

entity INE_4 is port (

xl, x2,x3,x4:in bit; yl: inout bit);

end INE_4;

architecture func_INE_2 of INE_2 is

signalsi,з2,s3:bit;

begin

sl<=xl;

s2<=x2;

s3<=not(xl and x2); process(xl,x2,si,s2,s3) begin

if((si'event and sl='0’)or(s2'event and s2-'0’)) then yl<=s3 after 1 ns;

elsif((si'event and si-'1')or(з2'event and s2- 1 ’)) then yl<=s3 after 3 ns;

end if; end process;

endfunc INE 2;

architecture func_INE_3 of INE_3 is signal sl,s2,s3,s4:bit; begin

sl<=xl; s2Ox2; s3<=x3;

s4<=not(xl and x2 and x3); ргосезз(xl,x2,x3,з1,з2,зЗ, s4) begin

if((si’event and sl=’0’)or(s2’event and s2=*0’)or(зЗ’event and s3=0 уК=з4 after 1 ns;

elsif((si•event and sl='1‘)or(s2’event and s2='1’)or(s3'event and s3 yl<=s4 after 3 ns;

end if; end рrocess;

end func_INE_3;

architecture func_INE_4 of INE_4 i3

3ignal si,s2,s3,s4,s5:bit;

begin

sl<=xl;

з2<=х2;

s3<=x3;

s4<=x4;

s5<=not(xl and x2 and x3 and x4); рrocess(xl,x2,x3,x4,si,s2, зЗ, з4, s5) begin

if((si’event and sl='0')or(s2'event and з2=’0‘)or(зЗ’event and s3=’O or(s4*event and з4=‘Э’)) then yl<=s5 after 1 ns;

elsif((sl*event and sl=’1’)or(з2’event and s2='21)or(зЗ’event and зЗ or(s4 * event and s4= * 1 ‘)) then yl<=s5 after 3 ns;

end if; end process;

end func_INE_4;

entityschl is port (

C, J,K,NS,NS:m bit;

Q,NS:inout bit);

endschl;

architecturefunc_schl of 3chl is componentINE_2 is

port

(

xl,x2:in bit; yl:inout bit);

end component; component INE_3 is

port

(

xl,x2,x3:in bit; y1:inout bit);

end component;

Exponent INE_4 is

/ port

(

xl,x2,x3,x4:in bit; yl:out bit):

end component;

signalzl, z2,z3,z4,z5,z6:bit

Begin

assert nor(NS=’0’ and NK=* 0')

report("Ошибка: Неопределенное состояние")

severity error;

Tl: INE_4 port map(C,O,NS,NQ, zl);

T2: INE_4 port map(C,K,NS,Q,z2);

T3: INE_3 port map(zl,NS,z4,z3);

T4: INE_3 port map(z2,NS,z3, z4);

T5; INE_2 pert map(z3,zl,z5);

T6: INE_2 port map(z4,z2,z6);

T7: INE_3 port map (z5,N5,NQ,Q);

T3; INE 3 pert map (z6,Na,C,NQ);

endfuncschl;

б) модель внешней среды, включающей:

• модель генератора входных сигналов, создающую в процессе моделирования тестовую последовательность импульсов для данной схемы;

entity GEN is port (

С, NS, NR, J, X: out bit >:

end GEN;

architecturef_GEN of GEN is

begin

SIG_C; process begin

C<-’0’; wait for 10 ns;

C<= 1’; wait for 10 ns;

end process SIG_C;

NS<=1_' after S5 ns,

'O’ after 103 ns;

NR<=’-’ after €5 ns,

‘O’ after 33 ns; J<='1’ after 5 ns, 'O’ after 22 ns,

’ 1' after 45 ns, 'O’ after 53 ns,

'after 65 ns,

* 0’ after 73 ns; K<=' 1’ after 27 ns 'O’ after 33 ns,

'1’ after 46 ns, ’O’ after 65 ns, '1’ after 85 ns,

end f_GEN;

модель наблюдателя-регистратора результатов эксперимента с моделью.

entity writer is port (

Q,NQ:in bit);

end writer;

use STC.TEXTIC.ALL;

architecturewriterl of writer is begin

process

variableLzLINE; begin

wait on Q,NQ; write(L,NCW); write (L,Q); write(L,NQ); writeline(output,L);

end process; end writerl;

Модельвнешнейсреды:

entity model is

end model;

architecturemodell of model is

component GEN is port (

C,NS,NR,J,K:out bit);

end component;

component writer is port (

C,NS:in bit);

end component;

componentschl is port (

C,NS,NR,O,K:in bit;

G,NQ:inout bit);

end component;

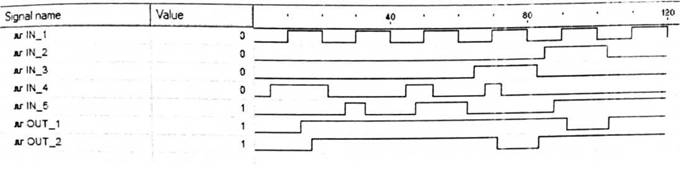

signal IN_1,IN_2,IN_3,IN_4,IN_5,OUT_1,OUT_2:bit;

begin

T1:GEN port map (IN_1, IN_2, IN_3, IN_4, IN__5);

T2:schl port map(IN_1,IN_2,IN_3,IN_4,IN_5,OUT_1,OUT_2); T3:writer port map(OUT_1,OUT_2);

endmodell;

Провести исследование разработанных моделей как единой модели:

2018-02-13

2018-02-13 889

889