Рассмотрим, в качестве примера, создание УГО элемента DS2438 (Smart Battery Monitor). Первое, что нужно сделать, это открыть OrCAD CIS, затем, как отмечено выше, открыть в меню File, создание новой библиотеки (см. рис. на рис. 13)

Рис. 13. Вид окна для создания новой библиотеки

Заполняем таблицу значений, которая приведена на рисунке 12. После сохранения необходимо добавить данный УГО к общей библиотеке (см. рисунок 14).

Рис. 14. Условно графическое обозначение созданного элемента DS2438.

Для этого необходимо просто нажать кнопку Save As. После этого необходимо найти библиотеку, которая находится там, где установлен пакет OrCAD. Эта операция приведена на рисунке 15.

Рис. 15. Вид окна для сохранения проекта в библиотеке

Необходимо написать название нового элемента и указать путь для его сохранения. Необходимые действия показаны на рисунке 16.

Рис. 16. Путь для сохранения нового элемента в библиотеке Pspice.

Теперь можно открывать уже имеющийся проект и присоединять УГО элемента к имеющимся.

3.6. Создание новых элементов из имеющихся

Если в какой-либо библиотеке имеется УГО элемента, похожий на требуемый, то можно на его основе создать необходимый, либо изменить уже имеющихся УГО. Обычно для этой цели берутся элементы с одинаковым количеством выводов, цепей питания, входов и выходов и т.п.

Для того, чтобы скопировать элемент полностью, достаточно выделить его в окне менеджера проекта и нажать Сtrl-С, затем выделив нужную библиотеку – Сtrl-v.

Если требуется только графическое обозначение, то необходимо зайти в нужную библиотеку и создать новый элемент описанным в начале предыдущего подраздела способом, т.е. заполнить поля свойств (имя, число компонентов в корпусе микросхемы, алфавитная или цифровая нумерация, одинаковые или разные компоненты и т.д.) в диалоговом окне задания свойств нового элемента. В диалоговом окне, появляющемся по команде file\open\library выбрать для открытия библиотеку, содержащую элемент-прототип. После открытия библиотеки появится окно, содержащее список находящихся в ней элементов. Выбрать нужный элемент в списке существующих в библиотеке, например, К140УД2 и дважды щёлкнув по нему левой кнопкой мыши. На экране появится этот элемент. В меню выбрать команду edit\select all, (выделить весь рисунок элемента для копирования) и команду edit\copy, т.е. скопировать выделенное в буфер обмена. Окно с графическим начертанием элемента-прототипа закрыть. Затем закрыть окно библиотеки (со списком содержащихся радиоэлементов), в которой брали элемент-прототип. На экране останется окно со списком элементов, содержащихся в библиотеке, в которой требовалось создать новый элемент. В списке также должно появится и имя вновь созданного элемента (для которого выше задали свойства). Двойным нажатием левой кнопки на имени этого элемента вывести его на экран. Поскольку графическое изображение элемента ещё создано не было, появится чистый лист с габаритной рамкой. Командой меню edit\paste from clipboard вставить запомненное в буфере обмена графическое изображение элемента-прототипа. Далее проделывать действия по изменению номеров ножек, их названий, свойств, графического начертания элемента, добавлению новых или исключению лишних ножек для получения требуемого вида элемента, как это показано в подразделе 3.4.

3.7. Создание иерархических блоков

Проект часто включает несколько схем, например, комплект схем телевизора обычно включает в себя лист, на котором изображены соединения основных блоков и на отдельных листах схемы самих блоков. Иерархические блоки как раз и предназначены для представления отдельной схемы в виде блока.

|

Создать блок можно, нажав на кнопку Place hierarchical block на панели рисования. В появившемся окне рис. 13 в поле Reference следует указать название блока, в поле Implementation type – Schematic View, а в поле Implementation – имя папки со схемами в Design manager (существование необязательно, при необходимости создается автоматически).

Рис. 13. Меню создания иерархических блоков

После нажатия Ok мышкой рисуется контур блока. Линии ввода-вывода или так называемые порты ввода-вывода кнопкой устанавливаются с помощью Place pin. Во всплывающем меню предлагается целый набор портов ввода-вывода. Пример создания иерархического блока с портами ввода-вывода приведен на рис. 14.

|

Рис. 14. Пример иерархического блока

Далее в контекстном меню блока (правая клавиша мыши) выбирается пункт Descend Hierarchy (если в указанной папке существует несколько страниц, то будет задан вопрос об имени создаваемой страницы). После этого появится страница с уже нарисованными портами (если страница уже была создана, порты не появятся), на которой и рисуется схема блока. Заметим, что порты можно добавить и кнопкой Place port, расположенной на панели инструментов.

3.8. Межстраничные соединения

Разработка сложной (большой) схемы потребует ее размещения на нескольких страницах, например формата А4. Для представления схемы как целой используются межстраничные соединители. Создание межстраничных соединений проводится путем нажатия на кнопки Place off-page connector на панели рисования. Межстраничные соединения объединяются в пределах схемной папки с портами иерархических блоков с тем же именем.

3.9. Проверка правильности соединений в схеме

Для устранения ошибок, допущенных при проектировании, в редакторе Capture Cis имеются правила проверки соединений DRC (Design Rules Check). DRC позволяет проконтролировать правильность сделанных в схеме соединений (не подсоединенные контакты), цепей, портов, межстраничных соединений, позиционных номеров элементов схемы, выявить несовпадения типов элементов при объединении их в один корпус. После запуска команды Tools>Design Rules Check появляется окно, имеющее две закладки (рис. 15 а и б).

На рис.15 а показана информация, которая будет внесена в отчет о проверке схемы.

В отчеты вносятся сообщения о нарушении правил проектирования двух типов:

§ Errors (E) - ошибки, которые обязательно должны быть исправлены.

§

|

Warnings (W) - предупреждения о возможных ошибках при проверке работоспособности спроектированной схемы путем моделирования ее работы (реагировать на них не обязательно).

а)

б)

Рис. 15. Задание конфигурации команды Tools>Design Rules Check

Рассмотрим некоторые опции закладки

Disign Rules check.

§ Scope - проверка всего проекта, выбранной страницы схемы.

§ Check unconnected nets - выявление цепей, каждая из которых не соединена по крайней мере с двумя выводами или не подключена к источникам внешних сигналов, а также цепей, имеющих на разных страницах схемы одинаковые имена.

§ Report all net names- составление списка всех имен цепей.

Правила проверки электрических соединений задаются с помощью ERC Matrix -матрицы правильности соединений, приведенной на рис. 15 б.

В ERC матрице по вертикальным и горизонтальным осям приведены различные типы выводов. Разноцветные квадраты, расположенные на пересечении определенной строки и столбца, определяют уровень критичности соединений соответствующих выводов. Серый цвет (No Report) сигнализирует о том, что соединение допускается и ошибки нет. Желтый (буква W) соответствует предупреждению о возможной ошибке, например, когда в схеме присутствует ненагруженный входной вывод (столбец Unconnected и строка Input Pin). Красный (буква E) соответствует ошибке, например, соединение выводов элемента (строка Output) с выводом выход (столбец Output) является ошибкой, которую нужно устранить. Кроме этого, имеются Passive Pin – соединение пассивных элементов.

Изменение уровня критичности ошибки производится последовательным перебором трех возможных значений щелчком левой кнопки мыши на нужном квадратике.

Для проверки соединений настроим матрицу ERC таким образом, чтобы она выявляла ненагруженные выходы в разрабатываемой схеме дешифратора DC2X4. Для этого найдем пересечение строки ХХХХ со столбцом УУУУ. Серый цвет квадрата говорит о том, что такое состояние по умолчанию нарушением не является. Щелкните левой кнопкой мыши один раз по этому квадратику, после чего его цвет изменится на желтый, что соответствует предупреждению.

Результатом проверки DRC является установка на страницах схемы в местах ошибок DRC маркеров, имеющих вид "шайбы". Это позволяет легко обнаруживать и определять ошибки, допущенные при проектировании. Заметим, что результаты проверки можно посмотреть в окне команды Browse (меню Edit). Дважды щелкнув по любому значению в первой колонке всплывающей таблицы, можно перейти на соответствующий маркер в схеме. И, соответственно, дважды щелкнув по маркеру на схеме, получим окно с поясняющим этот маркер текстом.

После завершения редактирования и DRC проверки принципиальной схемы её необходимо сохранить командой меню file\save и подготовить к переводу в формат, понятный разводчику печатных плат OrCAD Layout, а именно создать файл соединений. Связь программ OrCAD Capture и OrCAD Layout (рис. 16) осуществляется с помощью файла перечня элементов и соединений (netlist), создаваемого с расширением *.mnl.

Рис. 16. Схема взаимодействия OrCAD Capture и OrCAD Layout

Файл соединений создаётся командой меню tools\create netlist. В появившемся диалоговом окне необходимо посмотреть и запомнить (или записать на листке бумаги) полное имя файла и его расположение на диске (путь), предлагаемое программой, после чего нажать кнопку ОК. На этом можно считать, что проектирование принципиальной схемы закончено.

3.10. Оформление отчета о выполненном проекте

Программное обеспечения OrCAD позволяет создавать отчеты о выполненных проектах в формах Cross Reference - список позиционных обозначений и Bill of Materials - перечень элементов схемы. Перечень элементов может быть получен в двух видах, между которыми небольшие отличия. Для получения списка позиционных обозначений необходимо зайти в главное окно проекта, затем перейти в меню Tools\Cross Refrencre, и в появившейся панели нажать кнопку ОК. Перечень элементов схемы получается аналогично по команде меню Tool\Bill of Materials. Перечни записываются в тот же каталог, что и сама принципиальная схема и с тем же именем, но с расширениями *.xrf и *.bom соответственно.

На принципиальных электрических схемах часто в качестве дополнительной информации наносят текст. Текстовая информация необходима для уточнения особенностей схемы, используемых элементов или особенностей монтажа, настройки и регулировки устройства. Кроме этого, текстовая информация используется для документирования разработанной схемы, так как содержит выходные данные о фирме и разработчиках схемы.

Для размещения текста на принципиальной электрической схеме необходимо, находясь в OrCAD, зайти в меню place\part, выбрав Place Text. В появившемся меню закладки Color и Rotation определяют цвет и расположение текста на схеме. А закладки Font/ C hange позволяют выбирать алфавит и размеры символов, либо использовать его по умолчанию U se Default. В Capture CIS можно импортировать текст из любого приложения Windows. Для этого необходимо войти в приложение и скопировать текст в C lipbord командой C opy. Затем в редакторе схем выбрать в меню Place закладку Text, одновременным нажатием клавиш Ctrl+V вставить текст в окно для текста. Экспорт текста в другие приложения из редактора схем выполняется из меню E dit командой copy.

Обязательным элементом документа является штамп, в который заносится информация о названии проекта, фирме и разработчике схемы, ее вариантах. Для размещения штампа на принципиальной электрической схеме необходимо зайти в меню place\part и выбрать раздел Title Bloc k. В появившемся меню выбрать наиболее подходящий штамп, например TitleBlock4N. Для изменения надписей штампа необходимо щелкнуть два раза левой кнопкой мыши, а затем, выбрав в выпадающем меню необходимые установки алфавита и размеров шрифта, сделать соответствующие изменения.

Разработанный проект и библиотеки можно экспортировать или импортировать командами Export Design Import Design закладки File в форматы. EDIF и. DXF. Например, при экспортировании схемы в формат. DXF получается файл с расширением. DXF в формате AutoCAD v.12.

4. Моделирование работы разработанных устройств

Пакет OrCAD позволяетмоделировать (исследовать) работу разработанных электронных устройств при изменении температуры, расчете надежности, вариациях питающих напряжений и других факторах, а также проводить временное моделирование. Рассмотрим только временное моделирование.

4.1. Общие сведения

Проверка работоспособности спроектированной схемы устройства проводится путем моделирования его работы и анализа временных процессов, происходящих в нем. Временной анализ работы позволяет устранить "состояние гонок", неопределенности и этим повысить устойчивость работы проектируемого устройства в целом. Моделирование работы цифровых устройств в OrCAD производится с помощью программы PSpice, которая запускается автоматически при старте OrCAD.

4.2. Инструменты, используемые при моделировании

Рассмотрим пример моделирования на примере нарисованной ранее схемы дешифратора 2Х4. Для установки точек наблюдения сигнала используются пиктограммы Voltage/Level Marker и т.п., приведенные на панели моделирования и показанные на рис. 17.

Рис. 17. Вид маркеров, позволяющих контролировать временные процессы

Физический смысл маркеров, используемых при моделировании очевиден - это вольтметры, амперметры и ваттметры, позволяющие контролировать соответствующие физические величины в различных точках схемы. Причем точки измерения напряжения и разности потенциалов устанавливаются на проводники, тока – на выводы элементов, а мощности – на сами элементы.

В библиотеках SOURCE и SOURCSTM имеются источники сигналов (в OrCAD их принято называть стимулами), позволяющих моделировать работу цифровых и аналоговых устройств.

Библиотеки SOURCE и SOURCSTM включают: VDC – постоянного напряжения; VSTIM – график напряжения из stl-библиотеки; VSIN ‑ синусоидального напряжения; DigStim1 ‑ из stl-библиотеки; DigClock – меандра; STIM1 – импульсный сигнал.

Имеются источники логических уровней: 0– земля (необходим в аналоговых схемах); $D_HI – логическая «1»; $D_LO – логический «0».

Устанавливаются логические уровни кнопками Place power или Place ground, расположенными на панели инструментов. Сигналы (стимулы) кратных частот удобно создавать с помощью источников STIM1 или DigClock, имеющихся в библиотеке SOURCE.

Вид стимулов STIM1 (DSTM1), DigClock (DSTM2) и источников логических уровней «1» и «0» L0, L1 приведен на рис. 18.

Рис. 18. Вид стимулов STIM1 (DSTM1), DigClock (DSTM2) и L0, HI

Из приведенного рисунка видно, что параметры стимулов STIM1 и DigClock можно изменять. В частности, устанавливать логические уровни начала и конца импульсной последовательности, время единичного и нулевого уровней, время задержки между сигналами. Это особенно удобно использовать при моделировании, если временной протокол работы схемы известен и требуется только его уточнение при вариации параметров элементов схемы (анализа временных задержек).

Вид схемы DC2X4 с размещенными на ней стимулами и маркерами показан на рис. 19.

Рис. 19. Схема дешифратора DC2X4

4.3. Установка параметров моделирования

Вид пиктограмм управления моделированием показан на рис. 20.

Рис. 20. Пиктограммы управления моделированием

Левая пиктограмма на рис. 20 позволят создать новый файл для моделирования в Pspice AD и определить тип проводимого моделирования. Вид возникающего при этом меню показан на рис. 21.

Рис. 21. Вид меню Analysis

Закладка Analysis определяет вид моделирования. Для проведения временного моделирования необходимо выбрать Time Domain (Transient). Заметим, что OrCAD позволяет проводить испытания (моделирование работы) схемы при температурных испытаниях и статистическом моделировании.

Поля R un to time, Start saving data after и Maximum step size задают соответственно общее время моделирования, начало записи результатов в файл и интервал дискретизации процесса моделирования (разрешения). Если интервал дискретизации не указан, он выбирается автоматически (минимальный). Установки выполняются в секундах или производных секунд. Следует учитывать параметры стимулов и продолжительность времени моделирования.

Более наглядными результаты будут в том случае, если за время моделирования наблюдается 3-4 периода используемых стимулов.

Флажок Skip the initial transient bias point calculation указывает пропустить или нет начальный участок моделирования по постоянному току (имеет смысл установить, если требуется моделировать переходные процессы в схеме).

Закладка Stimulus позволяет работать со стимулами, созданными редактором Stimulus Editor (SE). С ее помощью можно подключить stl -библиотеки и этим проводить более полное моделирование разрабатываемых схем.

Запуск моделирования осуществляется активированием пиктограммы Run PSpice (рис. 20, 2-я справа) на панели моделирования, при этом, если не было ошибок, запустится PSpice и если и он не обнаружит ошибок, то через некоторое время появится окно с результатами моделирования. Результат моделирования приведен на рис. 22.

Рис. 22. Результаты моделирования схемы DC2X4

Следует заметить, что название временных диаграмм соответствует элементам схемы, а их расположение - порядку размещения на схеме маркера «V».

|

Закладка Option позволяет проводить начальную установку триггеров и счетчиков (рис. 23). Эти установки необходимы при моделировании работы счетчиков и делителей частоты. Перейдя в закладку Gate level Simulation, выбрав меню I nitialize all flip-flop to (рис. 23), можно установить соответственно начальное состояние «1», «0» или неопределенное «X». Заметим, что здесь же имеется закладка Default I/O level for A/D, позволяющая устанавливать по умолчанию уровни выходных сигналов для A/D.

|

Рис. 23. Закладка Option/Gate level Simulation

5. Редактор стимулов Stimulus Editor

Моделирование работы является закономерным финальным результатом разработки принципиальных электрических схем любого устройства радиоэлектроники. Оно позволяет не только проверить правильность составления схемы, но и убедиться в ее работоспособности в динамике, а также оценить весь временной протокол работы устройства.

Моделировать работу электронных схем в САПР OrCAD можно проводить двумя путями с использованием OrCAD Simulate или PSpice A/D. Об этом уже говорилось при создании проекта. Напомним, что PSpice A/D удобнее применять для моделирования смешанных цифровых и аналоговых схем, в этом случае используются библиотеки PSpice, а ORCAD Simulate - для моделирования цифровых схем с использованием средств VHDL модулей.

В состав PSpice A/D входит редактор Pspice Stimulus Editor (SE), предназначенный для создания и редактирования входных воздействий (файлов сигнала с расширением *.stl) или стимулов (дословныйперевод с английского). Рассмотрим теперь основные приемы работы с SE, которые позволяют провести моделирование работы принципиальных электрических схем. Редактор SE предоставляет более широкие возможности для проведения моделирования.

5.1. Создание файла стимула

Для создания нового файла необходимо запустить редактор SE. Пиктограмма PSpice Stimulus Editor находится в общем меню пакета ORCAD. После запуска SE появляется окно редактора, представленное на рис. 24.

Рис. 24. Вид окна SE

SE позволяет создавать стимулы (сигналы) (возможно создание нескольких стимулов в одном файле), проводить моделирование работы схемы, переносить и сохранять результаты моделирования.

Закладка F ile на этой панели позволяет создать новый или открыть уже существующий файл. Следует заметить, что порядок расположения пиктограмм SE (слева направо) совпадает с их применением для создания и редактирования стимулов.

Заметим, что для хранения и обработки результатов удобно в имени создаваемого (*.stl) файла упоминать имя проекта, а стимулы нумеровать порядковыми номерами. Например, моделируется работа разработанной ранее схемы дешифратора 2Х4. Вспомним, что проект назывался DC2X4, а создаваемый файл будем называть TestDC2X4, соответственно входящие в него стимулы 1, 2, 3 и т.д. Можно добавить в название и характерную особенность стимула, такую как временная задержка, начальные установки и прочее.

Меню E dit (редактирование) имеет вид, приведенный на рис. 25.

Рис. 25. Меню E dit

Пункты D elete и A dd позволяют соответственно удалять или добавлять точки в редактируемых стимулах. A tributes – позволяет изменять параметры стимулов. Рассмотрим этот пункт позднее при редактировании уже созданных стимулов.

Меню S timulus (стимул) имеет вид, показанный на рис. 26.

Рис. 26. Меню S timulus

При создании нового стимула (пункт меню N ew) появится диалоговое окно, показывающее, какие сигналы могут быть использованы в SE. Вид окна показан на рис. 27, а описание видов стимулов приведено в таблице 1.

Заметим, что если имя стимула не введено, появится подсказка, указывающая на это, а если имя повторяется, то появляется подсказка о необходимости его изменения.

Рис. 27. Стимулы, используемые в SE

Опция B US имеет поле Width, позволяющее задавать ширину шины (количество проводников), а список Initial V alue позволяет выбрать начало стимула (сигнала) соответственно с нуля, единицы, неопределенного или третьего состояния Z.

Виды стимулов Таблица 1

| Вид | Описание |

| Аналоговые | |

| EXP | Экспонента |

| PULSE | Меандр |

| PWL | Кусочно-линейный сигнал (форма задается произвольно) |

| SFFM | ЧМ-сигнал |

| SIN | Синусоидальный (гармонический) |

| Цифровые | |

| Clock | Меандр |

| Signal | Сигнал произвольной формы |

| Bus | Шина представляется в виде нескольких линий |

Пункт G et – позволяет выбрать один из стимулов (если их было несколько). Остальные пункты этого меню понятны и не требуют пояснения.

5.2. Редактирование стимулов

Общие свойства стимула можно вывести, дважды щелкнув на его названии слева от графика, либо выбрав стимул, щелкнув на названии, а затем нажав  . Появившееся диалоговое окно будет зависеть от типа стимула. Выбранный SE стимул выделяется красным цветом.

. Появившееся диалоговое окно будет зависеть от типа стимула. Выбранный SE стимул выделяется красным цветом.

Форма стимулов типов PWL, Signal и Bus задается в режиме рисования, который включается нажатием  , а выключается правой кнопкой мыши. После выхода из режима рисования точки изменения стимула можно передвигать мышью.

, а выключается правой кнопкой мыши. После выхода из режима рисования точки изменения стимула можно передвигать мышью.

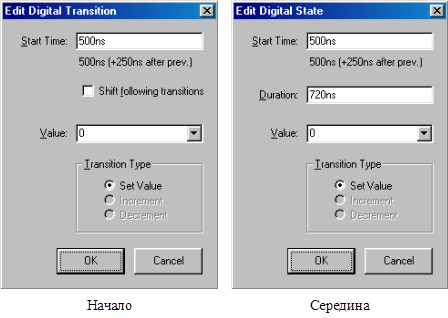

Для цифровых стимулов присутствует диалоговое окно установки параметров участков сигнала, которое выводится либо двойным нажатием на требуемый участок, либо выбором участка и нажатием  , причем при выборе начала или середины участка выводятся разные диалоговые окна.

, причем при выборе начала или середины участка выводятся разные диалоговые окна.

Вид меню установки параметров стимулов показан на рис. 28.

Рис. 28. Диалоговое окно установки параметров стимулов

В этом диалоговом окне S tart Time – время начала участка; Shift f ollowing transitions – сдвигать последующие участки при изменении времени начала текущего; D uration – длительность; V alue – значение сигнала; Set Value – присвоить сигналу значение поля V alue; Increment – увеличить значение на V alue (только для шины); Decrement – уменьшить значение на Value (только для шины).

Для того, чтобы опции Set Value, Increment или Decrement устанавливались автоматически во время рисования, нужно устанавливать соответственно X, +X или –X (где X – требуемое значение) в окне, расположенном справа от пиктограммы  .

.

Для установки разрядности цифрового стимула и вида его отображения присутствует диалоговое окно (рис. 29), которое можно вызвать двойным нажатием на название стимула, либо выбором названия стимула и нажатием  . В этом окне в поле Bus W idth устанавливается разрядность шины (1 для сигнала), а в списке Display R adix – вид отображения (для шины – система счисления). Все вышеперечисленные действия можно также осуществлять с помощью соответствующих пунктов меню E dit.

. В этом окне в поле Bus W idth устанавливается разрядность шины (1 для сигнала), а в списке Display R adix – вид отображения (для шины – система счисления). Все вышеперечисленные действия можно также осуществлять с помощью соответствующих пунктов меню E dit.

Рис. 29. Вид окна с редактируемым стимулом

5.3. Определение границ отображаемой области

Для определения объема отображаемой на экране информации необходимо активировать пиктограмму  . Появляющееся окно показано на рис. 30.

. Появляющееся окно показано на рис. 30.

В опции Displayed Data Range указывается начало и конец области, отображаемой в окне целиком, в Extent of the Scrolling Region – указываются пределы отображаемой области при использовании полос прокрутки, а опция Minimum Resolution задает минимальное разрешение (интервал дискретизации) по каждой из осей.

Рис. 30. Окно задания границ отображаемой области

5.4. Пример моделирования с использованием редактора SE

Пример моделируемой схемы дешифратора DC2Х4 с расставленными маркерами и стимулами приведен на рис. 31

|

. Рис. 31. Схема дешифратора DC2Х4

Результаты моделирования работы дешифратора DC2Х4 приведены на рис. 32.

|

На этом рисунке верхние строки A0 и A1 показывают состояние шины, а четыре нижние строки - выходы элементов 7408 (логических элементов 2И-НЕ) дешифратора с U2A по U2D. По оси абсцисс отложено время моделирования.

Рис. 32. Результаты моделирования работы дешифратора DC2X4

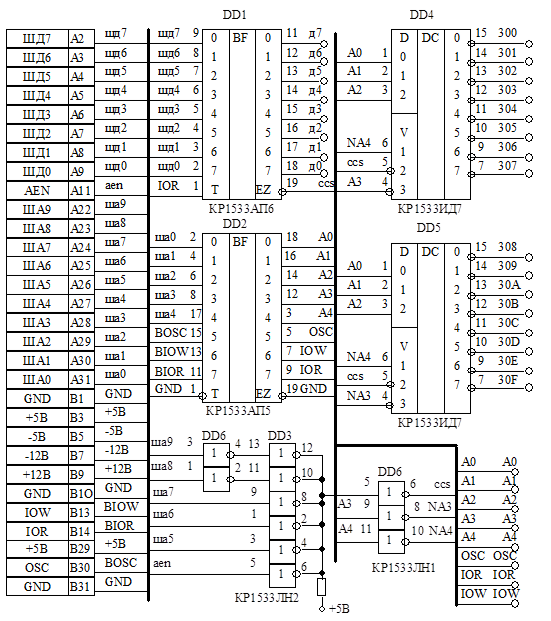

Пример устройства имеющего архитектуру 'общая шина' для двунаправленной передачи информации. Пример схемы такого устройства показан на рис. 33. На рис. 34 приведена временная диаграмма работы схемы 'общая шина'.

|

Рис. 33. Архитектура 'общая шина'

При разработке цифровых устройств с шинной архитектурой необходимо выполнять одно из главных условий, а именно - в любой момент времени на шине может быть только один источник информации и в общем случае несколько приемников, приемник информации может быть ее источником. Для этого в устройстве с шиной необходимо использовать буферы с третьим состоянием. В библиотеке ORCAD имеются следующие элементы, позволяющие шине находиться в состояниях «1», «0» и «Z», это буферы 74НС125, 74НС126 и регистры 74НС245, 74НС205, 74НС573, имеющие третье состояние.

|

На рис. 34 видно неопределенное состояние линий шины (на экране он выделяется синим цветом) и соответственно входы и выходы линий.

Рис. 34. Временная диаграмма работы схемы 'общая шина'

На этой схеме управляющими сигналами являются стимулы DSTM2 и DSTM3, один из которых активизирует 74НС125, а другой направление передачи.

6. Задание на самостоятельную работы

При выполнении работ используйте серию ИМС 7400 - аналог отечественной серии К1533, или CD аналог серии К561.

Практикум работы с OrCAD включает шесть работ которые необходимо выполнить для начального освоения OrCAD.

Работа 1. Знакомство с OrCAD. Подготовка среды и создание нового проекта. Редактор схем OrCAD CiS.

Цель работы - показать возможности пакета и привить начальные навыки по его использованию.

Работа 2. Рисование и редактирование простых принципиальных электрических схем

Цель работы - научиться рисовать и редактировать принципиальные электрические схемы цифровых и аналоговых радиоэлектронных устройств. Часть 1.

Работа 3. Рисование, редактирование и оформление принципиальных электрических схем, содержащих программируемые БИС и архитектуру типа ОШ.

Цель работы - научиться редактировать и оформлять принципиальные электрические схемы Часть 2.

Работа 4. Составление новых элементов и иерархических блоков.

Цель работы - научиться создавать графические обозначения элементов схемы, отсутствующих в библиотеках OrCAD и рисовать сложные принципиальные электрические схемы.

Работа 5. Временное моделирование работы средствами OrCAD на примере счетчиков с последовательным и параллельным переносом и пересчетных схем, делителей частоты. Моделирование динамики работы цифровых устройств, оценка временных задержек в схемах. Пример моделирования схемы телевизионного синхрогенератора.

Цель работы - научиться проводить временное моделирование работы цифровых устройств.

Работа 6. Временное моделирование работы цифровых устройств, в том числе с архитектурой ОШ. Пример моделирования и исследования работы релаксационного генератора, одновибратора, схемы задержки, дешифратора и шифратора кодов. Моделирование динамики работы ОШ с переключением в состояния «1», «0» и «Z».

Цель работы - научиться проводить моделирование и исследование работы цифровых и микропроцессорных устройств с использованием редактора SE. Пример - моделирование работы режима ввода/вывода контроллера шины ISA.

7. Контрольные вопросы

Объем полученных знаний контролируется предъявленными в виде отчета результатами и ответом на следующие контрольные вопросы.

1. Назовите составляющие пакета OrCAD.

2. Настройка, меню проекта Options, Preference, Design Template.

3. Покажите возможности изменения размеров бумаги, сетки (Grid) и возможности их использования при рисовании принципиальных электрических схем.

4. Покажите действие флажка Pointer snap to grid. Поясните его применение для разработки схемы.

5. Поменяйте цветовое оформление схемы и используемые фонты.

6. Чем отличается задание Project от Design. Поясните структуру проекта, созданного в OrCAD.

7. Запишите в штампе разработанной принципиальной электрической схемы ее название, номер вашей группы, ФИО ваc и преподавателя.

8. Покажите возможности нумерации проводников, входящих в архитектуру “общая шина”.

9. Познакомьтесь с закладкой Select диалоговой панели Preferences. Покажите возможность и рациональность ее применения.

10. Покажите свойства указанного преподавателем элемента схемы.

11. Создайте “новый” элемент из уже имеющегося прототипа.

12. Создайте оптрон (аналог КР294ЛП1), в качестве прототипа возьмите, например, К544UD1.

13. Создайте список элементов разработанной принципиальной электрической схемы.

14. Нарисуйте принципиальную электрическую схему дешифратора 3Х8, 2Х4 на логических элементах 2И-НЕ, 3И-НЕ или ИЛИ.

15. Покажите возможности поиска элементов схемы при частичном задании их имени из редактора схем и менеджера проектов.

16. Проведите моделирование работы дешифратора 3Х8 или 2Х4, изменяя временные параметры (соотношения) стимулов (сигналов).

17. Нарисуйте принципиальную электрическую схему совпадения кодов 300Н, 200Н.

18. Нарисуйте принципиальную электрическую схему по указанию преподавателя, приведенную в приложении. Проверьте правильность соединений и проведите ее временное моделирование. Сделайте перечень элементов схемы. Перечислите источники и виды стимулов, использующихся в OrCAD.

19. На примере DSTM продемонстрируйте возможности изменения параметров стимулов.

20. Покажите отличие стимулов DSTM и CLOCK.

21. Нарисуйте схему релаксационного генератора. Проведите моделирование и исследование его работы. Используйте редактор SE для задания сигналов.

22. Нарисуйте ЛЧМ цифровой сигнал.

23. Установите состояние ОШ адреса 200Н и 1FH.

24. Установите состояние ОШ последовательно с адреса 300Н по 31FH.

25. Нарисуйте схему одновибратора. Проведите моделирование и исследование его работы. Нарисуйте схему задержки на RC цепи.

26. Нарисуйте схему временной задержки (регистра сдвига). Проведите моделирование и исследование его работы.

27. Нарисуйте двоичные счетчики с последовательным и параллельным переносом и начальной установкой в «1» и «0».

28. Сделайте необходимые установки и исследуйте временные характеристики счетчиков, варьируя параметры стимулов DSTM и CLOCK.

29. Промоделируйте работу буферного элемента (ИМС 74НС125, 74НС126) ОШ.

30. Промоделируйте в динамике работу ОШ с переключением в состояния «1», «0» и «Z». Используйте ИМС 74НС245, 74НС205, 74НС573.

31. Разработайте схему дешифратора ОШ с базового адреса 300Н последовательно с 300Н по 30FH.

32. Выберите элементы и промоделируйте в динамике передачу с шины на один порт поочередно кодов AAH и 55H.

33. Поясните аббревиатуру DRC.

34. Объясните назначение строк и столбцов ERC матрицы и цветовую палитру элементов. Настройте ERC матрицу на проверку ошибки типа соединение «двух выходов» или «ненагруженный вывод».

35. Сымитируйте ошибку в схеме дешифратора DC2X4 типа «соединение двух выходов» или «ненагруженный вывод». Продемонстрируйте средствами проверки ее обнаружение.

8. Рекомендуемая литература

1. Разевиг В. Д. OrCAD 9.2. – Москва,: СОЛОН – Р, 2001 – 519 с.

2. Афанасьев А. О., Кузнецов С. А. OrCAD 7.0…9.0. Проектирование электронной аппаратуры и печатных плат. – СПб: Наука и техника, 2001. – 464 с.

3. Рафикузаманн А. Машинное проектирование микропроцессорных систем. В 2-х книгах – М.: Радио и связь, 1989, 126 с. Высшая школа, 1982. – 307 с.

4. Клингманн Э. Проектирование микропроцессорных систем - М.: Мир, 1980. - 575 с.

5. Сопряжение датчиков и устройств ввода данных с компьютерами IBM PC/ Под ред. Томпкинса У, Уэбстер Дж. - М.: Мир, 1992.- 589 с.

6. Новиков Ю.В., Калашников О.А., Гуляев С.Э. Разработка устройств сопряжения. - М.: ЭКОМ, 1997.- 224 с.

ПРИЛОЖЕНИЯ

Приложение 1

Генератор цугов

|

Приложение 2

Телевизионный синхрогенератор

Приложение 3

Дешифратор шины ISA

|

Приложение 4

Архитектура 'общая шина'

|

|

Приложение 5

Приложение 6

Зарубежные аналоги микросхем

| Серия '561' | Серия CD | Серии '561' | Серия CD |

| К561ЛН1 | CD4502 | К561ИМ1 | CD4008 |

| К561ЛН2 | CD4009 | К561ИР12 | CD45108 |

| К561ЛА7 | CD4011 | К561ИП2 | CD4585 |

| К561ЛА8 | CD4012 | К561ТВ1 | CD4027 |

| К561ЛА9 | CD4023 | К561ТМ2 | CD4013 |

| К561ЛЕ5 | CD4028 | К561ТМ3 | CD4042 |

| К561ЛЕ6 | CD4002 | К561ТР2 | CD4043 |

| К561 ЛЕ10 | CD4025 | К561ТЛ1 | CD4093 |

| К561КТ1 | CD4016 | К561ИЕ8 | CD4017 |

| К561КТ3 | CD4066 | К561ИЕ9 | CD4022 |

| К561КП1 | CD4052 | К561ИЕ10 | CD4520 |

| К561КП2 | CD4051 | К561ИЕ11 | CD4516 |

| К561ИР2 | CD4015 | К561ИЕ16 | CD4020 |

| К561ИР6 | CD4034 | К561СА1 | CD4531 |

| К561ИР9 | CD4032 | К561ИД1 | CD4028 |

| Зарубежный прибор | Тип прибора | Отечественный аналог |

| BC548 | Биполярный транзистор | КТ3102А, Б |

| BZY88C3V9 | Стабилитрон | КС433А, КС139А |

| BZY88C3V0 | Стабилитрон | КС133Г |

| BZY88C4V7 | Стабилитрон | КС447А, КС147А |

| BZY88C5V1 | Стабилитрон | КС456А, КС156А |

| BZY88C10V0 | Стабилитрон | Д814Г, КС210Ж |

| CD4001 | Цифровая ИМС КМОП-типа | К561ЛЕ5 |

| CD4002 | Цифровая ИМС КМОП-типа | К561ЛЕ6 |

| CD4012 | Цифровая ИМС КМОП-типа | К561ЛА8 |

| CD4013 | Цифровая ИМС КМОП-типа | К561ТМ2 |

| CD4020B | Цифровая ИМС КМОП-типа | К561ИЕ16 |

| CD4023 | Цифровая ИМС КМОП-типа | К561ЛА9 |

| CD4025 | Цифровая ИМС КМОП-типа | К561ЛЕ10 |

| CD4027 | Цифровая ИМС КМОП-типа | К561ТВ1 |

| CD4049 | Цифровая ИМС КМОП-типа | К561ЛН2 |

| CD4050 | Цифровая ИМС КМОП-типа | К561ПУ4 |

| CD4069 | Цифровая ИМС КМОП-типа | К561ЛН1 |

| CD4070 | Цифровая ИМС КМОП-типа | КР1561ЛП14 |

| CD4071 | ИМС:четыре логических элемента 2ИЛИ | — |

| CD4072 | ИМС: два логических элемента 4ИЛИ | — |

| CD4073 | ИМС три логических элемента 3И | — |

| CD4075 | ИМС три логических элемента 3ИЛИ | — |

| CD4076 | Цифровая ИМС КМОП-типа | КР1561ИР14 |

| CD4077 | ИМС: четыре логических элемента ‹‹Исключающее ИЛИ›› | — |

| CD4078 | ИМС: восемь логических элементов И–НЕ/ИЛИ | — |

| CD4081 | Цифровая ИМС КМОП-типа | КР1561ИР14 |

| L200 | ИМС регулируемого стабилизатора напряжения | К142ЕН3А К142ЕН12 |

| LM393 | ИМС сдвоенного компаратора напряжения | К1401СА3 |

| LM555 | ИМС таймера | КР1006ВИ1 |

| OA91 | Диод | КД295К, Д78 |

| SKB2/02L5A | Мостовой выпрямитель | КЦ402Д, КЦ403Д |

| SN7400 | Цифровая ИМС ТТЛ–типа | К155ЛА3 |

| SN7401 | Цифровая ИМС ТТЛ–типа | К155ЛА8 |

| SN7402 | Цифровая ИМС ТТЛ–типа | К155ЛЕ1 |

| SN7403 | Цифровая ИМС ТТЛ–типа | К155ЛА9 |

| SN7404 | Цифровая ИМС ТТЛ–типа | К155ЛН1 |

| SN7405 | Цифровая ИМС ТТЛ–типа | К155ЛН2 |

| SN7406 | Цифровая ИМС ТТЛ–типа | К155ЛН3 |

| SN7407 | Цифровая ИМС ТТЛ–типа | К155ЛН4 |

| SN7408 | Цифровая ИМС ТТЛ–типа | К155ЛИ1 |

| SN7409 | Цифровая ИМС ТТЛ–типа | К155ЛИ2 |

| SN7410 | Цифровая ИМС ТТЛ–типа | К155ЛИ4 |

| SN7411 | Цифровая ИМС ТТЛ–типа | К155ЛИ3 |

| SN7412 | Цифровая ИМС ТТЛ–типа | К155ЛА10 |

| SN7413 | Цифровая ИМС ТТЛ–типа | К155ТЛ1 |

| SN7414 | Цифровая ИМС ТТЛ–типа | К155ТЛ2 |

| Зарубежный прибор | Тип прибора | Отечественный аналог |

| SN7415 | Цифровая ИМС ТТЛ–типа | К155ЛИ4 |

| SN7416 | Цифровая ИМС ТТЛ–типа | К155ЛН5 |

| SN7417 | Цифровая ИМС ТТЛ–типа | К155ЛП4 |

| SN7420 | Цифровая ИМС ТТЛ–типа | К155ЛА1 |

| SN7421 | Цифровая ИМС ТТЛ–типа | К155ЛИ6 |

| SN7422 | Цифровая ИМС ТТЛ–типа | К155ЛА7 |

| SN7423 | Цифровая ИМС ТТЛ–типа | К155ЛЕ2 |

| SN7425 | Цифровая ИМС ТТЛ–типа | К155ЛЕ3 |

| SN7426 | Цифровая ИМС ТТЛ–типа | К155ЛА11 |

| SN7427 | Цифровая ИМС ТТЛ–типа | К155ЛЕ4 |

| SN7428 | Цифровая ИМС ТТЛ–типа | К155ЛЕ5 |

| SN7430 | Цифровая ИМС ТТЛ–типа | К155ЛА2 |

| SN7432 | Цифровая ИМС ТТЛ–типа | К155ЛЛ1 |

| SN7433 | Цифровая ИМС ТТЛ–типа | К155ЛР4 |

| SN7437 | Цифровая ИМС ТТЛ–типа | К155ЛА12 |

| SN7438 | Цифровая ИМС ТТЛ–типа | К155ЛА13 |

| SN7440 | Цифровая ИМС ТТЛ–типа | К155ЛА6 |

| SN7442 | Цифровая ИМС ТТЛ–типа | К155ИД6 |

| SN7445 | Преобразователь двоичного кода в десятичный | К155ИД10 |

| SN7447 | Преобразователь двоичного кода в сигналы 7-сегментного кода (15 В) | К155ИД18 |

| SN7448 | Преобразователь двоичного кода в сигналы 7-сегментного кода (5 В) | — |

| SN7449 | Преобразователь двоичного кода в сигналы 7-сегментного кода | К133ПП4 |

| SN7450 | Цифровая ИМС ТТЛ–типа | К155ЛР1 |

| SN7451 | Цифровая ИМС ТТЛ–типа | К155ЛР11 |

| SN74LS51 | Цифровая ИМС ТТЛШ–типа | К555ЛР11 |

| SN7453 | Цифровая ИМС ТТЛ–типа | К155ЛР3 |

| SN7454 | Цифровая ИМС ТТЛ–типа | К155ЛР13 |

| SN74LS55 | Цифровая ИМС ТТЛШ–типа | К555ЛР4 |

| SN7460 | Цифровая ИМС ТТЛ–типа | К155ЛД1 |

| SN7470 | ИМС JK -триггера с логическим элементом И на входе | — |

| SN7473 | ИМС сдвоенного JK -триггера | К531ТВ9, К155ТВ1 |

| SN7475 | Цифровая ИМС ТТЛ–типа | К155ТМ7 |

| SN7476 | ИМС сдвоенного JK -триггера | К531ТВ9П, К531ТВ11П |

| SN7477 | Цифровая ИМС ТТЛ–типа | К155ТМ5 |

| SN74LS78 | ИМС сдвоенного JK -триггера с предварительной установкой | — |

| SN7480 | Последовательный сумматор | К155ИМ1 |

| SN7482 | Сумматор | К155ИМ2 |

| SN7483 | Сумматор | К155ИМ3 |

| Зарубежный прибор | Тип прибора | Отечественный аналог |

| SN74LS86 | Цифровая ИМС ТТЛШ–типа | К555ЛП5 |

| SN7490 | Цифровая ИМС ТТЛ–типа | К155ИЕ2 |

| SN7491 | Цифровая ИМС ТТЛ–типа | — |

| SN7492 | Цифровая ИМС ТТЛ–типа | К155ИЕ4 |

| SN7493 | Цифровая ИМС ТТЛ–типа | К155ИЕ5 |

| SN7495 | Цифровая ИМС ТТЛ–типа | К155ИР1 |

| SN7496 | Цифровая ИМС ТТЛ–типа | К155ИР1 |

| SN74107 | Цифровая ИМС ТТЛ–типа | К155ТВ6 |

| SN74109 | Цифровая ИМС ТТЛ–типа | К155ТВ15 |

| SN74110 | Цифровая ИМС ТТЛ–типа | — |

| SN74111 | Цифровая ИМС ТТЛ–типа | — |

| SN74112 | Цифровая ИМС ТТЛ–типа | К155ТВ9 |

| SN74113 | Цифровая ИМС ТТЛ–типа | К155ТВ10 |

| SN74114 | Цифровая ИМС ТТЛ–типа | К155ТВ11 |

| SN74121 | Цифровая ИМС ТТЛ–типа | К155АГ1 |

| SN74122 | Цифровая ИМС ТТЛ–типа | К155АГ3 |

| SN74123 | Цифровая ИМС ТТЛ–типа | К155АГ3 |

| SN74124 | Цифровая ИМС ТТЛ–типа | К155ГГ1 |

| SN74125 | Цифровая ИМС ТТЛ–типа | К155ЛП8 |

| SN74126 | Цифровая ИМС ТТЛ–типа | К155ЛП14 |

| SN74128 | Цифровая ИМС ТТЛ–типа | К155ЛЕ6 |

| SN74132 | Цифровая ИМС ТТЛ–типа | К155ТЛ3 |

| SN74136 | Цифровая ИМС ТТЛ–типа | К155ЛЛ3,К555ЛП12 |

| SN74138 | Цифровая ИМС ТТЛ–типа | К155ИД7 |

| SN74139 | Цифровая ИМС ТТЛ–типа | К155ИД14 |

| SN74141 | Цифровая ИМС ТТЛ–типа | К155ИД1 |

| SN74145 | Цифровая ИМС ТТЛ–типа | К155ИД10 |

| SN74150 | Цифровая ИМС ТТЛ–типа | К155КП1 |

| SN74151 | Цифровая ИМС ТТЛ–типа | К155КП7 |

| SN74152 | Цифровая ИМС ТТЛ–типа | К155КП5 |

| SN74153 | Цифровая ИМС ТТЛ–типа | К155КП2 |

| SN74155 | Цифровая ИМС ТТЛ–типа | К155ИД4 |

| SN74173 | Цифровая ИМС ТТЛ–типа | К155ИР15 |

| SN74174 | Цифровая ИМС ТТЛ–типа | К155ТМ9 |

| SN74175 | Цифровая ИМС ТТЛ–типа | К155ТМ8 |

| SN74176 | Цифровая ИМС ТТЛ–типа | — |

| SN74177 | Цифровая ИМС ТТЛ–типа | — |

| SN74178 | Цифровая ИМС ТТЛ–типа | — |

| SN74179 | Цифровая ИМС ТТЛ–типа | — |

| SN74180 | Цифровая ИМС ТТЛ–типа | К155ИП2 |

| SN74184 | Цифровая ИМС ТТЛ–типа | К155ТПР6 |

| SN74190 | Цифровая ИМС ТТЛ–типа | — |

| SN74192 | Цифровая ИМС ТТЛ–типа | К155ИЕ6 |

| SN74193 | Цифровая ИМС ТТЛ–типа | К155ИЕ7 |

| SN74194 | Цифровая ИМС ТТЛ–типа | К155ИР11 |

| SN74199 | Цифровая ИМС ТТЛ–типа | К531ИР12П |

| SN74240 | Цифровая ИМС ТТЛ–типа | К155АП3 |

| SN74241 | Цифровая ИМС ТТЛ–типа | К155АП4 |

| Зарубежный прибор | Тип прибора | Отечественный аналог |

| SN74242 | Цифровая ИМС ТТЛ–типа | К155ИП6 |

| SN74243 | Цифровая ИМС ТТЛ–типа | К155ИП7 |

| SN74244 | Цифровая ИМС ТТЛ–типа | К555АП5 |

| SN74245 | Цифровая ИМС ТТЛ–типа | К155АП6 |

| SN74LS266 | Цифровая ИМС ТТЛШ–типа | — |

| SN74273 | Цифровая ИМС ТТЛ–типа | К555ИР22 |

| SN74279 | Цифровая ИМС ТТЛ–типа | К155ТР2 |

| SN74283 | Цифровая ИМС ТТЛ–типа | К155ИМ6 |

| TBA820M | ИМС усилителя мощности | К174УН4 |

| TL082 | ИМС сдвоенного операционного усилителя | КР574УД2 |

| IN4001 | Диод | КД103, КД226А |

| IN4148 | Диод | КД522А |

| 2N3053 | Биполярный транзистор | КД603Д, КД608Б |

| 2N3703 | Биполярный транзистор | КТ313Б, КТ3107А |

| 2N3705 | Биполярный транзистор | КТ645А, КТ3117А |

| 741 | ИМС операционного усилителя | К140УД7 |

| 78H05 | ИМС стабилизатора напряжения | К142ЕН5 |

| 7805 | ИМС стабилизатора напряжения | К142ЕН5 |

| 7216A | Универсальный счетчик со схемой управления светодиодами | — |

2020-01-14

2020-01-14 553

553