Память типа ROM

ОРГАНИЗАЦИЯ ОП.

Оперативная память — это рабочая область для процессора компьютера.

В компьютерах используются запоминающие устройства трех основных типов:

1. ROM (Read Only Memory) – ПЗУ, не способное выполнять операцию записи данных.

2. DRAM (Dynamic Random Access Memory) - динамическое запоминающее устройство с произвольным порядком выборки.

3. SRAM (Static RAM) - статическая оперативная память.

В памяти типа ROM (Read Only Memory), или ПЗУ (постоянное запоминающее устройство), данные можно только хранить, изменять их нельзя. Именно поэтому такая память используется только для чтения данных. ROM также часто называется энергонезависимой памятью, потому что любые данные, записанные в нее, сохраняются при выключении питания. Поэтому в ROM помещаются команды запуска ПК, т.е. программное обеспечение, которое загружает систему.

Динамическая оперативная память (Dynamic RAM — DRAM) используется в большинстве систем оперативной памяти современных ПК. Основное преимущество памяти этого типа состоит в том, что ее ячейки упакованы очень плотно, т.е. в небольшую микросхему можно упаковать много битов, а значит, на их основе можно построить память большой емкости. Ячейки памяти в микросхеме DRAM — это крошечные конденсаторы, которые удерживают заряды. Наличием или отсутствием зарядов кодируются биты. Проблемы, связанные с памятью этого типа, вызваны тем, что она динамическая, т.е. должна постоянно регенерироваться, так как в противном случае электрические заряды в конденсаторах памяти будут “стекать” и данные будут потеряны.

Кэш"память " SRAM

Память SRAM в отличие от динамической оперативной памяти (DRAM), для сохранения ее содержимого не требует периодической регенерации. SRAM имеет более высокое быстродействие, чем DRAM, и может работать на той же частоте, что и современные ЦП. Однако для хранения каждого бита в конструкции SRAM используется кластер из шести транзисторов. Использование транзисторов без каких либо конденсаторов означает, что нет необходимости в регенерации.

Оперативная память всегда строится из отдельных модулей памяти, которые имеют свое собственное электронное обрамление (т.е. устройства, обеспечивающие запись, выборку, чтение). Структура модуля памяти определяется способом организации ОП (способ адресации). Существует 3 разновидности организации оперативной памяти:

Оперативная память всегда строится из отдельных модулей памяти, которые имеют свое собственное электронное обрамление (т.е. устройства, обеспечивающие запись, выборку, чтение). Структура модуля памяти определяется способом организации ОП (способ адресации). Существует 3 разновидности организации оперативной памяти:

1) адресная память

2) память со стековой организацией

3) ассоциативная организация ОП

С точки зрения функционального построения, любое ЗУ этого типа представляет собой некоторый массив элементов памяти. Структурные элементы памяти образуют ячейки памяти. Ширина ячеек – ширина выборки из памяти.

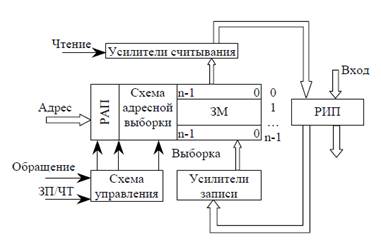

1) В адресной памяти, размещение и поиск информации в запоминающем массиве, базируется на основе номера (адреса). Массив запоминания элементов содержит N n-разрядных слов, которые пронумерованы (0…N-1). Электронное обрамление включает в себя регистры для хранения адреса памяти, регистр информации (само слово), схемы адресной выборки (адресации), разрядные усилители для чтения и записи.

Цикл работы памяти инициируется сигналом обращения к памяти и операцией (ЗП/ЧТ). При инициировании обращения производится дешифрация адреса схемы адресной выборки. Если задана операция чтения, то активизируется усилитель считывания и информация через него предается в регистр информации памяти. Если память требует динамической регенерации, то после регистра информации памяти все поступает в регистр адреса памяти. Если происходит операция записи, то активизируется усилитель записи, который обеспечивает запись из регистра информации памяти в нужное место памяти.

2) В стековой организации запись нового слова, поступившего с входной информационной шиной, производится в верхнюю (нулевую) ячейку- которая является выходной информационной шиной, при этом все ранее записанные слова (включая слово в ячейке 0) сдвигаются вниз, в соседние ячейки, номера которых на единицу больше. Считывание возможно только из верхней (нулевой) ячейки памяти. Основной режим – это считывание с удалением. Таким образом, ячейка N-1 – дно стека, а ячейка 0 – вершина.

Обычно аппаратный стек снабжается счетчиком стека СчСт, показывающим общее количество занесенных в память слов (СчСт = 0 – стек пустой). При заполнении стека полностью он запрещает дальнейшие операции записи. Стековая организация данных возможна и на обычной адресной памяти с произвольным обращением (программный стек). Для организации стека в этом случае необходима еще одна ячейка памяти (регистр), в которой всегда хранится адрес вершины стека и которая называется указателем стека. Обычно в качестве указателя стека используют один из внутренних регистров процессора. Кроме этого, требуется соответствующее программное обеспечение.

В отличие от аппаратного стека данные, размещенные в программном стеке, при записи нового числа или считывании не перемещаются. Запись каждого нового слова осуществляется в ячейку памяти, следующую по порядку за той, адрес которой содержится в указателе стека. При этом содержимое указателя стека увеличивается на единицу. Таким образом, в программном стеке перемещаются не данные, а вершина стека. При считывании слова из стека происходит обратный процесс. Слово считывается из ячейки, адрес которой находится в указателе стека, после чего содержимое указателя стека уменьшается на единицу.

3) В ассоциативной памяти поиск информации происходит не по адресу, а по ее содержанию. Под содержанием информации в данном случае понимается побитовый состав записанного двоичного слова. При этом ассоциативный запрос также представляет собой двоичный код с определенным побитовым составом. Поиск по ассоциативному запросу происходит параллельно во времени для всех ячеек ЗМ и представляет собой операцию сравнения содержимого разрядов регистра запроса с содержимым соответствующих разрядов ячеек памяти. Для организации такого поиска все ЗЭ ЗМ снабжены однобитовыми процессорами, поэтому в ряде случаев память такого типа рассматривают как многопроцессорную систему.

Ассоциативный поиск можно реализовать и в компьютере с обычной адресной памятью, последовательно вызывая записанные в ячейки памяти слова в процессор и сравнивая их с некоторым ассоциативным признаком (шаблоном).

Контроль четности и коды коррекции ошибок (ECC)

Факторы программных ошибок в памяти:

Скачки в энергопотреблении или шум на линии.

Использование неверного типа или параметра быстродействия памяти.

Статические разряды.

Ошибки синхронизации.

Тепловыделение.

Для повышения отказоустойчивости в компьютерах применяются методы контроля четности и коды коррекции ошибок (ECC).

В методе контроля четности информация в банках памяти хранится фрагментами по 9 бит, причем восемь из них (составляющих один байт) предназначены собственно для данных, а девятый является битом четности (parity). Использование девятого бита позволяет схемам управления памятью на аппаратном уровне контролировать целостность каждого байта данных. Если обнаруживается ошибка, работа компьютера останавливается и на экран выводится сообщение о неисправности. Если вы работаете на компьютере под управлением Windows или OS/2, то при возникновении ошибки контроля четности сообщение, возможно, не появится, а просто произойдет блокировка системы.

Технология контроля четности не позволяет исправлять системные ошибки, однако дает возможность их обнаружить пользователю компьютера, что имеет следующие преимущества:

контроль четности оберегает от последствий проведения неверных вычислений на базе некорректных данных;

контроль четности точно указывает на источник возникновения ошибок, помогая разобраться с проблемой и улучшая степень эксплуатационной надежности компьютера.

Коды коррекции ошибок (Error Correcting Code — ECC) позволяют не только обнаружить ошибку, но и исправить ее в одном разряде. В случае ошибки в одном разряде ПК может работать без прерывания, причем данные не будут искажены. Коды коррекции ошибок в большинстве ПК позволяют только обнаруживать, но не исправлять ошибки в двух разрядах. Данный тип ECC получил название SEC_DED (single_bit error_correction double_bit error detection — одноразрядная коррекция, двухразрядное обнаружение ошибок). В кодах коррекции ошибок этого типа для каждых 32 бит требуется дополнительно семь контрольных разрядов при 4_байтовой и восемь — при 8_байтовой организации (64_разрядные процессоры Athlon/Pentium). Для использования кодов коррекции ошибок необходим контроллер памяти, вычисляющий контрольные разряды при операции записи в память. При чтении из памяти такой контроллер сравнивает прочитанные и вычисленные значения контрольных разрядов и при необходимости исправляет испорченный бит (или биты).

2014-02-02

2014-02-02 2103

2103