Время выполнения команды МП зависит от типа команды и продолжается от 1 до 5 машинных циклов (M). Длительность машинного цикла может составлять от 3 до 5 машинных тактов (Т,). Длительность машинного такта равна периоду тактовой частоты, задаваемой частотой фаз CLKI, CLK.2 генератора тактов.

Операции, выполняемые МП в машинном цикле, определяются 8-разрядной информацией, характеризующей состояние внутренних узлов микропроцессора. Этот байт состояния называется также словом состояния процессора и выдается на шину данных МП в такте Т2 каждого машинного цикла (табл. 1.2, табл. 1.3). Байт состояния может использоваться для формирования управляющих сигналов обращения к ЗУ, УВВ, а также при организации различных режимов работы микропроцессорной системы.

Таблица 1.2. Сигналы состояния микропроцессора

| Обозначение сигнала | Разряд шины данных | Назначение сигнала |

| INTA | DO | Подтверждение прерывания; используется для стробирования приема команды RST в МП из схемы прерывания |

| WO | Dl | Запись; L-уровень сигнала указывает на запись данных в ЗУ или ВУ; Н - уровень сигнала – на запись в микропроцессоре |

| STACK | D2 | Стек; Н- уровень сигнала указывает, что на шине адреса установлено содержимое SP |

| HLTA | D3 | Подтверждение останова; Я-уровень сигнала указывает на переход МП в состояние останова |

| OUT | D4 | Ввод; Н-уровень сигнала указывает, что на шине адреса установлен код ВУ и можно осуществить ввод данных в МП по сигналу DBIIN = 1 |

| MI | D5 | Н-уровень сигнала указывает, что МП принимает первый байт команды |

| INP | D6 | Ввод; Н-уровень сигнала указывает, что на шине адреса установлен код ВУ и можно осуществить ввод данных в МП по сигналу DBIN= 1 |

| MEMR | D7 | Чтение; Н-уровень сигнала указывает, что осуществляется чтение содержимого ЗУ по адресу, установленному на шине адреса |

Таблица 1.3. Разновидности машинных циклов микропроцессора

| Машинный цикл | Обозначение сигнала слова-состояния процессора | |||||||

| INTA | WO | STACK | HLTA | OUT | М1 | INP | MEMR | |

| Цикл M1 - выборка команды | ||||||||

| Цикл чтения из ЗУ записи в ЗУ чтения из стека | ||||||||

| Цикл записи в стек | ||||||||

| Цикл ввода Цикл вывода Цикл прерывания Цикл останова Цикл прерывания при останове |

Для фиксации слова-состояния процессора можно применить внешний 8-разрядный регистр. временная диаграмма и схема записи слова состояния в многорежимный буферный регистр К589ИР12 приведена на рис.1.3. Запись осуществляется сигналом CLKI в такте Т2 с использованием сигнала SYNC.

|

Рис.1.3.

Цикл выборки команды M1 является первым и обязательным машинным циклом всех команд МП.

Управление функционированием микропроцессорной системы на базе МП КР580ИК80А осуществляется генерацией управляющих сигналов по двум шинам: по шине управления собственно МП (WR, DBIN, INTE,...) в каждом такте работы микропроцессора Ti), по шине данных путем генерации слова-состояния процессора (PSW) в каждом машинном цикле M.

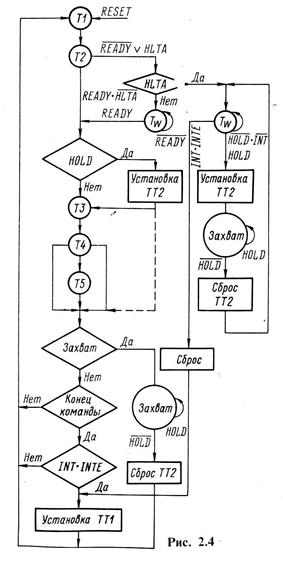

Диаграмма состояний МП при выполнении типового машинного цикла с внешними управляющими сигналами READY, HOLD, INT и сигналом HLTA формируемым по команде HLT, приведена на рис. 1.4.

|

Рис.1.4

Рис.1.4

На диаграмме состояний МП (рис. 1.5) можно выделить следующие особенности его функционирования.

1. Любой машинный цикл включает, по крайней мере, три такта: Т1, Т2 и ТЗ. Такты Т4, Т5 не обязательны и применяются для внутренних операций МП.

2. Подача сигнала H-уровня на вход RESET длительностью не менее трех периодов тактовой частоты устанавливает МП в исходное состояние. В программный счетчик заносятся нули, а схема управления начинает формировать такт Т1 машинного цикла выборки команды М1.

3. В такте Т2 микропроцессор анализирует сигналы READY, HLTA и HOLD. При наличии на входе READY напряжения H-уровня и отсутствии сигналов HLTA и HOLD микропроцессор переходит к такту ТЗ. В зависимости от вида выполняемой команды машинный цикл завершается после выполнения тактов ТЗ, Т4 или Т5. Если выполнение команды не закончено, то МП переходит к следующему машинному циклу команды, начиная с такта Т1. В конце каждой команды МП проверяет наличие запроса прерывания. Если H -уровень сигнала находится на входе INT и триггер разрешения прерывания установлен (INTE= 1), то МП переключает триггер прерывания (ТТ1) и приступает к выполнению машинного цикла прерывания, начиная с такта Т1.

При наличии на входе READ Y сигнала L-уровня в такте Т2 микропроцессор переходит в состояние ожидания (Тw), пока не появится сигнал READ Y от внешнего устройства.

4. В такте Т2 анализируется наличие сигналов установки внутреннего триггера захвата (ТТ2). Однако переход к режиму захвата до такта ТЗ не разрешается, потому что МП должен закончить обмен с внешним регистром в начале такта ТЗ. По окончании состояния захвата МП всегда переходит к такту Т1 следующего машинного цикла. Если текущий машинный цикл содержит такты Т4 и Т5, то они совмещаются с режимом захвата.

5. МП переходит в состояние останова при наличии сигнала HLTA, формируемого во втором машинном цикле команды HLT, при этом внутренние шины адреса и данные переводятся в высокоимпедансное состояние, появляется H-уровень напряжения на выходе WAIT- выполнение программы прекращается. Из состояния останова МП выходит по сигналу сброса RESET или по сигналу запроса прерывания INT при установленном триггере разрешения прерывания (I N ТЕ = 1). В состоянии останова МП может переходить в режим захвата, если поступает сигнал напряжения Н- уровня на вход HOLD.

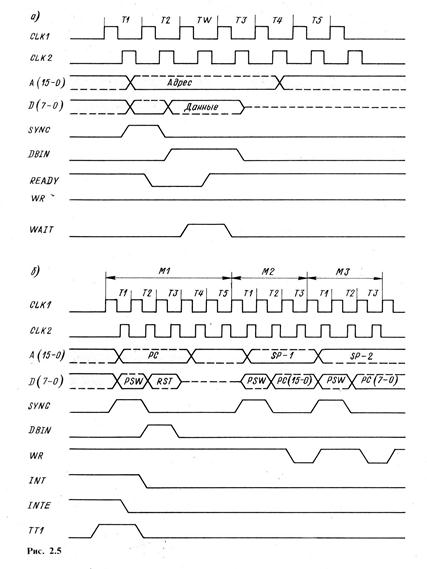

На рис. 1.5, а изображена временная диаграмма приема информации в микропроцессор в цикле чтения из ЗУ и цикле ввода. В такте Т1 по каналу данных передается информация о состоянии текущего цикла; в канал адреса передается адрес ячейки памяти, из которой считывается информация в текущем цикле; формируется сигнал Н-уровня SYNC. В такте Т2 микропроцессор устанавливает сигнал высокого уровня DBIN, а канал данных принимает информацию с шины данных по импульсу синхронизации CLK2 при условии, что здесь имеется сигнал высокого уровня READY. Если необходимо согласовывать по времени работу ЗУ и МП, то можно увеличить длительность сигнала приема DBIN подачей L-уровня сигнала READY. Тогда МП переходит в состояние ожидания и выдает сигнал H-уровня WAIT, а канал адреса, канал данных и сигнал DBIN не изменяют своего состояния. По сигналу READY Н-уровня МП переходит в такт ТЗ, изменяются уровни сигналов WAIT u DBIN; канал данных переводится в высокоимпедансное состояние. В такте Т4 информация в адресном канале изменяется и становится неопределенной до начала следующего цикла. В течение всего цикла приема информации сигнал WR сохраняет H-уровень напряжения. Временная диаграмма основных сигналов при выдаче информации из МП для цикла записи в ЗУ и цикла вывода отличается отсутствием сигнала DBIN и формированием после такта Т2 сигнала WR L-уровня. В такте Т2 микропроцессор выдает информацию на шину данных для записи в ЗУ или УВВ.

Микропроцессор начинает обработку запроса прерывания, поступившего на вход INT, если внутренний триггер разрешения прерывания установлен в состояние (INТЕ = 1). Устанавливать или сбрасывать триггеры разрешения прерывания можно программно, с помощью команд ЕI(i) (разрешение прерывания) или DI (запрещение прерывания). Если запрос прерывания принят, то МП начинает 'выполнение машинного цикла прерывания. В такте Т1 этого цикла на шину адреса поступает содержимое программного счетчика, а на шину данных - слово-состояние процессора (рис. 1.5, б). Слово-состояние цикла прерывания содержит единицы в разрядах DO (INТА), DI (WO) и D5 (MI) (см. табл. 1.1). Сигнал подтверждения прерывания INTA используется в микропроцессорной системе для квитирования микропроцессором приема запроса прерывания. В такте Т1 по сигналу CLK2 также сбрасывается триггер разрешения прерывания (INTE=0), что приводит к запрету приема последующих запросов прерываний. В такте Т2 по сигналу DBIN обычно вводится код операции из памяти, но слово-состояние цикла прерывания содержит в разряде D7 (MEMR) нуль-запрет на чтение из памяти, поэтому код операции должен сформировать внешнее устройство. В такте Т2 сбрасывается также внутренний триггер прерывания, а содержимое PC не изменяется. В такте ТЗ команда RST, сформированная ВУ, с шины данных передается в регистр команд МП, а в тактах Т4 и Т5 она дешифрируется. По команде RST содержимое PC (адрес возврата) запоминается в стеке, а в PC заносится адрес первой команды программы обработки прерывания, определяемый номером команды RST. Запоминание адреса возврата из прерывания в стеке выполняется в циклах М2 и МЗ - запись в стек.

|

Рис.1.5.

Рис.1.5.

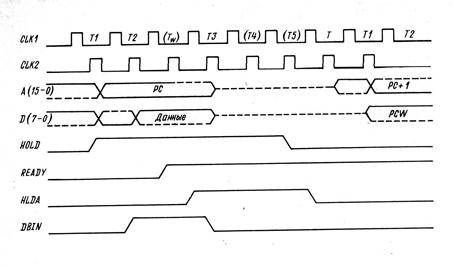

Для обмена информацией с быстродействующими внешними устройствами (ВУ) используется режим прямого доступа к памяти, в котором выполнение программы приостанавливается, буферы адреса и данных МП переходят в высокоимпедансное состояние, и контроллер прямого доступа к памяти организует обмен данными между ВУ и памятью микроЭВМ. Временная диаграмма режима прямого доступа к памяти в цикле чтения из ЗУ изображена на рис. 1.6. При наличии сигнала READY H-уровня МП переходит в состояние захвата в такте ТЗ. Для режима прямого доступа в цикле записи в ЗУ при наличии сигнала READY переход МП в состояние захвата осуществляется после такта ТЗ.

Рис. 1.6.

2014-02-24

2014-02-24 2972

2972