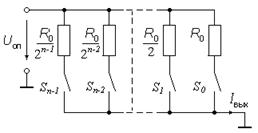

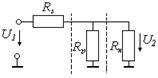

ЦАП с суммированием весовых токов. Большинство схем параллельных ЦАП основано на суммировании токов, сила каждого из которых пропорциональна весу цифрового двоичного разряда, причем должны суммироваться только токи разрядов, значения цифры в которых равны 1. Пусть, например, требуется преобразовать двоичный четырехразрядный код в аналоговый сигнал тока. У четвертого, старшего значащего разряда (СЗР) вес будет равен 23=8, у третьего разряда - 22=4, у второго - 21=2 и у младшего (МЗР) - 20=1. Если вес МЗР IМЗР=1 мА, то IСЗР=8 мА, а максимальный выходной ток преобразователя Iвых.макс=15 мА и соответствует коду 11112. Понятно, что коду 10012, например, будет соответствовать Iвых=9 мА и т.д. Следовательно, требуется построить схему, обеспечивающую генерацию и коммутацию по заданным законам точных весовых токов. Простейшая схема, реализующая указанный принцип, приведена на рис.13.4.

.

.

Рис.13.4. Простейшая схема ЦАП с суммированием

весовых токов

Сопротивления резисторов выбирают так, чтобы при замкнутых ключах через них протекал ток, соответствующий весу разряда. Ключ должен быть замкнут тогда, когда соответствующий ему бит входного слова равен единице. Выходной ток определяется соотношением

.

.

При высокой разрядности ЦАП токозадающие резисторы должны быть согласованы с высокой точностью. Наиболее жесткие требования по точности предъявляются к резисторам старших разрядов, поскольку разброс токов в них не должен превышать тока младшего разряда. Поэтому разброс сопротивления в i -м разряде должен быть меньше, чем

ΔR / R=2- i.

Из этого условия следует, что разброс сопротивления резистора, например, в четвертом разряде не должен превышать 3%, а в 10-м разряде - 0,05% и т.д.

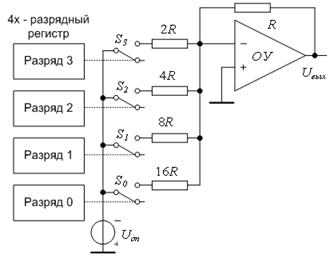

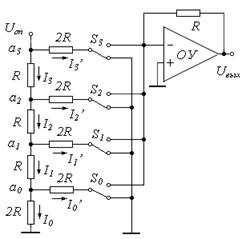

Суммирование весовых токов наиболее целесообразно выполнить с помощью операционного усилителя по рис.13.5. Здесь представлена базовая структурная схема 4-разрядного ЦАП (так называемая схема на взвешенных резисторах). Четыре бита, фиксируемые в регистре, управляют состоянием четырёх ключей и обеспечивают 16 различных комбинаций. ОУ включён по схеме сумматора. При замыкании одного из ключей выходное напряжение ЦАП определяется произведением опорного напряжения Uоп на отношение сопротивлений резистора обратной связи ОУ к резистору матрицы, находящемуся в цепи данного ключа.

Рис.13.5. Базовая структурная

схема четырёхразрядного ЦАП

Если, например, замкнут ключ, соответствующий старшему значащему разряду СЗР регистра (при установке в триггере этого разряда логической 1), то выходное напряжение Uвых= – (R/2R)Uоп = –Uоп / 2. При установке уровня сигнала 1 в разряде 1 получим Uвых = –(R/8R) Uоп= –Uоп/8. Замыкание каждого следующего ключа (в направлении увеличения веса разрядов) вызывает прирост выходного напряжения, вдвое превышающий результат замыкания предыдущего ключа. При замыкании нескольких ключей результирующее выходное напряжение определяется суммой вкладов от каждого замкнутого ключа. Например, при установке логической 1 в разрядах 3 и 1 получаем выходное напряжение Uвых= –(Uоп / 2 + Uоп / 8). Таким образом, можно получить 16 различных дискретных уровней выходного напряжения, соответствующих 16 различным двоичным комбинациям на входе ЦАП. Соотношения сопротивлений резисторов должны быть выдержаны с высокой точностью для обеспечения необходимой линейности преобразования входного кода в выходное напряжение.

Конструирование такого ЦАП на одном кристалле вызывает определённые трудности. Это объясняется слишком большим диапазоном величин сопротивлений входящих в него резисторов. В рассматриваемом 4-разрядном ЦАП сопротивление резистора в цепи младшего значащего разряда МЗР должно быть в 16 раз больше сопротивления резистора обратной связи. В общем случае для n –разрядного преобразователя нужны n +1 резистор, а сопротивление резистора в цепи МЗР должно быть в 2 n раз больше сопротивления резистора обратной связи. Реальное значение R, которое можно получить для резистора в рамках интегральной микросхемы, составляет 5-10 КОм. А в 8-разрядном ЦАП требуется 9 резисторов с сопротивлением от 5 КОм до 1.28 МОм (256 × 5 кОм), в то время как в 12-разрядном – 13 резисторов с нереальным диапазоном сопротивлений вплоть до 20.48 МОм.

Рассмотренная схема при всей ее простоте обладает целым букетом недостатков. Во-первых, при различных входных кодах ток, потребляемый от источника опорного напряжения (ИОН), будет различным, а это повлияет на величину выходного напряжения ИОН. Во-вторых, значения сопротивлений весовых резисторов могут различаться в тысячи раз, а это делает весьма затруднительной реализацию этих резисторов в полупроводниковых ИМС с необходимым классом точности. Кроме того, сопротивление резисторов старших разрядов в многоразрядных ЦАП могут быть соизмеримы с сопротивлением замкнутого ключа, а это приведет к погрешности преобразования. В-третьих, в этой схеме к разомкнутым ключам прикладывается значительное напряжение, что усложняет их построение.

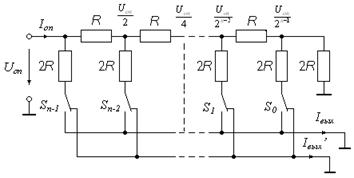

Эти недостатки устранены в схеме ЦАП AD7520 (отечественный аналог 572ПА1), разработанном фирмой Analog Devices в 1973 г., которая в настоящее время является по существу промышленным стандартом (по ней выполнены многие серийные модели ЦАП). Указанная схема представлена на рис.13.6. В качестве ключей здесь исполь-

Рис.13.6. Схема ЦАП с переключателями и матрицей R -2 R посто-

янного импеданса

зуются МОП-транзисторы.

В этой схеме задание весовых коэффициентов ступеней преобразователя осуществляют посредством последовательного деления опорного напряжения с помощью резистивной матрицы R -2 R постоянного импеданса. Основной элемент такой матрицы представляет собой делитель напряжения (рис.13.7), который должен удовлетворять следующему условию: если он нагружен на сопротивление Rн, то его входное сопротивление Rвх также должно принимать значение Rн. Коэффициент ослабления цепи a = U2 / U1 при этой нагрузке должен иметь заданное значение. При выполнении этих условий получаем следующие выражения для сопротивлений:

Рис.13.7. Построение ступени матрицы по-

стоянного импеданса

.

.

При двоичном кодировании a =0,5. Если положить Rн =2 R, то Rs = R и Rp =2 R в соответствии с рис.13.6.

Поскольку в любом положении переключателей Si они соединяют нижние выводы резисторов с общей шиной схемы, источник опорного напряжения нагружен на постоянное входное сопротивление Rвх = R. Это гарантирует неизменность опорного напряжения при любом входном коде ЦАП.

Согласно рис.13.6, выходные токи схемы определяются соотношениями

;

;  ,

,

а входной ток

.

.

Поскольку нижние выводы резисторов 2 R матрицы при любом состоянии переключателей Si соединены с общей шиной схемы через низкое сопротивление замкнутых ключей, напряжения на ключах всегда небольшие, в пределах нескольких милливольт. Это упрощает построение ключей и схем управления ими и позволяет использовать опорное напряжение из широкого диапазона, в том числе и различной полярности. Поскольку выходной ток ЦАП зависит от Uоп линейно, преобразователи такого типа можно использовать для умножения аналогового сигнала (подавая его на вход опорного напряжения) на цифровой код. Такие ЦАП называют перемножающими (MDAC).

На рис.13.8 показана схема ЦАП на резистивной матрице R-2R cо сложением весовых значений токов операционным усилителем.

На рис.13.8 показана схема ЦАП на резистивной матрице R-2R cо сложением весовых значений токов операционным усилителем.

Рис.13.8. ЦАП на сетке R -2 R

Для доказательства возможности использования такой резисторной матрицы в схеме ЦАП рассмотрим величины токов в параллельных ветвях к суммирующей точке ОУ.

Потенциалы средней точки переключателей S0,…S3 вне зависимости от положения подвижного элемента (верхнее или нижнее) остаются одинаковыми и равными потенциалу земли, так как в нижнем положении они подключаются к клемме “земля”, а в верхнем положении они подключаются к суммирующей точке операционного усилителя ОУ, потенциал которой по условиям работы ОУ близок к потенциалу земли. Отсюда следует, что переключения Si не вызывают изменения картины токов в резисторной матрице R- 2 R.

Рассмотрим картину токов в нижнем плече матрицы – точка a0. К ней подключены два резистора с одинаковым номиналом 2 R, то есть токи I0 и I0’ равны. Общее же сопротивление этих двух параллельно включенных резисторов R0об = (2R*2R)/(2R+2R) = R.

По закону Кирхгофа ток I1 = I0 + I0’ = 2I0’. Сопротивление вертикального участка цепи между точкой а 1 и землёй равняется R1 = R + R0об = R + R = 2R, то есть равно сопротивлению горизонтального участка от этой же точки. Следовательно, протекающие по ним токи также равны: I1 = I1’. Так как I1 = 2 I0’, то и I1’ = 2I0’. Общее же сопротивление резисторов, подключенных к точке а 1, по отношению к земле R1об = (R1*2R)/(R1+2R) = (2R*2R)/(2R+2R) = R.

Рассуждая аналогично по отношению к точкам а 2, а 3, придём к соотношениям: I2’ = 2I1’ = 4I0’, I3’ = 2I2’ = 8I0’. Отсюда следует, что отношения величин токов в соседних параллельных ветвях матрицы кратны двум; их соотношения соответствуют коэффициентам 8-4-2-1, как это имеет место в схеме, показанной на рис.13.5. Поэтому схема на рис.13.8 реализует преобразование цифры в аналог по двоичной системе счисления.

Точность этой схемы снижает то обстоятельство, что для ЦАП, имеющих высокую разрядность, необходимо согласовывать сопротивления R0 ключей на полевых транзисторах с разрядными токами. Особенно это важно для ключей старших разрядов. Например, в 10-разрядном ЦАП AD7520 ключевые МОП-транзисторы шести старших разрядов сделаны разными по площади и их сопротивление R0 нарастает согласно двоичному коду (20, 40, 80, …, 640 Ом). Таким способом уравниваются (до 10 мВ) падения напряжения на ключах первых шести разрядов, что обеспечивает монотонность и линейность переходной характеристики ЦАП. 12-разрядный ЦАП 572ПА2 имеет дифференциальную нелинейность до 0,025% (1 МЗР).

ЦАП на МОП ключах имеют относительно низкое быстродействие из-за большой входной емкости МОП-ключей. Тот же 572ПА2 имеет время установления выходного тока при смене входного кода от 000...0 до 111...1, равное 15 мкс. 12-разрядный DAC7611 фирмы Burr-Braun имеет время установления выходного напряжения 10 мкс. В то же время ЦАП на МОП-ключах имеют минимальную мощность потребления. Тот же DAC7611 потребляет всего 2,5 мВт. В последнее время появились модели ЦАП рассмотренного выше типа с более высоким быстродействием. Так 12-разрядный AD7943 имеет время установления тока 0,6 мкс и потребляемую мощность всего 25 мкВт. Малое собственное потребление позволяет запитывать такие микромощные ЦАП прямо от источника опорного напряжения. При этом они могут даже не иметь вывода для подключения ИОН, например, AD5321.

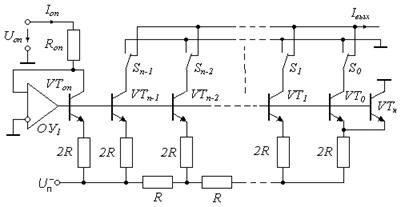

ЦАП на источниках тока обладают более высокой точностью. В отличие от предыдущего варианта, в котором весовые токи формируются резисторами сравнительно небольшого сопротивления и, как следствие, зависят от сопротивления ключей и нагрузки, в данном случае весовые токи обеспечиваются транзисторными источниками тока, имеющими высокое динамическое сопротивление. Упрощенная схема ЦАП на источниках тока приведена на рис.13.9.

Рис.13.9. Схема ЦАП на

источниках тока

Весовые токи формируются с помощью резистивной матрицы. Потенциалы баз транзисторов одинаковы, а чтобы были равны и потенциалы эмиттеров всех транзисторов, площади их эмиттеров делают различными в соответствии с весовыми коэффициентами. Правый резистор матрицы подключен не к общей шине, как на схеме рис.13.4, а к двум параллельно включенным одинаковым транзисторам VT0 и VTн, в результате чего ток через VT0 равен половине тока через VT1. Входное напряжение для резистивной матрицы создается с помощью опорного транзистора VTоп и операционного усилителя ОУ1, выходное напряжение которого устанавливается таким, что коллекторный ток транзистора VTоп принимает значение Iоп. Выходной ток для n -разрядного ЦАП

.

.

Характерными примерами ЦАП на переключателях тока с биполярными транзисторами в качестве ключей являются 12-разрядный 594ПА1 с временем установления 3,5 мкс и погрешностью линейности не более 0,012% и 12-разрядный AD565, имеющий время установления 0,2 мкс при такой же погрешности линейности. Еще более высоким быстродействием обладает AD668, имеющий время установления 90 нс и ту же погрешность линейности. Из новых разработок можно отметить 14-разрядный AD9764 со временем установления 35 нс и погрешностью линейности не более 0,01%. В качестве переключателей тока Si часто используются биполярные дифференциальные каскады, в которых транзисторы работают в активном

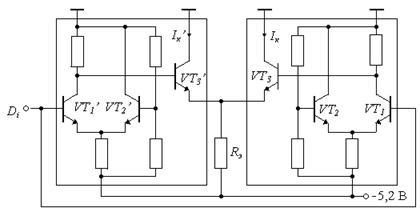

Рис.13.10. Переключатель тока на дифференциаль-

ных усилителях

режиме. Это позволяет сократить время установления до единиц наносекунд. Схема переключателя тока на дифференциальных усилителях приведена на рис.13.10.

Дифференциальные каскады VT1-VT3 и VT'1-VT'3 образованы из стандартных ЭСЛ вентилей. Ток Iк, протекающий через вывод коллектора выходного эмиттерного повторителя, является выходным током ячейки. Если на цифровой вход Di подается напряжение высокого уровня, то транзистор VT3 открывается, а транзистор VT'3 закрывается. Выходной ток определяется выражением

.

.

Точность значительно повышается, если резистор Rэ заменить источником постоянного тока, как в схеме на рис.13.9. Благодаря симметрии схемы существует возможность формирования двух выходных токов – прямого и инверсного. Наиболее быстродействующие модели подобных ЦАП имеют входные ЭСЛ-уровни. Примером может служить 12-ти разрядный МАХ555, имеющий время установления 4 нс до уровня 0,1%. Поскольку выходные сигналы таких ЦАП захватывают радиочастотный диапазон, они имеют выходное сопротивление 50 или 75 Ом, которое должно быть согласовано с волновым сопротивлением кабеля, подключаемого к выходу преобразователя.

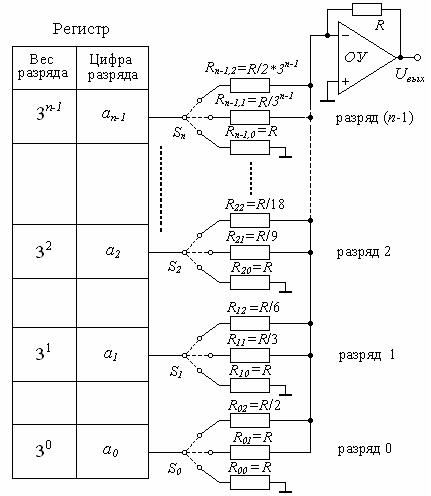

Принципы построения ЦАП для троичной системы счисления. Познавательный интерес представляет возможность выполнения цифро-аналоговых преобразований для систем счисления с любым основанием. В общем случае ЦАП находит аналоговый эквивалент заданной кодовой комбинации последовательным выполнением операций сложения произведений веса каждого разряда на соответствующую цифру в этом разряде. Отсюда основой построения ЦАП является сумматор на операционном усилителе. Для типовой схемы ЦАП на взвешенных резисторах по рис.13.5 эквивалентом веса разряда является величина тока, протекающая через тот или иной резистор на суммирующую точку операционного усилителя. Величины токов задаются значениями сопротивлений, номиналы которых уменьшаются в два раза при переходе от младшего разряда к последующему более старшему разряду. Если бит соответствующего разряда равен единице, то ключ Si подсоединяет цепь тока к суммирующей точке ОУ, в противном случае при нулевом значении бита цепь тока этого разряда разорвана.

Этот принцип построения преобразования следует применить и при разработке ЦАП для троичной системы счисления. Принципиальная схема устройства представлена на рис.13.11.

Этот принцип построения преобразования следует применить и при разработке ЦАП для троичной системы счисления. Принципиальная схема устройства представлена на рис.13.11.

Рис.13.11. Принципиальная схема ЦАП для троичной системы счи-

сления

В системе счисления с основанием n используются цифры от нуля до (n-1), то есть в нашем случае 0,1,2. Преобразуемый код заносится в регистр ЦАП, и вес разряда при переходе от нулевого младшего к последующему старшему определяется последовательностью 30, 31, … 3n-1. В каждом i-ом разряде преобразуемого кода может находиться одна из цифр набора 0,1,2 при общем количестве разрядов n. В зависимости от величины цифры младшего нулевого разряда переключатель S0 устанавливается в одно из трёх положений: нижнее (цифра 0), среднее (цифра 1) и верхнее (цифра 2). Совокупность цифр разряда реализуется набором из трёх резисторов – R00, R01, R02 (здесь и далее в индексах резисторов первая цифра указывает на номер реализуемого разряда, второй символ определяет моделируемую цифру набора). Нулевое значение младшей цифры моделируется тем, что выход нижнего резистора группы R00=R подсоединён к земле. Величины остальных двух резисторов группы цифр младшего разряда устанавливаются из следующих соображений. Наличие единичного сигнала на среднем резисторе R01 группы младшего разряда, моделирующего цифру 1, должно вызывать появление на выходе ОУ напряжения, эквивалентного единице. Следовательно, коэффициент передачи ОУ по этому каналу должен быть равен единице, и тогда на основании выражения (5.3) R01=R. По аналогии наличие единичного сигнала на резисторе R02 группы младшего разряда, моделирующего цифру 2, должно вызывать появление на выходе ОУ напряжения, эквивалентного двум. Поэтому коэффициент передачи по этому каналу должен быть равен двум, и на основании (5.3) R02=R/2.

Переход к моделированию цифр первого разряда должен учитывать вес этих цифр, равный 31. Здесь и далее ситуация с резисторами R10, R20, …остаётся неизменной – они подключены к земле через резистор R. Сигнал на входе резистора R11 должен приводить к появлению на выходе ОУ напряжения, эквивалентного 31, поэтому коэффициент передачи канала должен быть равен трём, и R11=R/3. Сигнал на входе резистора R12 должен вызывать появление на выходе ОУ напряжения, эквивалентного шести. Тогда R12=R/6.

Далее всё повторяется с увеличением весов последующих разрядов в три раза и снижением сопротивлений резисторов в три и шесть раз. Получили схему ЦАП для троичной системы счисления на взвешенных резисторах (рис.13.11), которая полностью повторяет недостатки аналогичной схемы для двоичной системы счисления.

Контрольные вопросы

1. Назначение, классификация цифро-аналоговых преобразователей, основные их характеристики?

2. Последовательные ЦАП: с широтно-импульсной модуляцией, на переключаемых конденсаторах – схемные реализации, их работа, основные соотношения, применение?

3. Параллельные ЦАП: преобразователи с суммированием весовых токов – схемное построение, основные соотношения, практическая реализация, метрологические характеристики?

4. Параллельные ЦАП: преобразователи на матрице R-2R - схемное построение, основные соотношения, практическая реализация, метрологические характеристики?

5. ЦАП на источниках тока - схемное построение, основные соотношения, практическая реализация, метрологические характеристики?

6. Принципы построения ЦАП для троичной системы счисления?

Лекция14. Аналого-цифровые

2015-02-27

2015-02-27 5799

5799