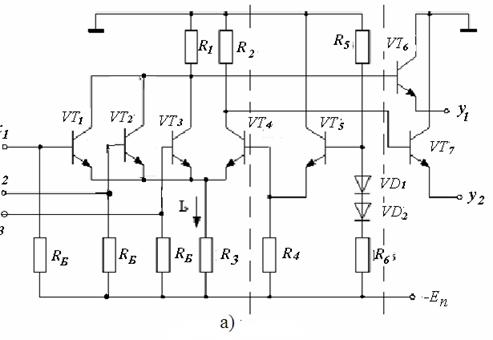

Функционально схема ЭСЛ состоит из трех узлов (см. рисунок 3.13):

а) токового переключателя на транзисторах VT1 ¸ VT4 и резисторах R1¸R3. Содержит две ветви: входную ‑ на транзисторах VТ1 ¸ VТ3 (максимально может быть до 9 входов) и резисторе R1 и опорную на VТ4 и резисторе R2. Транзисторы работают в ключевом режиме, а именно: открыт – активный режим, не входит в насыщенный, и заперт. Ветви имеют общее сопротивление R3. Источник питания En и резистор R3 образуют генератор тока, причем R3 >> R1, R2. Это дает постоянство эмиттерного тока  ;

;

б) источника опорного напряжения, включающего

б) источника опорного напряжения, включающего

|

б) источника опорного напряжения, включающего параметрический стабилизатор на элементах R5, VD1, VD2, R6 и эмиттерный повторитель на VT5 и R 4. VD1, VD2 – обеспечивают температурную компенсацию Uоп;

в) выходных эмиттерных повторителей на транзисторах VT6 и VT7. Цепь нагрузок транзисторов VT6 и VT7 вынесена из ИС ЭСЛ, что способствует снижению рассеиваемой в ней мощности и расширению функциональных возможностей. Эмиттерные повторители на VT6 и VT7 также являются сдвигателями уровней, повторяют Uвх, но сдвигают его на 0,7 В для обеспечения входа и выхода низкого  и высокого

и высокого  уровней.

уровней.

Таким образом, эмиттерные повторители на VT6 и VT7 обеспечивают:

1) формирование выходных сигналов;

2) развязку между переключателями тока и нагрузкой;

3) высокую нагрузочную способность;

4) быстрый перезаряд емкости нагрузки за счет малого выходного сопротивления.

В схеме общей шиной является шина + Еп, в результате чего потенциалы точек схемы отрицательны относительно общей шины. Однако в схеме ЭСЛ так же, как и в схемах ТТЛ, реализован принцип положительной логики, при которой большему выходному напряжению соответствует сигнал логической единицы, а меньшему – сигнал логического нуля.

Быстродействие токового переключателя высокое, так как транзисторы не входят в насыщение и, кроме того, мал логический перепад напряжений между значениями логического нуля и логической единицы. Это обеспечивается выбором малых значений сопротивлений резисторов R1 и R2 схемы, что крайне полезно с точки зрения уменьшения постоянной времени перезаряда выходной емкости транзистора.

Нетрудно заметить, что рассмотренная схема реализует по выходу y1 операцию ИЛИ-НЕ, а по выходу у2 – операцию ИЛИ

;

;  .

.

Резисторы RБ, включенные между базами транзисторов VТ1 ¸ VТ3 и – En, обеспечивают запертое состояние этих транзисторов при отсутствии входного сигнала. Это позволяет не беспокоиться о подключении неиспользуемых входов ИС к выводам источника питания. Условное обозначение ЭСЛ имеет вид (см. рисунок 3.13,б).

3.2.4 Логические элементы на полевых транзисторах

3.2.4.1 Логические элементы на МДП

Рассмотрим логические элементы НЕ, ИЛИ-НЕ, И-НЕ:

Рассмотрим логические элементы НЕ, ИЛИ-НЕ, И-НЕ:

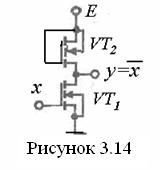

а) схема инвертора на МДП приведена на рисунке 3.14.

Транзистор VT1 работает в ключевом режиме, VT2 – всегда в активном. VT2 является нелинейной нагрузкой.

При запертом VT1 транзистор VT2 ‑ в активном режиме, ближе к насыщению, при насыщенном VT1 транзистор VT2 – в активном, ближе к отсечке.

При подаче на вход х низкого уровня напряжения VT1 запирается, VT2 близок к насыщению, на выходе ключа высокий уровень напряжения. При подаче на вход х высокого уровня напряжения VT1 отпирается, VT2 близок к отсечке, на выходе ключа низкий уровень напряжения. Выполняется операция  ;

;

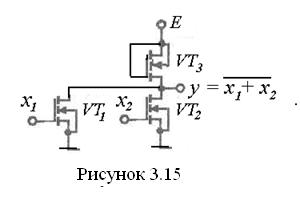

б) в двухвходовой схеме ИЛИ-НЕ (см. рисунок 3.15) входные транзисторы VT1 и VT2 соединены параллельно. Если хотя бы на один из входов подан высокий уровень напряжения, соответствующий транзистор отпирается, и на выходе схемы будет низкий уровень. И только при подаче на все входы схемы низкого уровня транзисторы VT1 и VT2 запрутся, и на выходе появится высокий уровень. Выполняется операция

б) в двухвходовой схеме ИЛИ-НЕ (см. рисунок 3.15) входные транзисторы VT1 и VT2 соединены параллельно. Если хотя бы на один из входов подан высокий уровень напряжения, соответствующий транзистор отпирается, и на выходе схемы будет низкий уровень. И только при подаче на все входы схемы низкого уровня транзисторы VT1 и VT2 запрутся, и на выходе появится высокий уровень. Выполняется операция  ;

;

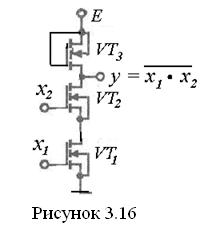

в) В двухвходовой схеме И-НЕ (см. рисунок 3.16) входные транзисторы VT1 и VT2 соединены последовательно. Если хотя бы на один из входов подан низкий уровень напряжения, соответствующий транзистор запирается, ток через входные транзисторы не течет, и на выходе схемы будет высокий уровень. И только при подаче на все входы схемы высокого уровня транзисторы VT1 и VT2 откроются, течет ток, и на выходе будет низкий уровень. Выполняется операция

в) В двухвходовой схеме И-НЕ (см. рисунок 3.16) входные транзисторы VT1 и VT2 соединены последовательно. Если хотя бы на один из входов подан низкий уровень напряжения, соответствующий транзистор запирается, ток через входные транзисторы не течет, и на выходе схемы будет высокий уровень. И только при подаче на все входы схемы высокого уровня транзисторы VT1 и VT2 откроются, течет ток, и на выходе будет низкий уровень. Выполняется операция  .

.

3.2.4.2 Логические элементы на КМДП

Основу микросхем КМДП составляет ключевой каскад на двух соединенных стоками МДП- транзисторах VT1 и VT2 (см. рисунок 3.17) с различными типами проводимости. Транзистор VT1 имеет канал с проводимостью n -типа; VT2 – канал с проводимостью р- типа. На соединенные вместе затворы подается входной сигнал x. Для КМДП принято, чтобы единица отображалась высоким уровнем, а ноль – низким.

Основу микросхем КМДП составляет ключевой каскад на двух соединенных стоками МДП- транзисторах VT1 и VT2 (см. рисунок 3.17) с различными типами проводимости. Транзистор VT1 имеет канал с проводимостью n -типа; VT2 – канал с проводимостью р- типа. На соединенные вместе затворы подается входной сигнал x. Для КМДП принято, чтобы единица отображалась высоким уровнем, а ноль – низким.

Напряжение питания Е положительной полярности может составлять от 3 до 15 В. Напряжение низкого уровня для микросхем КМДП равно 0,001 В, а напряжение высокого уровня практически равно напряжению питания.

При подаче на вход напряжения высокого уровня транзистор VT1 открывается, а транзистор VT2  закрывается. На выходе устанавливается напряжение низкого уровня. При подаче на вход напряжения низкого уровня транзистор VT1 закрыт, а транзистор VT2 открыт. Напряжение источника питания через открытый транзистор VT2 подается на выход каскада — это напряжение высокого уровня. Таким образом, данный ключевой каскад реализует логическую функцию НЕ.

закрывается. На выходе устанавливается напряжение низкого уровня. При подаче на вход напряжения низкого уровня транзистор VT1 закрыт, а транзистор VT2 открыт. Напряжение источника питания через открытый транзистор VT2 подается на выход каскада — это напряжение высокого уровня. Таким образом, данный ключевой каскад реализует логическую функцию НЕ.

Следует отметить одну важную особенность КМДП -ключа и интегральных микросхем на его основе — в статическом режиме потребляемая от источника питания мощность меньше на несколько порядков по сравнению с мощностью самых маломощных логических элементов ТТЛ и ТТЛШ. Это объясняется тем, что в статическом режиме один из транзисторов закрыт, и, следовательно, ток через ключ не проходит.

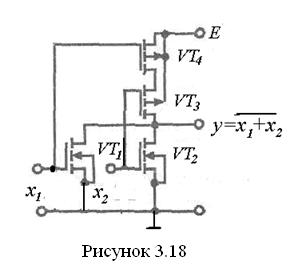

Схема логического элемента ИЛИ-НЕ на основе КМДП -ключа приведена на рисунке 3.18. Если на оба входа поданы сигналы низкого уровня, то транзисторы VT 3 и VT 4 будут открыты, так как имеют канал с проводимостью р-типа, а транзисторы VT 1 и VT 2 — закрыты, так как имеют канал с проводимостью n -типа. Таким образом, на выходе установится напряжение высокого уровня (логическая единица). При подаче напряжения высокого уровня хотя бы на один из входов соответствующий транзистор VT 3 или VT 4 закроется, т.е. ток через них не течет, а транзистор VT 1 или VT 2 соответственно откроется. На выходе установится напряжение низкого уровня (логический ноль). Видно, что данная схема реализует логическую функцию ИЛИ—НЕ.

Схема логического элемента ИЛИ-НЕ на основе КМДП -ключа приведена на рисунке 3.18. Если на оба входа поданы сигналы низкого уровня, то транзисторы VT 3 и VT 4 будут открыты, так как имеют канал с проводимостью р-типа, а транзисторы VT 1 и VT 2 — закрыты, так как имеют канал с проводимостью n -типа. Таким образом, на выходе установится напряжение высокого уровня (логическая единица). При подаче напряжения высокого уровня хотя бы на один из входов соответствующий транзистор VT 3 или VT 4 закроется, т.е. ток через них не течет, а транзистор VT 1 или VT 2 соответственно откроется. На выходе установится напряжение низкого уровня (логический ноль). Видно, что данная схема реализует логическую функцию ИЛИ—НЕ.

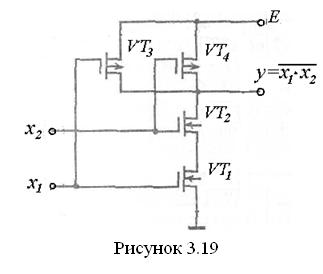

Устройство базового элемента И—НЕ как бы обратно устройству элемента ИЛИ—НЕ: параллельно соединены транзисторы с каналами р -типа, а последовательно — с каналами п- типа (см. рисунок 3.19). Работа данной схемы абсолютно идентична работе элемента ИЛИ—НЕ с тем исключением, что напряжение низкого уровня на выходе устанавливается только при одновременной подаче на оба входа элемента напряжения высокого уровня, а во всех остальных случаях на выходе будет присутствовать напряжение высокого уровня. Действительно, при одновременной подаче на входы x 1 и x 2 напряжения высокого уровня транзисторы VT 1 и VT 2 открываются, а транзисторы VT 3 и VT 4 закрываются. На выходе устанавливается напряжение низкого уровня (логический ноль). При подаче хотя бы на один из входов напряжения низкого уровня один из параллельно включенных транзисторов VT 3 или VT 4 открывается, а соответствующий ему комплементарный транзистор (VT 1 или VT 2 ) закрывается. На выход в этом случае через соответствующий открытый транзистор передается напряжение источника питания. На выходе устанавливается напряжение высокого уровня (логическая единица).

Устройство базового элемента И—НЕ как бы обратно устройству элемента ИЛИ—НЕ: параллельно соединены транзисторы с каналами р -типа, а последовательно — с каналами п- типа (см. рисунок 3.19). Работа данной схемы абсолютно идентична работе элемента ИЛИ—НЕ с тем исключением, что напряжение низкого уровня на выходе устанавливается только при одновременной подаче на оба входа элемента напряжения высокого уровня, а во всех остальных случаях на выходе будет присутствовать напряжение высокого уровня. Действительно, при одновременной подаче на входы x 1 и x 2 напряжения высокого уровня транзисторы VT 1 и VT 2 открываются, а транзисторы VT 3 и VT 4 закрываются. На выходе устанавливается напряжение низкого уровня (логический ноль). При подаче хотя бы на один из входов напряжения низкого уровня один из параллельно включенных транзисторов VT 3 или VT 4 открывается, а соответствующий ему комплементарный транзистор (VT 1 или VT 2 ) закрывается. На выход в этом случае через соответствующий открытый транзистор передается напряжение источника питания. На выходе устанавливается напряжение высокого уровня (логическая единица).

2015-03-08

2015-03-08 1391

1391