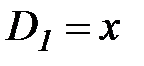

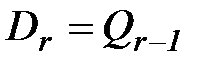

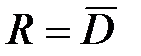

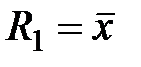

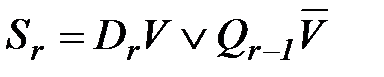

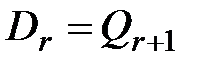

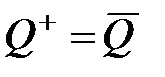

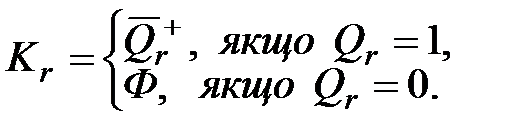

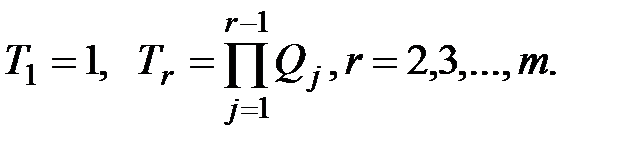

На рис. 2.23 зображено цифровий автомат, що складається з m послідовно з'єднаних D -тригерів, функції збудження яких мають вид

,

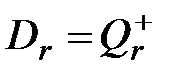

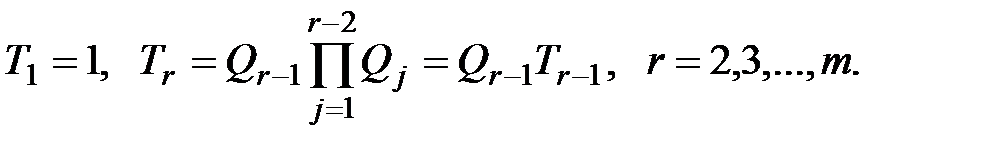

,  , r = 2, 3, …, m. (2.1)

, r = 2, 3, …, m. (2.1)

Рисунок 2.23 — Регістр зсуву

Зі співвідношення (2.1) випливає, що інформація, яка зберігається у деякому такті в тригері Qr-1, передається в наступному такті в тригер Qr, тобто відбувається зсув інформації від тригера до тригера. Такі автомати називаються регістрами зсуву. Їх використовують для зсуву m -розрядних чисел в одному напрямку (значення вхідного сигналу x, що відповідає деякому такту, з'являється на виході регістра зсуву Qm через m тактів).

Якщо Qm — старший розряд, то відбувається зсув убік або ліворуч старших розрядів. Якщо Qm вважати молодшим розрядом, то відбувається зсув убік або праворуч молодших розрядів. Крім основного призначення (зсув чисел) регістри зсуву, використовують і для зсуву нечислової інформації (наприклад, у разі побудови з них лічильників).

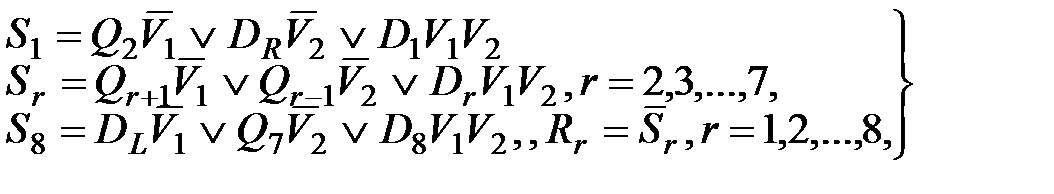

На рис. 2.24 зображено 8-розрядний регістр зсуву, виконаний на мікросхемі К564ИР2, що є здвоєним 4-розрядний регістром зсуву. Асинхронні входи R ' призначені для установлення регістра зсуву у стані «0». Даний регістр зсуву можна використовувати для перетворення послідовного коду на паралельний (зчитування в цьому випадку проводиться з восьми виходів регістра за допомогою схем І після введення в нього 8-розрядного коду).

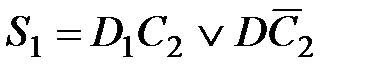

Регістр зсуву можна виконати і з RS -тригерів. Дійсно, підставивши у функцію переходів (2.1) значення S=D і

, одержимо функцію переходів Q+=D, тобто функції збудження Sr і Rr регістра зсуву, виконаного на

, одержимо функцію переходів Q+=D, тобто функції збудження Sr і Rr регістра зсуву, виконаного на

RS -тригерах, на підставі функції (2.1) можна подати у такому вигляді:

S1=x, Sr=Qr-1,  ,

,  , r = 2, 3,..., m,

, r = 2, 3,..., m,

або S1= x, Sr= Qr-1, r = 2, 3,..., m,  , r = 1, 2,..., m.

, r = 1, 2,..., m.

Рисунок 2.24 — Восьмирозрядний регістр зсуву,

виконаний на мікросхемі К564ИР2

Часто потрібні більш складні регістри зсуву: з паралельним синхронним записом інформації, реверсивні, реверсивні з паралельним синхронним записом інформації. Такі регістри називаються універсальними.

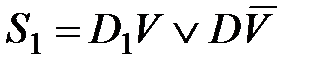

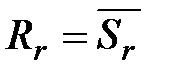

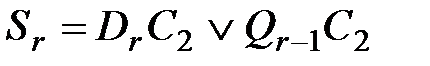

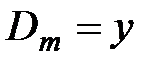

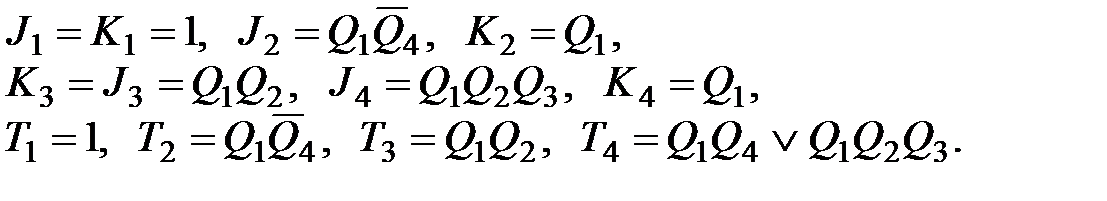

Мікросхема К155ИР1 – це 4-хрозрядний регістр зсуву із синхронним записом інформації (рис. 2.25), виконаний на основі чотирьох RS -тригерів. Функції збудження Sr і Rr цих тригерів мають вигляд:

,

,

, r = 2, 3, 4, (2.2)

, r = 2, 3, 4, (2.2)

a  , де r = 1, 2, 3, 4.

, де r = 1, 2, 3, 4.

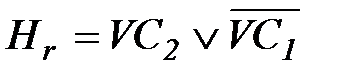

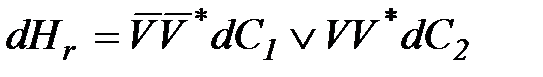

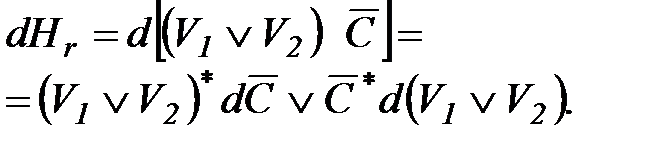

Вхід D є входом послідовного введення інформації. Через Hr позначатимемо сигнал, який надходить на тактовий вхід r -го тригера навіть у тому випадку, якщо Hr не залежить від r. Залежно від внутрішньої структури тригерів впливати на них можуть сигнали dHr або  . У цьому випадку

. У цьому випадку  та

та

(2.3)

(2.3)

Рисунок 2.25— Регістр зсуву, з синхронним паралельним

записом К155ИР1

З цього співвідношення випливає, що на тригери можуть впливати сигнали dC1, dC2,  і dV.

і dV.

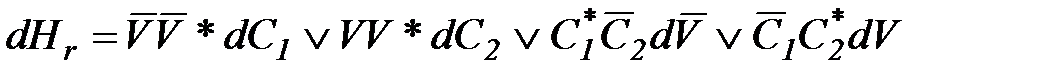

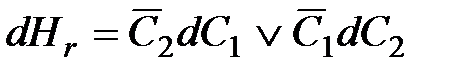

Через те що сигнал V входить у функції збудження (2.2), то його зміни не повинні впливати на тригери. З виразу (2.3) випливає, що для цього сигнал V має змінюватися тільки при значеннях C1= С2 = 0 або C1= C2 = 1. У цьому випадку

(2.4)

(2.4)

(тут, наприклад, множник VV* означає, що сигнал V не повинний змінюватися з 0 на 1 при dC2 = 1).

З виразів (2.2) і (2.3) випливає, що при V = 0, функції збудження S1=D, Sr=Qr-1 та сигнал dHr = dC1, тобто схема працює як регістр зсуву за від’ємним перепадом (з 1 на 0) сигналу C1, а при V = 1, функції збудження Sr = Dr і сигнал dHr=dC2, тобто схема працює в режимі синхронного запису в регістр значень сигналів Dr за від’ємним перепадом сигналу C2. Якщо у формулі (2.4) взяти C1 =C2= C, то отримаємо, що сигнал dHr = dC, тобто залежно від значення сигналу V буде вироблятися запис або зсув за від’ємним перепадом того самого сигналу С.

З виразів (2.2) і (2.3) випливає, що при V = С2 функції збудження  ,

,  і сигнал

і сигнал  , тобто при C1 = 0 відбувається запис інформації у регістр за від’ємним перепадом сигналу С2, а при C2 = 0 — зсув її за від’ємним перепадом сигналу C1. На підставі формул (2.2) і (2.3) легко переконатися, що при V = C1 можливий тільки запис інформації за від’ємним перепадом сигналу C1 при значенні сигналу C2 = 1.

, тобто при C1 = 0 відбувається запис інформації у регістр за від’ємним перепадом сигналу С2, а при C2 = 0 — зсув її за від’ємним перепадом сигналу C1. На підставі формул (2.2) і (2.3) легко переконатися, що при V = C1 можливий тільки запис інформації за від’ємним перепадом сигналу C1 при значенні сигналу C2 = 1.

Якщо в регістрі зсуву (див. рис. 2.23) змінити напрямок зсуву інформації, то функції збудження D -тригерів визначатимуться співвідношеннями

, r = 1, 2, …, m-1,

, r = 1, 2, …, m-1,  . (2.5)

. (2.5)

Якщо функції збудження (2.1) і (2.5) об'єднати в такий спосіб:

(2.6)

(2.6)

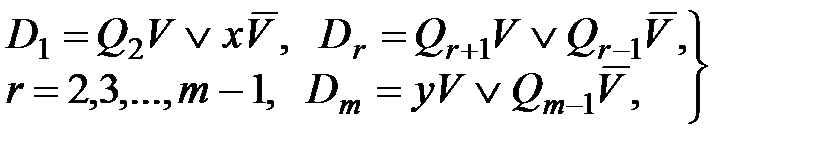

то одержимо реверсивний регістр зсуву (при V = 0 — зсув ліворуч, а при V = 1 — праворуч). На мікросхемах К155ИР1 можна виконати реверсивний регістр зсуву, якщо для зсуву праворуч використовувати входи Dr, призначені для паралельного синхронного запису інформації. Ця можливість випливає з порівняння співвідношень (2.2) і (2.6). На рис. 2.26 зображено 8-розрядний реверсивний регістр зсуву, виконаний на двох мікросхемах К155ИР1. Можливості рівнозбіжного запису в даному регістрі відсутня. Для зсуву ліворуч можна було б використовувати тактовий вхід C1, а для зсуву праворуч — тактовий вхід C2. З виходів z1 і z2 знімається послідовний код при зсуві праворуч і ліворуч.

Мікросхема К155ИР13 є 8-розрядним реверсивним регістром зсуву, з паралельним синхронним записом інформації (рис. 2.27), виконаний на основі RS -тригерів.

Рисунок 2.26 — Восьмирозрядний реверсивний регістр зсуву,

виконаний на двох мікросхемах К155ИР1

Рисунок 2.27 — Восьмикорозрядний реверсивний регістр

зсуву з синхронним паралельним записом К155ИР13

Функції збудження Sr і Rr цих тригерів описуються виразами:

(2.7)

(2.7)

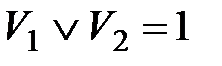

де DR і DL — вхідні сигнали у разі послідовного введення інформації при зсувах ліворуч і праворуч. Імпульсний тактовий сигнал dHr, що впливає на тригери, визначається співвідношенням

(2.8)

(2.8)

З цього співвідношення випливає, що сигнали V1 і V2, не повинні змінюватися при значенні сигналу C = 0, тому що вони входять у функції збудження (2.7), а зсув і запис інформації відбуваються за додатним перепадом (з 0 на 1) сигналу C при  . З виразів (24.7) випливає, що при V1 = 0 і V2 =1 відбувається зсув інформації праворуч, при V1 = 1 і V2= 0 — ліворуч, а при V1=V2 =1 — запис інформації в регістр. Регістр має асинхронний потенційний вхід R' для встановлення нульового стану регістра.

. З виразів (24.7) випливає, що при V1 = 0 і V2 =1 відбувається зсув інформації праворуч, при V1 = 1 і V2= 0 — ліворуч, а при V1=V2 =1 — запис інформації в регістр. Регістр має асинхронний потенційний вхід R' для встановлення нульового стану регістра.

2.4.2 Лічильники за mod M

Будь-який лічильник можна виконати у вигляді синхронного, асинхронного потенційного або асинхронного імпульсного автомата. Асинхронні потенційні лічильники через їхню складність використовувати недоцільно. Асинхронні імпульсні лічильники можна виконати із синхронних лічильників за допомогою деяких перетворень. Розглянемо в основному синхронні лічильники та лічильники змішаного типу (синхронні лічильники з асинхронним потенційним установленням деякого внутрішнього стану).

Синхронним лічильником за mod M називають цифровий синхронний автомат без входів, що має М різних внутрішніх станів, які циклічно змінюються під впливом змін тактового сигналу H з 1 на 0 (чи з 0 на 1). На відміну від реверсивних лічильників і лічильників зі змінним коефіцієнтом перерахування лічильники за mod M не мають вхідних сигналів х, якікерують переходами між внутрішніми станами.

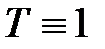

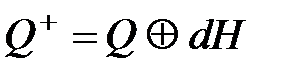

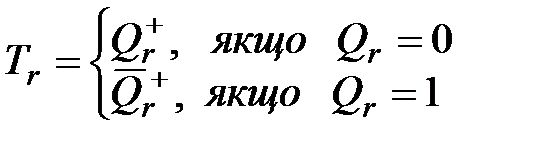

Один із M внутрішніх станів лічильника вибирають як початковий. Оскільки внутрішні стани лічильника змінюються циклічно, то після М змін тактового сигналу з 1 на 0 (або з 0 на 1) лічильник повертається в початковий стан, що свідчить про його переповнення. Якщо лічильник перебував в початковому стані і тактовий сигнал H змінився N раз, то при N > M за кінцевим станом лічильника можна визначити лише залишок від розподілу числа N на М, тобто рахунок здійснюють за модулем М. Число М називають коефіцієнтом перерахування лічильника. Найпростішим є лічильник за mod 2, що становить собою T -тригер при  . Дійсно, при Т = 1 наступний стан тригера

. Дійсно, при Т = 1 наступний стан тригера  ,а при dH = 1 стан

,а при dH = 1 стан  , тобто стан тригера 0 і 1 циклічно змінюється при кожній зміні тактового сигналу Н з 1 на 0. Граф переходів лічильника за mod 2 зображено на рис. 2.28, а.

, тобто стан тригера 0 і 1 циклічно змінюється при кожній зміні тактового сигналу Н з 1 на 0. Граф переходів лічильника за mod 2 зображено на рис. 2.28, а.

На рис. 2.6, б наведено граф переходів лічильника за mod 7, внутрішні стани якого позначені цифрами від 1 до 2. Для одержання семи різних внутрішніх станів потрібно використовувати не менше ніж три тригери.

Спосіб кодування внутрішніх станів лічильника може бути довільним (важливо тільки, щоб усі внутрішні стани були різні). У загальному випадку від обраного способу кодування внутрішніх станів автомата залежить його складність. Закодуємо внутрішні стани лічильника значеннями вихідних сигналів трьох тригерів Q1, Q2 і Q3 так, як показано на рис. 2.28.

а) mod 2; б) mod 7

Рисунок 2.28 — Графи переходів лічильників за mod 2 та mod 7

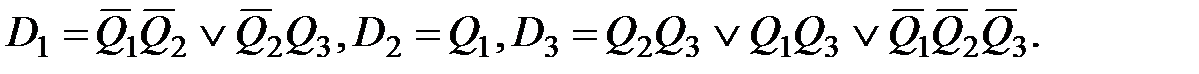

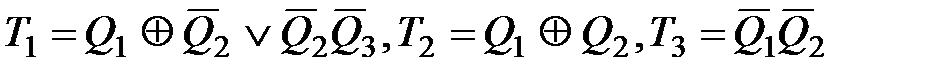

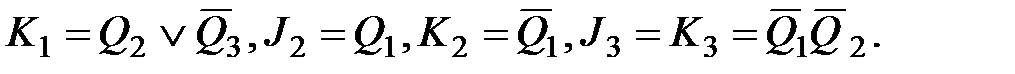

На підставі рис. 2.28 можна укласти таблицю істинності (табл. 2.16) і діаграми Вейча для функцій Q3+, Q2+, Q1+ (рис. 2.29). Для синтезу лічильників, як і будь-яких цифрових автоматів, можна використовувати тригери типів: D, T та JK. Складність автомата в загальному випадку залежить від використаних типів тригерів. Слід мати на увазі, що в одному автоматі можна використовувати тригери різних типів. Зробимо синтез лічильника за mod 7 із тригерів типів D, Т та JK. Для цього потрібно знайти їх функції збудження Dr, Тr, Jr і Кr (r = 1, 2, 3).

Рисунок 2.29 — Граф переходів лічильника за mod 7

Таблиця 2.16 — Таблиця істинності лічильника за mod 7

| i | Q3 | Q2 | Q1 | Q3+ | Q2+ | Q1+ |

З функції переходів D -тригера (2.7) випливає, що функції збудження

, (2.9.)

, (2.9.)

тому функції збудження тригерів лічильника за mod 7 знаходять за діаграмами Вейча, зображених на рис. 2.30:

Рисунок 2.30 — Діаграма Вейча для функції переходів лічильника за mod 7

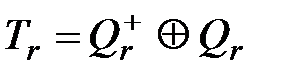

З функції переходів T -тригера і властивостей операції «сума за модулем два» випливає, що функції збудження  , тобто

, тобто

(2.10).

(2.10).

За цим співвідношенням заповнюються діаграми Вейча для функцій збудження T1, T2 і T3 (рис. 2.31) — у половину діаграми Вейча, позначену Qr, заносяться значення  , а в іншу половину — значення Qr+ з діаграм Вейча для функцій Qr+ (див. рис. 2.30).

, а в іншу половину — значення Qr+ з діаграм Вейча для функцій Qr+ (див. рис. 2.30).

Рисунок 2.31 — Синтез лічильника за mod 7 на тригерах типу Т

З рис. 2.31 випливає, що функції збудження T- тригерів лічильника за mod7

.

.

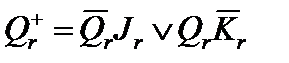

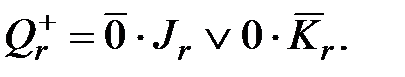

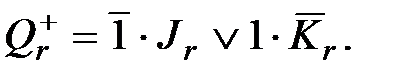

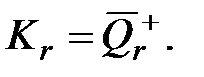

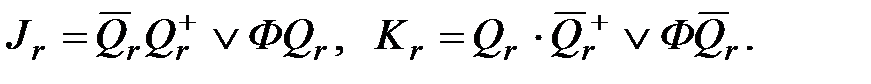

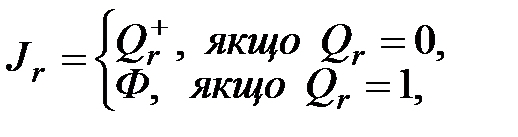

З функції переходів JK -тригера випливає, що  __ логічне рівняння з двома невідомими Jr і Kr , які потрібно розв’язати щодо цих невідомих. Через те що для функцій збудження Jr і Кr необхідно складати тільки діаграми Вейча, то для функцій Qr+, можна скористатися наступним методом. Нехай Qr = 0, тоді

__ логічне рівняння з двома невідомими Jr і Kr , які потрібно розв’язати щодо цих невідомих. Через те що для функцій збудження Jr і Кr необхідно складати тільки діаграми Вейча, то для функцій Qr+, можна скористатися наступним методом. Нехай Qr = 0, тоді  З останнього рівняння випливає, що Jr = Qr+, a Kr = Ф — довільні значення. Нехай тепер Qr = 1, тоді

З останнього рівняння випливає, що Jr = Qr+, a Kr = Ф — довільні значення. Нехай тепер Qr = 1, тоді  З цього рівняння випливає, що Jr = Ф, а

З цього рівняння випливає, що Jr = Ф, а

Об'єднавши обидва розв`язки при Qr = 0 і Qr = 1, отримаємо

Дійсно, з даних виражень випливає, що

(2.11)

(2.11)

Діаграми Вейча для функцій збудження Jr і Kr (рис. 2.10) заповнюють за аналогією із заповненням діаграм Вейча для функцій збудження Тr.

З рис. 2.32 випливає, що функції збудження JK -тригерів лічильника за mod 7:

Побудуємо принципову схему лічильника за функціями збудження D1, D2 і T3. Для цього перетворимо функцію збудження D1 до вигляду:  Якщо замість прямого входу D використати інверсний вхід, то виходи тригера Q і

Якщо замість прямого входу D використати інверсний вхід, то виходи тригера Q і  поміняються місцями.

поміняються місцями.

Рисунок 2.32 — Синтез лічильника за mod 7 на тригерах типу JK

На рис. 2.33 зображено принципову схему лічильника за mod 7, виконану на мікросхемах серії K155 відповідно до отриманих функцій збудження  , D2 і Т (якщо на вхід елемента серії K155 не надходить ніякого сигналу, то це еквівалентно надходженню на цей вхід сигналу 1). Слід мати на увазі, що при зміні функції збудження D на

, D2 і Т (якщо на вхід елемента серії K155 не надходить ніякого сигналу, то це еквівалентно надходженню на цей вхід сигналу 1). Слід мати на увазі, що при зміні функції збудження D на  асинхронні потенційні входи R' і S' також поміняються місцями.

асинхронні потенційні входи R' і S' також поміняються місцями.

Рисунок 2.33 — Схема лічильника за mod 7 на тригерах типів D та Т

Побудуємо принципову схему лічильника за mod 7, використовуючи функції збудження J1, K1, D2, J3 і К3 на мікросхемах серії К155 (рис. 2.34). Так як JK -тригери спрацьовують при значенні сигналу dH = 1, а D -тригер — при значенні сигналу  то моменти спрацьовування тригерів необхідно погоджувати за допомогою логічного елементу НЕ.

то моменти спрацьовування тригерів необхідно погоджувати за допомогою логічного елементу НЕ.

Рисунок 2.34 — Схема лічильника за mod 7 на тригерах типів D та JK

Під час проектування цифрових пристроїв особливе значення мають двійкові та двійково-десяткові лічильники, кодування внутрішніх станів яких виконано за допомогою двійкових і двійково- десяткових чисел. Двійковий лічильник, побудований з т тригерів, має 2 m внутрішніх станів, тобто є лічильником по mod 2 m. Кодування внутрішніх станів двійково- десяткових лічильників виконується кодом 8—4—2—1, тобто ці лічильники синтезуються з чотирьох тригерів і є лічильниками за mod 10.

На рис. 2.35 наведено граф переходів двійкового лічильника за mod 23. Зробимо синтез цього лічильника на Т- тригерах. Уклавши за графом переходів таблицю істинності (табл. 2.17), а потім діаграми Вейча для функцій Qr+ і Тr (рис.2.36), можна одержати

T1 = 1, T2 = Q1, T3 = Q1Q2. (2.12)

Рисунок 2.35 — Граф переходів двійкового лічильника за mod 8

Якщо зробити синтез лічильника за mod 2 4,то функції збудження T- тригерів матимуть вигляд:

T1 = 1, T2 = Q1, T3 = Q1Q2, T4 = Q 1 Q2 Q3 . (2.13)

Порівнявши вирази (2.12) і (2.13), можна зазначити, що функції збудження перших трьох тригерів не змінилися.

Таблиця 2.17 — Таблицю істинності двійкового лічильника за mod 8

| i | Q3 | Q2 | Q1 | Q3+ | Q2+ | Q1+ |

Рисунок 2.36 — Синтез двійкового лічильника за mod 8 на тригерах типу Т

З цього можна дійти висновку, що функції збудження лічильника за mod 2m повинні описуються виразами

(2.14)

(2.14)

Відповідно до цих функцій збудження, виконаний 6-розрядний двійковий лічильник на мікросхемі К155ИЕ8.

Вираження (2.14) можна надати вигляду

(2.15)

(2.15)

Схема двійкового лічильника, що відповідає цим функціям збудження, значно простіша, ніж схема лічильника, що відповідає функціям збудження (2.14), однак швидкодія менше через послідовне вмикання логічного елемента І (максимально допустиме значення частоти тактового сигналу Н буде менше).

На рис. 2.37 показано частину двійкового лічильника, виконану до функцій збудження (2.15).

Рисунок 2.37 — Схема двійкового лічильника за mod 2m

На рис. 2.38 наведено граф переходів двійково– десяткового лічильника за mod 10. Якщо за цим графом переходів зробити синтез синхронного лічильника на тригерах типів JК та Т, то можна одержати

(2.16)

(2.16)

Рисунок 2.38 — Граф переходів двійково- десяткового лічильника

За отриманими функціями збудження можна побудувати принципові схеми двійково- десяткових лічильників. На рис. 2.39 зображено схему такого лічильника, виконана на JK -тригерах (мікросхеми K155ТВ1; входи що не використовуються, не зображені).

Рисунок 2.39 — Схема двійково- десяткового лічильника

Звичайно лічильники за mod M виконують так, що в них є тригер (або ЛЕ), вихідний сигнал якого змінюється з 1 на 0 (або з 0 на 1) тільки в момент повернення лічильника в початковий (нульовий) стан. Цей сигнал свідчить про переповнення лічильника при надходженні на його вхід М імпульсів (dH =1) і може бути використаний як вхідний сигнал іншого лічильника. Лічильники за mod Mj (j = 1, 2,..., k) можна з'єднувати послідовно (рис. 2.40) для одержання лічильників за mod (M1 M2 … Mk). Якщо послідовно з'єднати т лічильників за mod 2, то вийде двійковий лічильник за mod 2m. У такий спосіб виконаний лічильник за mod 23 на мікросхемі K155ИЕ5 (у цій мікросхемі є ще лічильник за mod 2, що дає змогу одержати лічильник за mod 24). Ця мікросхема — 4-розрядний двійковий лічильник, виконаний на двоступінчастих JК - тригерах (рис. 2.41). Лічильник має два рахункових входи С1, С2 і два входи установлення нуля R01, R02. Вхід Q1 внутрішньо не з'єднаний з іншими тригерами схеми. Це дає можливість використовувати схему в двох незалежних режимах роботи:

– як 4-розрядний двійковий лічильник, коли вхідні лічильні імпульси надходять на вхід С1. Виводи здійснюють операцію розподілу на 2, 4, 8 і 16;

– як 3-розрядний двійковий лічильник, коли вхідні лічильні імпульси надходять на вхід С2. Перший тригер, не з'єднаний з іншими тригерами схеми, можна використовувати як елемент для функції розподілу на два. Встановлювальні входи мікросхеми забезпечують припинення лічення і повертають усі чотири тригери в стан низького рівня, якщо на входи R01 та R02 одночасно надходить високий рівень напруги. При операції лічення на одному з входів установки R01 або R02 має бути потенціал низького рівня.

Рисунок 2.40 — Структурна схема асинхронного лічильника

Рисунок 2.41 — Умовне позначення лічильника К155ИЕ5

Хоча кожний з лічильників за mod Mj є синхронним, однак лічильник за mod (M1 M2 … Mk) буде вже асинхронним, тому що відсутній єдиний тактовий сигнал для всього лічильника (у кожному лічильнику за mod Mj використовується свій тактовий сигнал Hj ). Недоліком таких лічильників є їх послідовне спрацьовування, що спричиняє запізнювання спрацьовування останнього лічильника щодо тактового сигналу першого.

Мікросхема K155ИЕ2 (рис. 2.42) містить лічильник за mod 2 і лічильник за mod 5, послідовне з'єднання яких (пунктир на рис. 2.42) дає двійково- десятковий лічильник (код 8-4-2-1). Лічильник за mod 5 виконаний у виді асинхронного імпульсного лічильника. Лічильник має асинхронні потенційні входи R' і S’ 9 для встановлення стану «0» (0000) і «9» (1001).

Рисунок 2.42 — Двійково - десятковий лічильник,

виконаний на мікросхемі К155ИЕ2

На рис. 2.43 зображено часові діаграми вихідних сигналів лічильника за mod 10.

Рисунок 2.43 — Часові діаграми двійково - десяткового лічильника

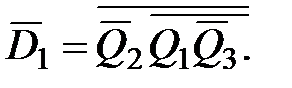

Використовуючи асинхронні входи R' і S'9, на основі мікросхеми K155ИЕ2 можна зробити лічильники за mod М, де М < 10. На рис. 2.44 показано лічильник за mod 7, робота якого пояснюється графом переходів (рис. 2.45) та часовими діаграмами (рис. 2.24). Як тільки лічильник установиться в стан «6» (0110), на виходах Q2 і Q3 з'являться значення сигналів 1, що по входах S'9 переведуть лічильник у стан «9» (1001) — пунктир на рис. 2.46. Тривалість перебування лічильника в стані «6» визначається швидкодією тригерів Q2 і Q3, що на входах S'9 установлюються в стан 0.

Рисунок 2.44 — Лічильник за mod 7 з асинхронними потенційними

зворотними зв'язками

Рисунок 2.45 — Граф переходів лічильника за mod 7 з асинхронними

потенційними зворотними зв'язками

Рисунок 2.46 — Часові діаграми лічильника за mod7

з асинхронними потенційними зворотними зв’язками

Недоліком цього способу побудови лічильників є критичність їхньої роботи — у разі великого розкиду часу спрацьовування тригерів деякі з них можуть не встановитися в необхідний стан. Якщо зворотні зв'язки (див. рис. 2.22) завести на входи R', а не на S¢9, то вийде лічильник за mod 6. Аналогічно можливо одержати й інші коефіцієнти перерахування.

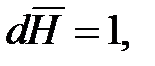

Мікросхема К564ИЕ10 є здвоєним лічильником за mod 16, у якому тригери спрацьовують по сигналу  (якщо С2 =1, то лічильник запускається додатними перепадами сигналу С1, а якщо C1 =0, то від’ємними перепадами сигналу C2 ).

(якщо С2 =1, то лічильник запускається додатними перепадами сигналу С1, а якщо C1 =0, то від’ємними перепадами сигналу C2 ).

На рис. 2.47 зображено лічильник за mod 102, виконаний на основі цієї мікросхеми з використанням асинхронного встановлення лічильника в нульовий стан на вході R'.

Рисунок 2.47 — Лічильник за mod 102

Надійність роботи даного лічильника досить висока, тому що ЛЕ І - НЕ та НЕ вносять запізнювання в коло асинхронного зворотного зв'язку.

Лічильник К176ИЕ2 (рис. 2.48) може працювати і як двійковий, і як десятковий. Він має п'ять двійкових входів і один десятковий. По входах D1-D4 у нього можна записати попередні дані. На вхід R лічильника надходить сигнал асинхронного скидання, а на С - тактова частота. Якщо на вході  є високий рівень, то лічильник працює як двійковий, якщо низький – як десятковий і на виводі f/10 виникають імпульси з частотою f/10. Високий рівень на вході EC дозволяє лічення.

є високий рівень, то лічильник працює як двійковий, якщо низький – як десятковий і на виводі f/10 виникають імпульси з частотою f/10. Високий рівень на вході EC дозволяє лічення.

Мікросхеми К176ИЕЗ і К176ИЕ4 (рис. 2.48) - це лічильники відповідно за mod 6 (або за mod 2) та mod 10 з дешифратором для семисегментного індикатора. На вхід C надходить тактова частота, на R - асинхронний сигнал скидання з активним високим рівнем. На вхід G надходить імпульсна послідовність з частотою 32 або 64 кГц, необхідна для роботи електролюмінісцентних або рідинно-кристалічних індикаторів.

Мікросхема K155ИЕ4 є лічильник – дільником на 12 (для побудови дільника на 12 потрібно замкнути виводи 2 і 6). Якщо хоча б на одному з входів R0 або &R0 є високий рівень, відбувається лічення.

Рисунок 2.48 — Умовні позначення лічильників

Мікросхема K176ИЕ5 - це лічильник – генератор секундних імпульсів. Безпосередньо до виводів T і  підключається кварцовий резонатор на 32 768 Гц або 16 384 Гц, або надходить частота із зовнішнього генератора імпульсів. При цьому на буферних виходах A і

підключається кварцовий резонатор на 32 768 Гц або 16 384 Гц, або надходить частота із зовнішнього генератора імпульсів. При цьому на буферних виходах A і  є присутнім сформована і посилена послідовність, а на виходах 1, 4 та 5 тактова частота розділена відповідно на 28, 214, 215. Для того щоб сигнал надійшов на вихідний дільник необхідно подати його з виводу 1 на вивід 2 мікросхеми. На вхід R подають асинхронний сигнал скидання з активним високим рівнем.

є присутнім сформована і посилена послідовність, а на виходах 1, 4 та 5 тактова частота розділена відповідно на 28, 214, 215. Для того щоб сигнал надійшов на вихідний дільник необхідно подати його з виводу 1 на вивід 2 мікросхеми. На вхід R подають асинхронний сигнал скидання з активним високим рівнем.

Мікросхема К564ИЕ9 містить лічильник за mod 8 і повний дешифратор із прямими виходами.

2015-07-14

2015-07-14 1707

1707