Асинхронные двоичные счетчики представляют собой цепочку Т-триггеров, последовательно соединенных друг с другом. Импульсами счета для триггеров более старших разрядов являются сигналы с выходов Q или  триггеров младших разрядов. Это представление справедливо как для суммирующих, так и для вычитающих счетчиков. Различия при этом состоят в направлении переключения предыдущего разряда, вызывающего переключение следующего. При суммировании следующий разряд переключается при переходе предыдущего от 1 к 0 под действием сигнала переноса, а при вычитании — при переходе предыдущего от 0 к 1 под действием сигнала заема. Следовательно, различие между вариантами заключается в разном подключении входов триггеров к выходам предыдущих.

триггеров младших разрядов. Это представление справедливо как для суммирующих, так и для вычитающих счетчиков. Различия при этом состоят в направлении переключения предыдущего разряда, вызывающего переключение следующего. При суммировании следующий разряд переключается при переходе предыдущего от 1 к 0 под действием сигнала переноса, а при вычитании — при переходе предыдущего от 0 к 1 под действием сигнала заема. Следовательно, различие между вариантами заключается в разном подключении входов триггеров к выходам предыдущих.

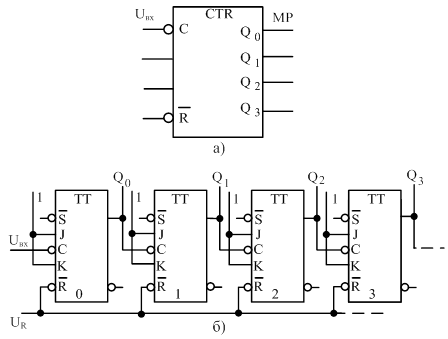

УГО и логическая схема четырехразрядного асинхронного двоичного суммирующего счетчика с последовательным переносом на универсальных JK-триггерах представлены на рисунке 27. УГО счетчика представляет собой прямоугольник с аббревиатурой CTR (от англ. counter) во внутреннем поле.

Рисунок 27 — Четырехразрядный асинхронный двоичный суммирующий счетчик с последовательным переносом на JK-триггерах. Условное графическое обозначение (а) и логическая схема (б)

На рисунке 27 на объединенные входы J и K триггеров постоянно подаются единичные сигналы с целью организации асинхронных Т-триггеров на базе JK-триггеров. Входные импульсы подаются в одну точку схемы на счетный вход триггера младшего разряда T0 (рисунок 27, б). Состояние счетчика считывается с прямых выходов триггеров Q3…Q0, причем с выхода Q0 считывается младший разряд (МР).

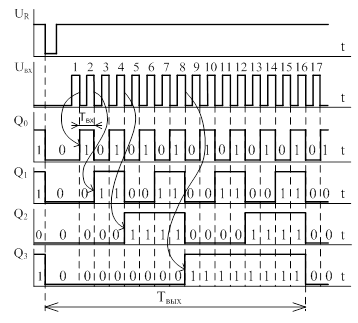

Работа счетчика поясняется временными диаграммами (рисунок 28).

Рисунок 28 — Временные диаграммы, поясняющие работу четырехразрядного двоичного суммирующего счетчика

Для сброса счетчика в исходное нулевое состояние на вход сброса  кратковременно подается нулевой сигнал. Из временных диаграмм следует:

кратковременно подается нулевой сигнал. Из временных диаграмм следует:

– триггер младшего разряда T0 переключается в противоположное состояние каждым входным импульсом в момент его окончания, а триггер любого старшего разряда переключается в противоположное состояние при переключении триггера соседнего младшего разряда от 1 к 0 под действием сигнала переноса;

– частота импульсов на выходе каждого триггера в два раза меньше чем на входе, а на выходе счетчика (выход Q3) — в шестнадцать раз меньше чем на входе, так как коэффициент пересчета счетчика Кпер = 24 = 16;

– после поступления шестнадцатого входного импульса счетчик сбрасывается в исходное нулевое состояние, а семнадцатый импульс начинает новый цикл работы, повторяющий предыдущий.

Достоинством асинхронных счетчиков являются простота схемы, а недостатком — низкое быстродействие, так как триггеры переключаются поочередно. В худшем случае перенос распространяется по всей схеме от младшего разряда к старшему, т.е. для установления нового состояния должны переключится последовательно все триггеры. Из этого следует, что время установления кода в асинхронном счетчике с последовательным переносом составит величину tуст = ntзд. тт, где tзд. тт — средняя задержка триггера, а максимальная частота входных импульсов fмакс ≤ 1/ ntзд. тт.

Максимальная частота входных импульсов в режиме деления частоты ограничивается быстродействием триггера младшего разряда, так как все последующие триггеры переключаются с более низкими частотами.

Особенностью асинхронных двоичных счетчиков с последовательным переносом является возникновение промежуточных (ложных) состояний при переходных процессах из-за задержек переключения триггеров [4].

Для построения вычитающего счетчика счетный вход триггеров старших разрядов следует соединить с инверсными выходами  соседних младших разрядов (рисунок 27).

соседних младших разрядов (рисунок 27).

2015-02-27

2015-02-27 7227

7227