Наибольшее практическое значение среди счетчиков с недвоичным кодированием состояний имеют счетчики с кодом Грея, счетчики Джонсона и счетчики с кодом «1 из N».

Особенности счетчиков в коде Грея были рассмотрены выше. Счетчики в коде «1 из N» находят применение в системах синхронизации, управления и других ЦУ. На их основе получают импульсные последовательности с заданными временными диаграммами. Для этого можно вначале разбить период временной диаграммы на части («кванты»), соответствующие минимальному интервалу временной диаграммы, применив задающий генератор с частотой, равной m/T, где m — число «квантов» в периоде диаграммы T. Выходные импульсы задающего генератора затем распределяются во времени и пространстве так, что каждый «квант» появляется в свое время и в своем пространственном канале.

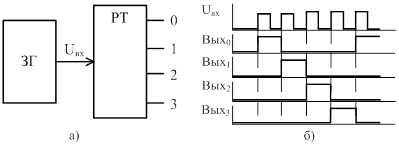

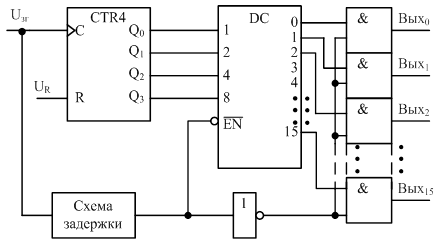

Счетчик в коде «1 из N» имеет один вход, на который подаются импульсы задающего генератора, и N выходов. Причем первый импульс генератора передается на первый выход счетчика (канал), второй импульс — во второй канал и т.д. Структура такого счетчика, называемого также распределителем тактов (РТ), и временные диаграммы его работы показаны на рисунке 36, причем временная диаграмма на рисунке 36, б соответствует режиму распределения уровней (РУ) (паузы между активными состояниями каналов отсутствуют), а диаграмма на рисунке 36, в — режиму распределения импульсов (РИ).

Рисунок 36 — Распределитель тактовых сигналов. Структурная схема (а) и временные диаграммы распределения уровней (б) и импульсов (в)

Распределители импульсов реализуются на основе РУ путем включения в их выходные цепи конъюнкторов, на вторые входы которых подаются импульсы задающего генератора.

Имея распределенные во времени и пространстве «кванты», можно с помощью логических элементов ИЛИ собирать из них импульсные последовательности с необходимыми временными диаграммами. Часто нужны именно те последовательности, которые вырабатываются непосредственно распределителями тактов.

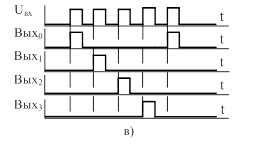

Распределителем тактов (РТ) является регистр сдвига, замкнутый в кольцо, если записанное в регистр слово содержит всего одну единицу. При сдвигах единица перемещается с одного выхода на другой, циркулируя в кольце. Число выходов РТ равно разрядности регистра. Недостаток схемы — потеря правильного функционирования при сбое. Возможны варианты с самовосстановлением работы РТ на кольцевом регистре. Работа схемы такого РТ (рисунок 37) основана на том, что на последовательный вход регистра подаются нули, пока в нем имеется хотя бы одна единица. Таким образом, лишние единицы будут устранены. Когда регистр очистится, сформируется сигнал записи единицы на его входе. Следовательно, потеря единственной единицы также будет исключена. Выход логического элемента ИЛИ-НЕ, выполняющего самовосстановление схемы, дает еще один дополнительный канал.

Рисунок 37 — Логическая схема распределителя с автоматическим вхождением в рабочий цикл

На рисунке 37 показаны также цепи пуска/останова РТ и два варианта выходов для РУ (непосредственно с триггеров и логического элемента ИЛИ-НЕ) и РИ (после стробирования сигналов РУ импульсами задающего генератора (ЗГ) на цепочке конъюнкторов). Существуют схемы РТ с быстрым исправлением сбоев [4].

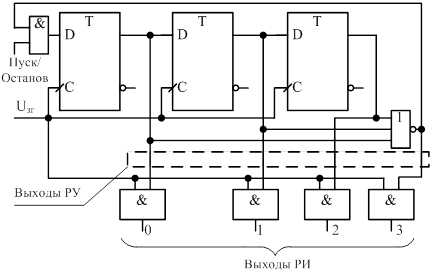

Распределители на кольцевых регистрах находят применение при малом числе выходных каналов. Их достоинством является высокое быстродействие (задержка перехода в новое состояние равна времени переключения одного триггера). При большом числе выходных каналов возрастают аппаратурные затраты, в этом случае обычно используют распределители на основе двоичного счетчика и дешифратора (рисунок 38).

Рисунок 38 — Логическая схема распределителя импульсов на основе двоичного счетчика и дешифратора

В схеме РИ на рисунке 38 использован двоичный счетчик, в котором при переключении из одного состояния в другое возможны промежуточные состояния, что приведет к появлению ложных выходных сигналов. Для предотвращения появления ложных сигналов запрещается работа дешифратора на время, необходимое для переключения счетчика в конечное состояние путем подачи задержанного входного импульса на разрешающий вход  (схема задержки содержит нечетное число инверторов).

(схема задержки содержит нечетное число инверторов).

Достоинством схемы распределителя импульсов на рисунке 38 являются малые аппаратурные затраты, а недостатком — более низкое быстродействие в сравнении со схемой на рисунке 37.

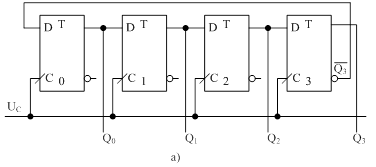

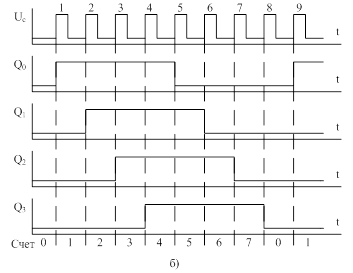

Счетчик Джонсона представляет собой кольцевой регистр сдвига с перекрестной обратной связью. Он имеет 2n состояний, т.е. при той же разрядности вдвое больше, чем обычный кольцевой регистр. В то же время выход счетчика Джонсона представлен не в коде «1 из N», что требует преобразования кодов для получения выходов распределителя тактов. Такие преобразователи очень просты, что и обуславливает применение счетчиков Джонсона в составе распределителей. Показанный на рисунке 39 четырехразрядный счетчик Джонсона при начальном нулевом состоянии работает следующим образом. Первый тактовый импульс Uc установит первый триггер Т0 в единичное состояние (Q0 = 1), так как  , в остальных разрядах будут нули как результат сдвига нулей от соседних слева разрядов. Второй импульс Uc сохраняет единичное состояние триггера Т0, так как по-прежнему

, в остальных разрядах будут нули как результат сдвига нулей от соседних слева разрядов. Второй импульс Uc сохраняет единичное состояние триггера Т0, так как по-прежнему  . Второй триггер Т1 окажется в единичном состоянии (Q1 = 1), поскольку примет единицу от первого триггера Т0. Остальные разряды Q2 и Q3 будут нулевыми. Последующие сдвиги приведут к заполнению единицами всех разрядов счетчика. Пятый импульс Uc (рисунок 39, б) установит первый разряд Q0 в нуль, так как теперь

. Второй триггер Т1 окажется в единичном состоянии (Q1 = 1), поскольку примет единицу от первого триггера Т0. Остальные разряды Q2 и Q3 будут нулевыми. Последующие сдвиги приведут к заполнению единицами всех разрядов счетчика. Пятый импульс Uc (рисунок 39, б) установит первый разряд Q0 в нуль, так как теперь  . Этим начинается процесс распространения «волны нулей». После восьми импульсов повторится состояние 0000, с которого было начато рассмотрение работы счетчика и т.д.

. Этим начинается процесс распространения «волны нулей». После восьми импульсов повторится состояние 0000, с которого было начато рассмотрение работы счетчика и т.д.

Рисунок 39 – Четырехразрядный счетчик Джонсона. Логическая схема (а) и временные диаграммы работы (б)

Особенность рассмотренной схемы — четное число состояний при любом числе разрядов n. Обычный кольцевой регистр такого ограничения не имеет. Для получения нечетного числа состояний можно исключить одно лишнее состояние одним из способов, которые были рассмотрены выше.

ЛИТЕРАТУРА

1 Калабеков, Б. А. Цифровые устройства и микропроцессорные системы: учеб. для техникумов связи / Б. А. Калабеков. – М.: Горячая линия – Телеком, 2002. – 336 с.

2 Калабеков, Б. А. Цифровые устройства и микропроцессорные системы: учеб. для техникумов связи / Б. А. Калабеков, И. А. Мамзелев. – М.: Радио и связь, 1987. – 400 с.

3 Лысиков, Б. Г. Цифровая и вычислительная техника: учеб. для техникумов связи / Б. Г. Лысиков. – Мн.: УП Экоперспектива, 2002. – 264 с.

4 Угрюмов, Е. П. Цифровая схемотехника: учеб. пособие для вузов / Е. П. Угрюмов. – СПб.: БХВ-Петербург, 2002. – 582 с.

5 Цифровые и микропроцессорные устройства: лабораторный практикум для студентов специальностей 2-45 01 03 – Сети телекоммуникаций, 2‑45 01 02 – Системы радиосвязи, радиовещания и телевидения. В 4 ч. / сост. В. И. Богородов. – Минск: ВГКС, 2009. – Ч. 1 – 84 с.; Ч. 2 – 65 с.

6 Цифровые интегральные микросхемы: справочник, 2-е изд., перераб. и доп. / М. И. Богданович [и др.]. – Мн.: Беларусь, Полымя, 1996. – 605 с.

2015-02-27

2015-02-27 3660

3660