Спроектировать последовательностное устройство - счетчик с произвольным порядком счета для использования в автомате управления текущим процессом. Входные сигналы: НУ - начальная установка и С - переход к определенному состоянию. Выходные сигналы: Q3, Q2, Q1. Десятичные коды последовательности выходных сигналов Q равны 4, 3, 7, 6, 5, 2, 0, 1 (проектирование на JK триггерах). Первый вход указывает исходное состояние выходов. Счетчик должен осуществлять циклический счет в соответствии с заданной последовательностью выходных сигналов.

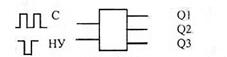

Изображаем проектируемое устройство как функциональныйблок (рисунок 4 ) и указываем входные и выходные сигналы.

|

Рисунок 4 - Проектируемое последовательностное устройство какфункциональный блок

Составляем таблицу состояний проектируемого устройства (таблица 7), и которой будут представлены входные и выходные сигналы.

Таблица 7 - Таблица состояний

| N | С | Q3 | Q2 | Q1 |

| Исх. 1 | ||||

| 1П | ||||

| 1П | ||||

| 1П | ||||

| 1П | ||||

| 1П | ||||

| 1П | ||||

| 1П |

Заданное устройство должно иметь8 состояний, их обеспечивают 3 JK триггера.

Нa основе таблицы состояний строим таблицу переходов счётчика (таблица 8). Таблица переходов позволяет построить таблицу управляющих сигналов, применяемых в проектируемом устройстве (таблица 10). Для ее построения используется характеристическая таблица JK триггеров (таблица 9).

Таблица 8 – Таблица переходов счетчика

| Q3 | Q2 | Q1 | Q3(t) ® Q3(t+1) | Q2(t) ® Q2(t+1) | Q1(t) ® Q1(t+1) |

| 1®0 | 0®1 | 0®1 | |||

| 0®1 | 1®1 | 1®1 | |||

| 1®1 | 1®1 | 1®0 | |||

| 1®1 | 1®0 | 0®1 | |||

| 1®0 | 0®1 | 1®0 | |||

| 0®0 | 1®0 | 0®0 | |||

| 0®0 | 0®0 | 0®1 | |||

| 0®1 | 0®0 | 1®0 |

Таблица 9 - Характеристическая таблица JK триггера

| J(t) | K(t) | Q(t) ®Q(t+1) |

| X | 0®0 | |

| X | 0®1 | |

| X | 1®0 | |

| X | 1®1 |

Таблица 10 - Таблица управляющих сигналов счетчика

| Q3 | Q2 | Q1 | J3 | КЗ | J2 | К2 | J1 | К1 • |

| ф | Ф | Ф | ||||||

| ф | Ф | Ф | ||||||

| ф | Ф | Ф | ||||||

| ф | Ф | Ф | ||||||

| I | ф | Ф | Ф | |||||

| ф | Ф | Ф | ||||||

| ф | Ф | Ф | ||||||

| ф | Ф | Ф |

Таблица 10 является таблицей истинности комбинаций схем выработки сигналов J и К. для каждого из триггеров по сигналам Q.

Осуществляем минимизацию для построения комбинационных схем управления триггерами (рисунок 5).

Q3

| Q3\Q2 Q1 |  00 00

|  01 01

| ||

| 1Ф | 1Ф | 1Ф | 0Ф | |

| Ф1 | Ф1 | Ф0 | Ф0 |

Q2

| Q3\Q2 Q1 |  00 00

|  10 10

| ||

0Ф 0Ф

| 0Ф | Ф0 | Ф1 | |

| 1Ф | 1Ф | Ф0 | Ф1 |

Q1

| Q3\Q2 Q1 |   00 00

| |||

0 0

|  0Ф 0Ф

| 1Ф | 1Ф | 0Ф |

| Ф1 | Ф1 | Ф0 | Ф0 |

Рисунок 5. Карты Карно для JK триггера

В соответствии с картами Карно (рисунок 5) составляем функционирования счетчика и переводим их в базис «И-НЕ», используя теорему Де Моргана:

Q3: J3 = Q1 Q2: J2 = Q3 Q1: J1 = Q2 + Q3 =

K3 =  K2 =

K2 =  K1 = Q2 + Q3 =

K1 = Q2 + Q3 =

Рассчитываем по уравнениям и представляем в таблице 11 значения входных и выходных сигналов триггеров.

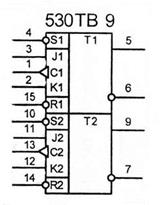

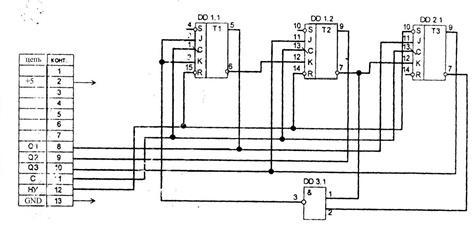

Выбираем из справочника микросхемы триггеров 530ТВ9 - два JK. триггера. Изображение микросхемы представлено на рисунке 6. Для построения устройства также необходима микросхема К155ЛА3, так как она содержит элемент И-НЕ,

Назначение выводов интегральной микросхемы 530ТВ9 представлено в таблице 12. Электрические параметры интегральной микросхемы 530ТВ9 представлены в таблице 13

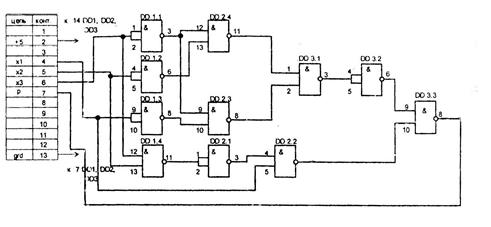

По результатам минимизации строим схему электрическую принципиальную, изображенную в приложении Б.

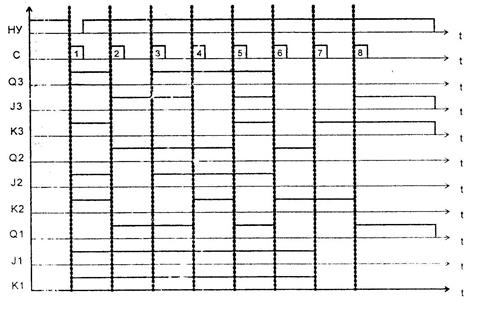

Значение сигналов Q, J и К после сигнала НУ и по сигналам перехода к следующим состояниям рассчитаны по уравнениям состояния счетчика. Результаты расчета сведены в таблицу 11. Соответствующие графики приведены на рисунке 7.

Таблица 11 - Таблица сигналов Q, J и К по тактам

| N | С | Q3 | Q1 | J3 | КЗ | J2 | К2 | J1 | К1 | |

| S | ||||||||||

| Исх | - | |||||||||

| О | ||||||||||

|

Рисунок 6 – Микросхема 530ТВ9

Таблица 12 – Назначение выводов интегральной микросхемы 530ВТ9

| Номер вывода | Обозначение | Назначение |

| 1, 13 | CI, C2 | Входы сброса состояния триггеров |

| 2, 12 | К1, К2 | Входы сигнала К |

| 3, 1 | J1, J2 | Входы сигнала J |

| 4,10 | S1, S2 | Входы сигнала НУ |

| 5, 9 | Q | Выходы сигнала результата |

| 6, 7 | q(инверсное) | Выходы сигнала результата в инверсном состоянии |

| GND | Общий | |

| 14, 15 | R1, R2 | Входы сигнала НУ |

| Ucc | Напряжение питания |

Таблица 13 - Электрические параметры интегральной микросхемы 530ТВ9

| Параметр | Значение |

| Входной ток низкого уровня | £ -2 мА |

| Входной ток высокого уровня | 0,05 мА |

| Выходное напряжение низкого уровня | 0,5В |

| Выходное напряжение высокого уровня | 2,7 В |

| Время задержки | 7 нс |

| Мощность потребления | 19 мВт |

| Номинальное напряжение | 0,5 В |

| Максимальное напряжение питания | 5,5В |

| Максимальное напряжение питания на входе | 5В |

| Максимальное напряжение, приложенное к выходу закрытой схемы | 5,5В |

| Минимальное напряжение питания на входе | -0,4В |

| Максимальная емкость нагружен | 150 пФ |

|

Рисунок 7 - Графики работы счетчиков на JK триггерах

Варианты заданий

Задание 1 на проектирование комбинационного устройства представлено набором цифр Его выходной сигнал Р равен 1 при подаче на входсигналов ХЗ, Х2, XI, сочетание которых является двоичным кодом заданных цифр. Для остальных сочетаний входных сигналов Р = 0.

Задание 2 на проектирование последователь костного устройства также задано набором цифр и указанием на основе какого триггера выполнять проектирование. Выходных сигналов устройства три: 03, Q2, Q1. Цифры задания указывают последовательность значений этих сигналов С. Первым поступает сигнал на установки, который должен обеспечить сочетание сигналов Q первое среди указанных.

В таблиц: 16 указаны варианты заданий дли выполнения курсовою проекта студентами 4 курса.

Таблица 16 - варианты задания

| № п/п | Знание 1. Проектирование комбинационного устройства. | Задание 2. Проектирование последователь костного устройства. |

| 0, 3, 5, 7 | 6, 1, 3, 0, 5 JK | |

| 0, 1, 3, 6 | 4, 2, 3, 6, 7, 5 JK | |

| 0, 1, 3, 4, 7 | 6, 4, 3, 0, 2, 1, 7 JK | |

| 1, 3, 4, 7 | 0, 2, 4,3, 1, 6, 5, 7 JK | |

| 1, 2, 3, 5, 6 | 2, 4, 1, 3, 5, 7, 6, 0 JK | |

| 0, 1, 3, 6, 7 | 1, 7, 4, 6, 0, 3, 2 JK | |

| 1, 2, 3, 4 | 1, 4, 3, 7, 6, 5, 0, 2 JK | |

| 0, 1, 2, 7 | 4, 3, 1, 6, 5, 7, 2 JK | |

| 0, 2, 3, 5, 7 | 6, 1, 3, 4, 2, 7 JK | |

| 1, 3, 5, 6 | 3, 4, 5, 2, 0, 1, 7, 6 JK | |

| 0, 2, 3, 4, 7 | 6, 1, 7, 2, 3 JK | |

| 0, 1, 2, 6, 7 | 3, 5, 2, 1, 0, 7, 4, 6 JK | |

| 2, 4, 5, 7 | 7, 6, 4, 5, 3, 1 JK | |

| 0, 3, 4, 5 | 2, 4, 3, 7, 6, 5, 1, 0 JK | |

| 1, 2, 5, 6, 7 | 5, 6, 3, 3, 0, 1, 7, 4 JK | |

| 0, 3, 5, 7 | 5, 2, 7, 1, 3, 6 JK | |

| 1, 3, 4, 6, 7 | 1, 7, 3, 6, 4, 5, 0, 2 JK | |

| 1, 2, 3, 4, 5 | 7, 6, 3, 5, 4, 2 JK | |

| 0, 1, 5, 6 | 5, 6, 0, 3, 7 JK | |

| 1, 2, 4, 5 | 7, 4, 3, 5, 1, 0, 2, 6 JK | |

| 1, 3, 4, 5, 6 | 3, 4, 5, 0, 7, 6 JK | |

| 1, 2, 5, 7 | 4, 5, 6, 3, 2, 1, 7 JK | |

| 0, 1, 3, 4, 6 | 1, 3, 2, 5, 7, 6, 0, 4 JK | |

| 0, 2, 3, 4, 5 | 5, 3, 6, 1, 0, 2, 7, 4 JK | |

| 0, 4, 5, 6 | 7, 5, 6, 3, 4, 0, 1, 2 JK | |

| 1, 2, 6, 7 | 3, 0, 2, 1, 6, 4, 7 JK | |

| 2, 3, 4, 7 | 4, 0, 6, 1, 7 JK |

Литература

1 Зельдин Е.А. Цифровые интегральные микросхемы в информационно-измерительной аппаратуре. Л.: Энергоатомиздат, 1986. - 280 с.

2 Интегральные микросхемы: Справочник/Б.В. Тарабрин, С.В. Якубовский, Н.А. Барканов и др.; под ред. Б.В. Тарабрина. М.: Энергоатомиздат, 1985. - 528 с.

3 Разработка и оформление конструкторской документации: Справочник РЭА/Э.Т.

4 Романычева, А.К. Иванова, А.С. Куликов и др.; под ред. Э.Т. Романычевой. М Радио и связь, 1989. - 448 с.

5 Сигорский В.П. Математический аппарат инженера. Киев: Техника, 1975. - 768 с.

6 Токхейм Р. Основы цифровой электроники; пер. с англ. М.: Мир, 1988, - 392 с.

Приложение А - Электрическая принципиальная схема комбинационного устройства цифровой электронной техники

|

Приложение Б - Электрическая принципиальная схема последовательностного устройства цифровой электронной техники

2015-04-30

2015-04-30 770

770