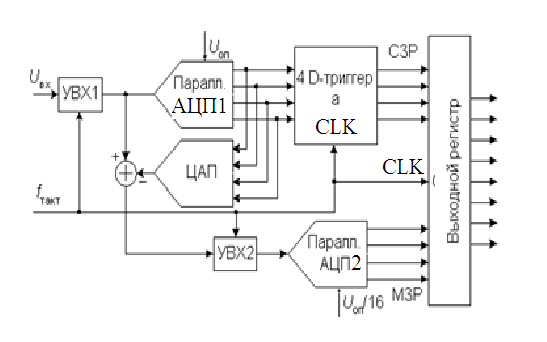

Быстродействие многоступенчатого АЦП можно повысить, применив конвейерный принцип многоступенчатой обработки входного сигнала. В обыкновенном многоступенчатом АЦП (рис.2.13) вначале происходит формирование старших разрядов выходного слова преобразователем АЦП1, а затем идет период установления выходного сигнала ЦАП. На этом интервале АЦП2 простаивает. На втором этапе во время преобразования остатка преобразователем АЦП2 простаивает АЦП1. Введя элементы задержки аналогового и цифрового сигналов между ступенями преобразователя, можно получить конвейерный АЦП, схема 8-разрядного варианта которого приведена на рис.2.13.

Рис..2.13. Структурная схема конвейерного АЦП

Роль аналогового элемента задержки выполняет устройство выборки-хранения УВХ2, а цифрового - четыре D-триггера. Триггеры задерживают передачу старшего полубайта в выходной регистр на один период тактового сигнала CLK.

Конвейерная архитектура позволяет существенно (в несколько раз) повысить максимальную частоту выборок многоступенчатого АЦП. То, что при этом сохраняется суммарная задержка прохождения сигнала, соответствующая обычному многоступенчатому АЦП с равным числом ступеней, не имеет существенного значения, так как время последующей цифровой обработки этих сигналов все равно многократно превосходит эту задержку. За счет этого можно без проигрыша в быстродействии увеличить число ступеней АЦП, понизив разрядность каждой ступени. В свою очередь, увеличение числа ступеней преобразования уменьшает сложность АЦП. Действительно, например, для построения 12-разрядного АЦП из четырех 3-разрядных необходимо 28 компараторов, тогда как его реализация из двух 6-разрядных потребует 126 компараторов.

Конвейерную архитектуру имеет большое количество выпускаемых в настоящее время многоступенчатых АЦП.

2015-06-04

2015-06-04 872

872