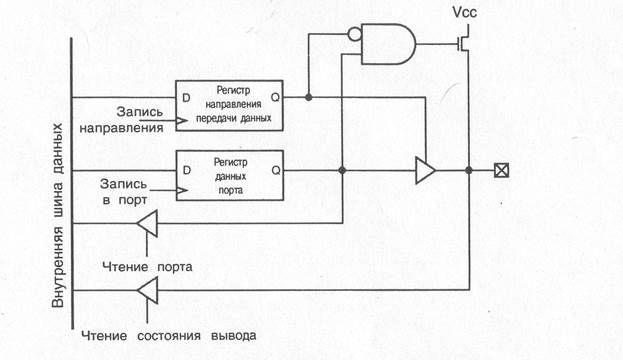

Рассмотрим организацию параллельного ввода-вывода простейшего AVR микроконтроллера. Схема подключения внешнего вывода, показанная на рис. 3, дает представление о его работе.

Рисунок 3 Схема подключения внешнего вывода AVR

С каждым набором линий (который называется «портом») связано три адреса ввода-вывода, которые позволяют определять значение данных, записанных в порт, направление передачи данных («I» — вывод, «О» — ввод) и реальное значение сигнала на внешнем выводе. Вследствие этого есть возможность «подтянуть» выводы порта к высокому потенциалу для работы в режиме ввода данных, и использовать состояние некоторых выводов в качестве запроса прерываний.

Чтение данных может быть выполнено либо непосредственно с внешнего вывода, либо с выхода регистра данных порта. Такая возможность является важной особенностью работы порта. Если внешняя линия перегружена или случайно закорочена на «землю» или питание, то состояние внешнего выхода никогда не будет меняться. Поэтому в некоторых случаях очень важно иметь возможность прочитать содержимое регистра порта и сравнить его с реальным состоянием внешнего вывода.

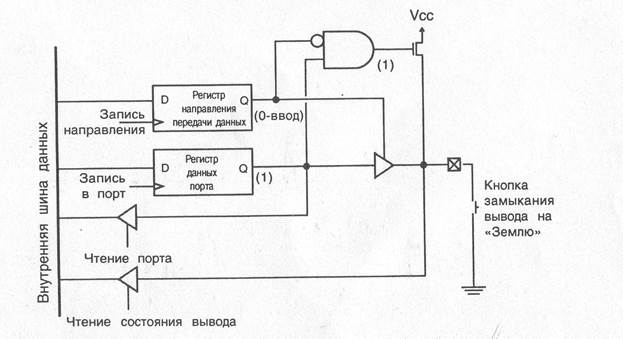

Хотя линии ввода-вывода AVR работают подобно аналогичным линиям в других микроконтроллерах, они имеют одно существенное отличие. Оно заключается в том, что «подтягивание» внешнего вывода к высокому потенциалу управляется не отдельными битами регистра, а для этого используется специальная комбинационная схема. Эта схема разрешает «подтягивание» только, когда внешний вывод работает в режиме ввода данных. На рис.4 показано, как работает линия ввода-вывода АУК при чтении состояния кнопки, которая подключает внешний вывод к «земле».

Рисунок 4 Подключение внешнего вывода к кнопке

Рассмотрим принцип работы портов ввода-вывода сначала на примере порта B.

Порт B 8-разрядный двунаправленный порт ввода/вывода. Для обслуживания порта отведено три регистра: регистр данных PORTB ($18, $38), регистр направления данных - DDRB ($17, $37) и ножки порта B ($16, $36). Адрес ножек порта B предназначен только для чтения, в то время как регистр данных и регистр направления данных - для чтения/записи.

Все выводы порта имеют отдельно подключаемые подтягивающие резисторы. Выходы порта B могут поглощать ток до 20 mA и непосредственно управлять светодиодными индикаторами. Если выводы PB0..PB7 используются как входы и замыкаются на землю, если включены внутренние подтягивающие резисторы, выводы являются источниками тока (Iil). Дополнительные функции выводов порта B приведены в таблице 8.

Таблица 16. Альтернативные функции выводов порта B

┌────────┬──────────────────────────────────────────────────────────┐

│Вывод │ Альтернативная функция │

├────────┼──────────────────────────────────────────────────────────┤

│PB0 │ AIN0 (Положительный вход аналогового компаратора) │

├────────┼──────────────────────────────────────────────────────────┤

│PB1 │ AIN1 (Отрицательный вход аналогового компаратора) │

├────────┼──────────────────────────────────────────────────────────┤

│PB3 │ OC1 (Выход совпадения таймера/счетчика1) │

├────────┼──────────────────────────────────────────────────────────┤

│PB5 │ MOSI (Вход данных для загрузки памяти) │

├────────┼──────────────────────────────────────────────────────────┤

│PB6 │ MISO (Выход данных для чиенмя памяти) │

├────────┼──────────────────────────────────────────────────────────┤

│PB7 │ SCK (Вход тактовых импульсов последовательного обмена) │

└────────┴──────────────────────────────────────────────────────────┘

При использовании альтернативных функций выводов, регистры DDRB и PORTB должны быть установлены в соответствии с описанием альтернативных функций.

РЕГИСТР ДАННЫХ ПОРТА B - PORTB

Бит 7 6 5 4 3 2 1 0

┌──────┬──────┬──────┬──────┬──────┬──────┬──────┬──────┐

$18 ($38) │PORTB7│PORTB6│PORTB5│PORTB4│PORTB3│PORTB2│PORTB1│PORTB0│

└──────┴──────┴──────┴──────┴──────┴──────┴──────┴──────┘

Чт./зап. R/W R/W R/W R/W R/W R/W R/W R/W

Нач.знач. 0 0 0 0 0 0 0 0

РЕГИСТР НАПРАВЛЕНИЯ ДАННЫХ ПОРТА B - DDRB

Бит

┌──────┬──────┬──────┬──────┬──────┬──────┬──────┬──────┐

$17 ($37) │ DDB7 │ DDB7 │ DDB5 │ DDB4 │ DDB3 │ DDB2 │ DDB1 │ DDB0 │

└──────┴──────┴──────┴──────┴──────┴──────┴──────┴──────┘

Чт./зап. R/W R/W R/W R/W R/W R/W R/W R/W

Нач.знач. 0 0 0 0 0 0 0 0

ВЫВОДЫ ПОРТА B - PINB

Бит

┌──────┬──────┬──────┬──────┬──────┬──────┬──────┬──────┐

$16 ($36) │PINB7 │PINB7 │PINB5 │PINB4 │PINB3 │PINB2 │PINB1 │PINB0 │

└──────┴──────┴──────┴──────┴──────┴──────┴──────┴──────┘

Чт./зап. R R R R R R R R

Нач.знач. Hi-Z Hi-Z Hi-Z Hi-Z Hi-Z Hi-Z Hi-Z Hi-Z

PINB не является регистром, по этому адресу осуществляется доступ к физическим значениям каждого из выводов порта B. При чтении PORTB, читаются данные из регистра-защелки, при чтении PINB читаются логические значения присутствующие на выводах порта.

ПОРТ B, КАК ПОРТ ВВОДА/ВЫВОДА ОБЩЕГО НАЗНАЧЕНИЯ

Все 8 бит порта B при использовании для ввода/вывода одинаковы.

Бит DDBn регистра DDRB выбирает направление передачи данных. Если бит установлен (1), вывод сконфигурирован как выход. Если бит сброшен(0) - вывод сконфигурирован как вход. Если PORTBn установлен и вывод сконфигурирован как вход, включается КМОП подтягивающий резистор. Для отключения резистора, PORTBn должен быть сброшен (0) или вывод должен быть сконфигурирован как выход.

Таблица 17. Влияние DDBn на выводы порта B

┌────┬──────┬───────┬───────────┬───────────────────────────────────┐

│DDBn│PORTBn│Вх/Вых │Подт.резист│Комментарий │

├────┼──────┼───────┼───────────┼───────────────────────────────────┤

│0 │0 │Вход │Нет │Третье состояние (Hi-Z) │

├────┼──────┼───────┼───────────┼───────────────────────────────────┤

│0 │1 │Вход │Да │PBn источник тока Iil, если извне │

│ │ │ │ │соединен с землей │

├────┼──────┼───────┼───────────┼───────────────────────────────────┤

│1 │0 │Выход │Нет │Выход установлен в 0 │

├────┼──────┼───────┼───────────┼───────────────────────────────────┤

│1 │1 │Выход │Нет │Выход установлен в 1 │

└────┴──────┴───────┴───────────┴───────────────────────────────────┘

n = 7,6...0 - номер вывода

АЛЬТЕРНАТИВНЫЕ ФУНКЦИИ PORTB

SCK - PORTB, Bit 7 - вход тактовой частоты для загрузки/чтения памяти.

MISO - PORTB, Bit 6 - выход данных для чтения памяти

MOSI - PORTB, Bit 5 - вход данных для загрузки памяти

OC1 - PORTB, Bit 3 - Выход совпадения. Этот вывод может быть сконфигурирован для внешнего вывода события совпадения таймера1. Для этого бит DDB3 должен быть установлен в 1 (вывод сконфигурирован как выход).

AIN1 - PORTB, Bit 1 - Отрицательный вход аналогового компаратора. Если этот вывод сконфигурирован как вход (DDB1=0) и отключен внутренний подтягивающий резистор, этот вывод работает как отрицательный вход внутреннего аналогового компаратора.

AIN0 - PORTB, Bit 0 - Положительный вход аналогового компаратора. Если этот вывод сконфигурирован как вход (DDB0=0) и отключен внутренний подтягивающий резистор, этот вывод работает как положительный вход внутреннего аналогового компаратора.

Порт D

Для порта D зарезервированы 3 ячейки памяти - регистр PORTD $12 ($32), регистр направления данных - DDRD $11 ($31) и выводы порта D - PIND $10 ($30). Регистры данных и направления данных могут читаться/записываться, ячейка PIND - только для чтения.

Порт D - 7-разрядный двунаправленный порт с встроенными подтягивающими регистрами. Выходные буферы порта могут поглощать ток до 20 mA. Если выводы используются как входы и на них подан низкий уровень, они являются источниками тока Iil, если подключены подтягивающие резисторы. Некоторые из выводов порта имеют альтернативные функции, как показано в таблице 18.

Если выводы порта используются для обслуживания альтернативных функций, они должны быть сконфигурированы на ввод/вывод в соответствии с описанием функции.

Таблица 18. Альтернативные функции порта D

┌───────────┬────────────────────────────────────────┐

│Вывод порта│Альтернативная функция │

├───────────┼────────────────────────────────────────┤

│ PD0 │ RXD (вход данных UART) │

├───────────┼────────────────────────────────────────┤

│ PD1 │ TXD (выход данных UART) │

├───────────┼────────────────────────────────────────┤

│ PD2 │ INT0 (вход внешнего прерывания 0) │

├───────────┼────────────────────────────────────────┤

│ PD3 │ INT1 (вход внешнего прерывания 1) │

├───────────┼────────────────────────────────────────┤

│ PD4 │ T0 (внешний вход таймера счетчика 0) │

├───────────┼────────────────────────────────────────┤

│ PD5 │ T1 (внешний вход таймера счетчика 1) │

├───────────┼────────────────────────────────────────┤

│ PD6 │ ICP (вход захвата таймера счетчика 1)│

└───────────┴────────────────────────────────────────┘

РЕГИСТР ДАННЫХ ПОРТА D - PORTD

Бит

┌──────┬──────┬──────┬──────┬──────┬──────┬──────┬──────┐

$12 ($32) │ - │PORTD6│PORTD5│PORTD4│PORTD3│PORTD2│PORTD1│PORTD0│

└──────┴──────┴──────┴──────┴──────┴──────┴──────┴──────┘

Чт./зап. R R/W R/W R/W R/W R/W R/W R/W

Нач.знач. 0 0 0 0 0 0 0 0

РЕГИСТР НАПРАВЛЕНИЯ ДАННЫХ ПОРТА B - DDRB

Бит

┌──────┬──────┬──────┬──────┬──────┬──────┬──────┬──────┐

$11 ($31) │ - │ DDD7 │ DDD5 │ DDD4 │ DDD3 │ DDD2 │ DDD1 │ DDD0 │

└──────┴──────┴──────┴──────┴──────┴──────┴──────┴──────┘

Чт./зап. R R/W R/W R/W R/W R/W R/W R/W

Нач.знач. 0 0 0 0 0 0 0 0

ВЫВОДЫ ПОРТА B - PINB

Бит

┌──────┬──────┬──────┬──────┬──────┬──────┬──────┬──────┐

$10 ($30) │PIND7 │PIND7 │PIND5 │PIND4 │PIND3 │PIND2 │PIND1 │PIND0 │

└──────┴──────┴──────┴──────┴──────┴──────┴──────┴──────┘

Чт./зап. R R R R R R R R

Нач.знач. Hi-Z Hi-Z Hi-Z Hi-Z Hi-Z Hi-Z Hi-Z Hi-Z

PIND не является регистром, по этому адресу осуществляется доступ

к физическим значениям каждого из выводов порта D. При чтении PORTD, читаются данные из регистра-защелки, при чтении PIND читаются логические значения присутствующие на выводах порта.

Порт D, как порт ввода/вывода общего назначения

Бит DDDn регистра DDRD выбирает направление передачи данных. Если бит установлен (1), вывод сконфигурирован как выход. Если бит сброшен (0) - вывод сконфигурирован как вход. Если PORTDn установлен и вывод сконфигурирован как вход, включается КМОП подтягивающий резистор. Для отключения резистора, PORTDn должен быть сброшен (0) или вывод должен быть сконфигурирован как выход.

Таблица 19. Влияние DDDn на выводы порта D

┌────┬──────┬───────┬───────────┬───────────────────────────────────┐

│DDDn│PORTDn│Вх/Вых │Подт.резист│Комментарий │

├────┼──────┼───────┼───────────┼───────────────────────────────────┤

│0 │0 │Вход │Нет │Третье состояние (Hi-Z) │

├────┼──────┼───────┼───────────┼───────────────────────────────────┤

│0 │1 │Вход │Да │PDn источник тока Iil, если извне │

│ │ │ │ │соединен с землей │

├────┼──────┼───────┼───────────┼───────────────────────────────────┤

│1 │0 │Выход │Нет │Выход установлен в 0 │

├────┼──────┼───────┼───────────┼───────────────────────────────────┤

│1 │1 │Выход │Нет │Выход установлен в 1 │

└────┴──────┴───────┴───────────┴───────────────────────────────────┘

n = 6...0 - номер вывода

Альтернативные функции порта D

ICP - Порт D, бит 6 - вход захвата таймера/счетчика 1. Подробнее см. описание таймера.

T1 - Порт D, бит 5 - тактовый вход таймера/счетчика 1. Подробнее см. описание таймера.

T0 - Порт D, бит 4 - тактовый вход таймера/счетчика 0. Подробнее см. описание таймера.

INT1 - Порт D, бит 3 - вход внешних прерываний 1. Подробнее см. описание прерываний.

INT0 - Порт D, бит 2 - вход внешних прерываний 0. Подробнее см. описание прерываний.

TXD - Порт D, бит 1 - выход передатчика UART. Если разрешена работа передатчика UART, независимо от состояния DDRD1 этот вывод сконфигурирован как выход.

RXD - Порт D, бит 0 - выход приемника UART. Если разрешена работа приемника UART, независимо от состояния DDRD0 этот вывод сконфигурирован как выход. Когда UART использует вывод для приема данных, единица в PORTD0 подключает встроенный подтягивающий резистор.

2015-07-21

2015-07-21 1226

1226