Следующее поколение семейства ADSP 21ххх представлено микропроцессорами ADSP-21060 и ADSP-21062. Будучи сходными с МП ADSP-210xx по структуре ядра и совместимыми снизу-вверх по системе команд, они обладают существенными архитектурными отличиями, что позволило разработчикам выделить их в отдельное архитектурное семейство SHARC.

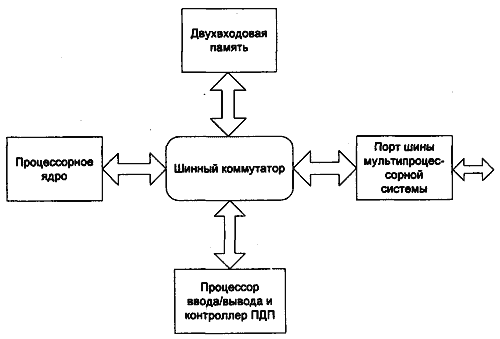

Рисунок 2 - Архитектура SHARC

На тактовой частоте 40 МГц производительность МП составляет 80 MIPS и 120 Mflops.

Шинный коммутатор соединяет ядро процессора с независимым процессором ввода/вывода, двухвходовой памятью и портом шины мультипроцессорной системы. Производятся также модули SHARCPAC и TRANSPAC, устанавливаемые в специальные разъемы материнских плат. Вычислительные модули на базе SHARC используются в системах радио - и гидролокации, в системах распознавания речи и обработки изображений, в средствах телекоммуникации и медицинской диагностики.

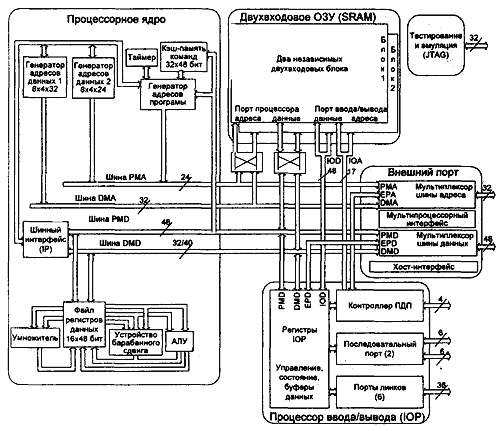

Рисунок 3 - Структура микропроцессора ADSP-2106X

Интерфейс с хост-процессором обеспечивает простое соединение со стандартной 16- или 32-разрядной микропроцессорной шиной. Передача данных через интерфейс осуществляется асинхронно, со скоростью, ограниченной тактовой частотой МП. Хост-интерфейс доступен через внешний порт и отображается в адресное пространство МП. 4 канала контроллера ПДП обеспечивают обмен данными и командами через хост-интерфейс с минимальным участием процессорного ядра.

ADSP-21060 имеет 2 синхронных последовательных порта для связи с периферийными устройствами. Максимальная скорость передачи данных через последовательный порт 40 Мбит/с. ADSP-21060 предоставляет разработчикам широкие возможности по созданию мультипроцессорных сигнальных систем. Общее адресное пространство может быть разделено между несколькими процессорами. Встроенная распределенная шинная логика позволяет создавать системы, содержащие до 6 взаимодействующих процессоров ADSP-21060 и хост-процессор. Межпроцессорное управление осуществляется с помощью механизма векторов прерывания. Загрузка микропроцессора может осуществляться из ПЗУ, хост-процессора.

МП с архитектурой SHARC семейства ADSP-2116X;

Следующей разработкой компании Analog Devices явились 32-разрядные МП семейства SHARC - ADSP-2116x, представленные в 1998 г.

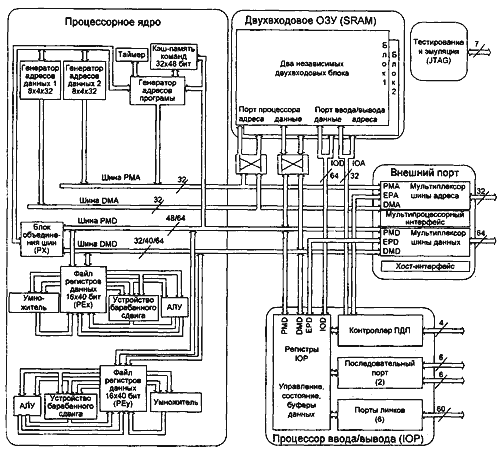

Основным отличием семейства ADSP-2116x от ADSP-2106x является наличие в составе микропроцессорного ядра двух процессорных элементов, а также является увеличенная разрядность внутренних шин.

Каждый процессорный элемент содержит набор обрабатывающих устройств: 32-, 40-разрядное арифметико-логическое устройство с фиксированной и плавающей точкой, 32-, 40-разрядный умножитель в формате с плавающей точкой с 80-разрядным регистром-аккумулятором, устройство барабанного сдвига, регистровый файл - 32 40-разрядных регистра.

Рисунок 4 - Структура микропроцессора ADSP-2116x

МП ADSP21160 является первым представителем новой серии. Он содержит 4 Мбит внутренней памяти, 14 каналов ПДП. Приведем основные характеристики данного микропроцессора:

· выполнение команд за один такт, в том числе, двумя вычислительными блоками, в SIMD-режиме;

· наличие сдвоенного генератора адреса;

· наличие команд ускорения обработки циклов;

· тактовая частота 100 МГц;

· пиковая производительность 600 Mflops;

· напряжение питания 2,5 В.

При относительно небольшой тактовой частоте высокая реальная производительность микропроцессоров ADSP-2116x достигается благодаря эффективной системе команд.

Таблица 2. Производительность микропроцессоров семейства SHARC

| ADSP-21065L SHARC | ADSP-21160 SISD | ADSP-21160 SIMD | |

| Тактовая частота | 66 МГц | 100 МГц | 100 МГц |

| Длительность такта | 15 нс | 10 нс | 10 нс |

| Mflops средняя | 132 Mflops | 200 Mflops | 400 Mflops |

| Mflops пиковая | 198 Mflops | 300 Mflops | 600 Mflops |

| Комплексное БПФ на 1024 точки | 274 мкс | 180 мкс | 90 мкс |

| Звено КИХ-фильтра | 15 нс | 10 нс | 5 нс |

| Звено БИХ-фильтра | 60 нс | 40 нс | 20 нс |

2015-08-21

2015-08-21 726

726