Принцип работы дешифратора

Обычно дешифратор имеет n-входов и 2n выходов, при этом n — разрядность дешифрируемого кода. Определенной комбинации на входе соответствует активный сигнал на одном из выходов, или при сигнале «00» — мы имеем «1» на нулевом выходе схемы; при «01» имеем — «1» на первом выходе, сигнал «10» трансформируется в 1 – на втором выходе и т.д. Другими словами, эти элементы схем могут преобразовывать двоичный код в различные системы исчисления (это может быть десятичная, шестнадцатеричная и пр.), поскольку все зависит от конкретной задачи, выполняемой микросхемой.

В стандартные типы дешифраторов входят модели на 4, 8 и 16 выходов, при этом на выходе — 2, 3 и 4 разрядов входного кода. Входы дешифраторов называют часто адресными, и на схемах нумеруют 1,2,4,8, при этом цифра соответствует весу двоичного кода. Сигнал на выходе 1,2,4,8 устанавливает номер активного выхода. С1,С2 – входы разрешения (или стробирования), которые работают с условием «и». Сигнал на этом входе сообщает о моменте срабатывания дешифратора. Также их можно использовать для увеличения разрядности логических устройств.

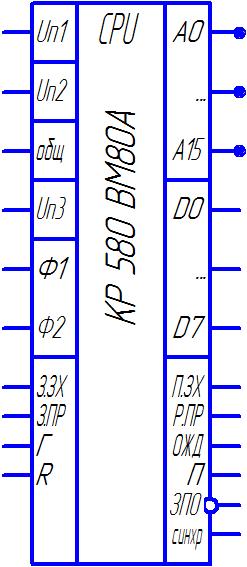

Микропроцессор КР580ВМ80А

Данный микропроцессор представляет собой однокристальный микропроцессор с тремя шинами: шестнадцатиразрядная шина адреса, двунаправленная восьмиразрядная шина данных, двенадцатиразрядная шина управления. Условно-графическое обозначение приведено на рис.1.

Рис.1 УГО МП КР580ВМ80А.

- шина адреса с тремя состояниями, которая предназначена для обращения к любой из 216 ячеек памяти или портам ввода/вывода.

- шина данных с тремя состояниями, которая предназначена для обмена данными между микропроцессором и периферийными устройствами.

П.ЗХ (подтверждение захвата) - единичный сигнал на этом выходе появляется в ответ на единичный сигнал, посылаемый от внешних устройств. При этом микропроцессор переходит в состояние «Захват», при котором ША и ШД переводятся в высокоомное состояние и микропроцессор отключен от всех шин. Эта особенность используется для реализации режима прямого доступа к памяти.

Р.ПР (разрешение прерывания) - на этот выход выдается состояние внутреннего триггера разрешения прерывания. Если на выходе РПР логическая единица, то микропроцессор способен воспринимать запросы на прерывание. Установка РПР осуществляется с помощью команд – EI (разрешить прерывание = уст. 1) и DI (запретить прерывание = сброс в 0). Запрос на прерывание не будет восприниматься, если не установлена 1, т.е. триггер или микропроцессор находится в состоянии «захват».

ОЖД (ожидание) - единичный сигнал на этом выходе информирует о том, что микропроцессор находится в состоянии ожидания, при котором остановлен процесс обработки.

(запись) - нулевой сигнал на этом выходе указывает на то, что данные микропроцессора выставлены на шину данных и могут быть восприняты внешними устройствами.

(прием) - единичный сигнал указывает на то, что микропроцессор готов к приему данных.

Синхр. - синхросигнал появляется на этом выходе в начале каждого машинного цикла.

Г (готов) - единичный сигнал на этом выходе приводит микропроцессор в режим обработки данных. При логическом нуле микропроцессор переходит в состояние ожидания, информируя об этом единицей на выходе ОЖД.

R (сброс) - единичный сигнал обнуляет программный счетчик, внутренние регистры прерывания и захвата. Состояние регистров блока РОН при этом не меняется.

З.ЗХ (HLD) – запрос захвата. Запрос на захват поступает от внешних устройств уровня логической единицы.

З.ПР (INT) – запрос прерывания. Запрос на прерывание поступает от внешних устройств и будет восприниматься только тогда, когда будет установлен в единицу внутренний триггер разрешения прерываний. Запрос не будет восприниматься, если МП находится в состоянии «захват» или на выходе Р.ПР установлен «0».

Ф1 и Ф2 - входы тактового генератора.

Динамика работы МП КР580ВМ80А следующая. Выполнение каждой команды в микропроцессоре производится в определенной последовательности, определенным кодом команды и синхронизируется во времени сигналами Ф1, Ф2 тактового генератора. Период синхросигналов Т1 и Т2 – называется машинным тактом. Длительность машинного такта устанавливается произвольно в пределах 0,5-1,6 мкс, что соответствует частоте 2 МГц-600 кГц.

| Таблица назначения выводов | |||

| Вывод | Обозначение | Тип вывода | Описание |

| 1 | A10 | Выход | Адресные шины микросхемы |

| 2 | GND | - | Общий |

| 3 | D4 | Вход/Выход | Шина данных микросхем (двунаправленныетрехстабильные) |

| 4 | D5 | ||

| 5 | D6 | ||

| 6 | D7 | ||

| 7 | D3 | ||

| 8 | D2 | ||

| 9 | D1 | ||

| 10 | D0 | ||

| 11 | -5В | - | Напряжение смещения подложки |

| 12 | CLR | Вход | Установка |

| 13 | RQ | Вход | Запрос шин |

| 14 | RQINT | Вход | Запрос прерывания |

| 15 | CLC2 | Вход | Сигнал тактового импульса |

| 16 | ACKINT | Выход | Подтверждение прерывания |

| 17 | IP | Выход | Прием |

| 18 | OP | Выход | Выдача |

| 19 | S | Вход | Синхронизация |

| 20 | 5В | - | Напряжение питания |

| 21 | ACKRQ | Выход | Подтверждение запроса прерывания |

| 22 | CLC1 | Вход | Общий |

| 23 | RDY | Вход | Готовность |

| 24 | WAIT | Выход | Ожидание |

| 25 | A0 | Выход | Адресные шины микросхемы |

| 26 | A1 | ||

| 27 | A2 | ||

| 28 | 12В | - | Напряжение питания |

| 29 | A3 | Выход | Адресные шины микросхемы |

| 30 | A4 | ||

| 31 | A5 | ||

| 32 | A6 | ||

| 33 | A7 | ||

| 34 | A8 | ||

| 35 | A9 | ||

| 36 | A15 | ||

| 37 | A12 | ||

| 38 | A13 | ||

| 39 | A14 | ||

| 40 | A11 | ||

2018-02-13

2018-02-13 1677

1677