В настоящее время семейство MCS-51 является лидером по количеству модификаций и выпускающих их компаний среди всех 8-разрядных микроконтроллеров. Оно получило свое название от микроконтроллера 8051, выпущенного в 1980 году компанией Intel на базе технологии n-МОП. На сегодняшний день существует более 200 модификаций микроконтроллеров семейства 8051. Эти модификации включают в себя кристаллы с широким спектром периферии: от простых 20-выводных устройств с одним таймером и 1К программной памяти до 100-выводных кристаллов с 10-разрядными АЦП, массивами таймеров-счетчиков, аппаратными 16-разрядными умножителями и 64К программной памяти на кристалле. Микросхемы для этого семейства производятся рядом фирм различных стран мира, включая Россию (семейства КР1816ВЕ, КР1830ВЕ и др.).

Архитектура семейства MCS-51 в значительной мере предопределяется ее назначением – построение компактных и дешевых цифровых устройств. Микроконтроллеры семейства MCS-51 позволяют выполнять как задачи управления различными устройствами, так и реализовывать отдельные узлы аналоговой схемы. Все микросхемы этого семейства работают с одной и той же системой команд, большинство из них выполняется в одинаковых корпусах с совпадающей цоколевкой, что позволяет использовать для разработанного устройства микросхемы разных фирм-производителей без переделки принципиальной схемы устройства и программы.

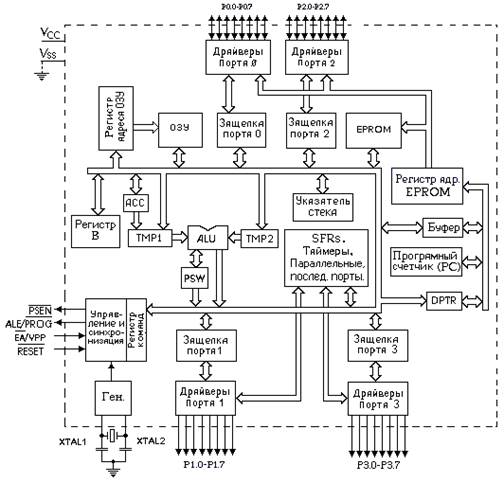

Структурная схема контроллера семейства MCS-51, представленная на рисунке 1.1, состоит из следующих функциональных узлов: блока управления, арифметико-логического устройства, блока таймеров/счетчиков, блока последовательного интерфейса и прерываний, программного счетчика, памяти данных и памяти программ. Двусторонний обмен осуществляется с помощью внутренней 8-разрядной магистрали данных. Различные микросхемы этого семейства различаются только регистрами специального назначения (в том числе и количеством портов). Система команд всех контроллеров семейства MCS-51 содержит 111 базовых команд с форматом 1, 2 или 3 байта и не изменяется при переходе от одной микросхемы к другой. Это обеспечивает переносимость программ с одной микросхемы на другую с минимальными трудностями.

Рисунок 1 – Структурная схема микроконтроллеров семейства MCS-51

Назначение узлов:

1) Блок управления и синхронизации предназначен для выработки синхронизирующих и управляющих сигналов, обеспечивающих координацию работы блоков ЭВМ во всех допустимых режимах ее работы. В состав блока управления входят: устройство формирования временных интервалов, логика ввода-вывода, регистр команд, регистр управления потреблением электроэнергии, дешифратор команд и логика управления ЭВМ.

а) устройство формирования временных интервалов предназначено для формирования внутренних синхросигналов фаз, тактов и циклов. Количество машинных циклов определяет продолжительность выполнения команд. Все команды ЭВМ выполняются за один-два машинных цикла (кроме умножения и деления, продолжительность выполнения которых составляет четыре цикла). Длительность машинного цикла составляет 12 периодов сигнала задающего генератора;

б) логика ввода-вывода предназначена для приема и выдачи сигналов, обеспечивающих обмен информации с внешними устройствами через порты ввода-вывода Р0-Р3 (квазидвунаправленные порты ввода-вывода, предназначенные для обеспечения обмена информацией ЭВМ с внешними устройствами, образуя 32 линии ввода-вывода);

в) регистр команд предназначен для записи и хранения 8-ми разрядного кода операции выполняемой команды. Код операции, с помощью дешифратора команд и логики управления ЭВМ, преобразуется в микропрограмму выполнения команды;

г) регистр управления потреблением (PCON) позволяет останавливать работу микроконтроллера для уменьшения потребления электроэнергии и уменьшения уровня помех от микроконтроллера. Еще меньших величин потребления и помех можно добиться, остановив задающий генератор микроконтроллера. Этого можно достичь при помощи переключения бита регистра управления потреблением PCON.

2) Арифметико-логическое устройство представляет собой параллельное восьмиразрядное устройство, обеспечивающее выполнение арифметических и логических операций. АЛУ состоит из регистров аккумулятора, регистров временного хранения TMP1 и TMP2, ПЗУ констант, сумматора, дополнительного регистра (регистра В), аккумулятора (ACC) и регистра состояния программ (PSW).

а) регистр аккумулятор и регистры временного хранения – восьмиразрядные регистры, предназначенные для хранения операндов на время выполнения операций над ними. Программно не доступны;

б) ПЗУ констант обеспечивает выработку корректирующего кода при двоично-десятичном представлении данных, кода маски при битовых операциях и кода констант;

в) параллельный восьмиразрядный сумматор представляет собой схему с последовательным переносом, предназначенную для выполнения арифметических операций сложения, вычитания и логических операций сложения, умножения, неравнозначности и тождественности;

г) регистр B – восьмиразрядный регистр, используемый во время операций умножения и деления. Для других инструкций он может рассматриваться как дополнительный сверхоперативный регистр;

д) аккумулятор – восьмиразрядный регистр, предназначенный для приема и хранения результата, полученного при выполнении арифметико-логических операций или операций сдвига;

е) регистр состояния программы (PSW) предназначен для хранения информации о состоянии АЛУ при выполнении программы.

3) Блок последовательного интерфейса и прерываний (ПИП) предназначен для организации ввода-вывода последовательных потоков информации и организации системы прерывания программ.

4) Счетчик команд предназначен для формирования текущего 16-разрядного адреса внутренней памяти программ и 8/16-разрядного адреса внешней памяти программ. В состав счетчика команд входят 16-разрядные буфер РС, регистр РС и схема инкремента.

5) Память данных (RAM) предназначена для временного хранения информации, используемой в процессе выполнения программы.

6) Память программ (EPROM) предназначена для хранения программ и представляет собой постоянное запоминающее устройство (ПЗУ). В разных микросхемах применяются масочные, стираемые ультрафиолетовым излучением или FLASH ПЗУ.

Микроконтроллеры семейства MCS-51 построены по Гарвардской архитектуре, т. е. память данных и память программ в этих микросхемах разделены и имеют отдельное адресное пространство. В этих микроконтроллерах имеется пять адресных пространств: память программ, внешняя память данных, три для внутренней памяти. Такое построение памяти позволяет удвоить доступное адресное пространство. Кроме того, такое построение памяти позволяет в ряде случаев увеличить быстродействие микросхем. Для обращения к памяти данных и к памяти программ используются одни и те же шина адреса и шина данных, но разные управляющие сигналы. Для чтения памяти программ вырабатывается сигнал PSEN, а для чтения памяти данных вырабатывается сигнал RD. Для записи информации в память данных вырабатывается сигнал WR. То есть память программ доступна только для чтения, а память данных доступна и для чтения и для записи любой информации, записанной в двоичном коде. Память программ имеет адресное пространство объемом 64 КБ, причем для некоторых микросхем (КР1816ВЕ51, КМ1819ВЕ751, КР1830ВЕ51) для хранения программ на кристалле микроконтроллера расположено ПЗУ. Это ПЗУ отображается в область младших адресов памяти программ. Так как выполнение программы после сброса микроконтроллера всегда начинается с нулевого адреса памяти программ, при включении питания начнет выполняться программа, записанная во внутреннем ПЗУ микроконтроллера. Микроконтроллеры, не имеющие внутреннего ПЗУ (КР1816ВЕ31 и КР1830ВЕ31) могут работать только с внешней микросхемой ПЗУ емкостью до 64 КБ (при использовании портов P1 и P3 в качестве расширителя адреса объем подключаемой ПЗУ может быть увеличен до 1 ГБ). Внешняя память данных предназначена для хранения информации, используемой в процессе выполнения программы. Эта память физически подключена к микроконтроллеру. Максимальный объем определяется регистром DPTR и составляет 64 КБ. Объем внешней памяти данных может быть увеличен за счет использования портов P1 и P3 до 1 ГБ. Внешняя память данных для своей работы требует использование портов P0, P2 и P3, что приводит к увеличению габаритов устройства, увеличению уровня помех и увеличению стоимости устройства в целом. Поэтому в современных устройствах внешняя память не используется. Однако, в некоторых микроконтроллерах (87с550 фирмы DALLAS) команды обращения к внешней памяти используются для работы с дополнительной внутренней памятью большого объема.

Внутреннее ОЗУ данных предназначено для временного хранения информации, используемой при выполнении программы, и занимает 128 (8031, 8051, модели 31, 51 и 751 серий КР1816ВЕ и КР1830ВЕ) или 256 (для всех остальных микроконтроллеров семейства) младших байт.

2020-01-15

2020-01-15 231

231