Из-за высоких требований, обусловленных специфическими областями применения сигнальных процессоров, их архитектура и рабочие характеристики отличаются от архитектуры других микропроцессоров и микроконтроллеров. Кроме высокой скорости выполнения команд, цифровой сигнальный процессор должен обладать следующими свойствами:

• Способность быстрого и гибкого выполнения арифметических операций - Базовая архитектура семейства ADSP-2100 обеспечивает вычисление за один цикл операций умножения, умножения с накоплением, произвольной величины сдвига и стандартных арифметико-логических операций. Кроме того, арифметические устройства позволяют осуществлять вычисления в любой последовательности, поэтому не требуется дополнительно модифицировать алгоритм цифровой обработки сигнала.

• Расширенный динамический диапазон - Большие суммарные результаты, типичные в цифровой обработке сигналов, аппаратно поддерживаются в умножителе-накопителе процессоров семейства ADSP-2100. Сумматор разрядностью в 40 бит обеспечивает восемь бит защиты от переполнения при последовательном сложении, и тем самым гарантирует, что не произойдет ни потери данных, ни их диапазона; чтобы произошла потеря старшего разряда, требуется 256 переполнении. Имеются специальные команды для выполнения масштабирования данных с блочной плавающей точкой.

• Возможность выбора двух операндов за один цикл - Для обеспечения вычислений с расширенными суммарными результатами требуется два операнда в каждом цикле. Все члены семейства ADSP-2100 способны поддерживать выполнение двух операндов данных, независимо от того, хранятся ли данные на или вне кристалла.

• Аппаратная поддержка циклических буферов - Для целого класса алгоритмов цифровой обработки сигналов, включая фильтры, требуется реализация циклических буферов. Базовая архитектура процессоров семейства ADSP-2100 включает аппаратное обеспечение циклического возврата указателя адреса, упрощая использование циклических буферов в памяти как на, так и вне кристалла и сокращая потери на их организацию (и, следовательно, увеличивая производительность).

• Организация циклов и условных переходов с нулевыми потерями времени -Алгоритмы цифровой обработки сигналов содержат повторы и в большинстве своем выражаются логически как циклы. Программный автомат в процессорах семейства ADSP-2100 поддерживает код цикла с нулевыми потерями, обеспечивая одновременно отличные рабочие характеристики и ясную структуру программы. Подобным же образом, без потерь ресурсов, организуются условные переходы.

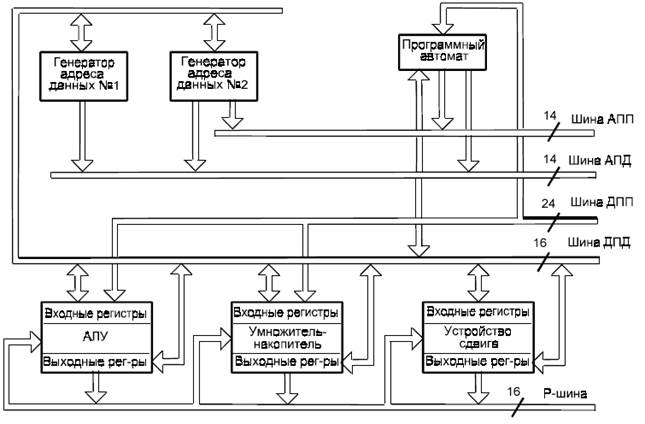

2.1 БАЗОВАЯ АРХИТЕКТУРА

Рис.2 базовая архитектура

Каждый процессор семейства ADSP-2100 содержит три независимых вычислительных устройства с полным набором функциональных возможностей:

арифметико-логическое устройство (АЛУ), умножитель-накопитель (умножитель) и устройство циклического сдвига. Вычислительные устройства обрабатывают данные разрядностью в 16 бит и поддерживают вычисления с повышенной точностью.

В АЛУ выполняются стандартные арифметические и логические операции и примитивы деления. В умножителе за один машинный цикл выполняются операции умножения, умножения/сложения и умножения/вычитания. Устройство сдвига выполняет операции арифметического и логического сдвига, нормализации, денормализации и нахождения порядка числа. Устройство сдвига осуществляет управление числовыми форматами, включая представления чисел, состоящих из нескольких слов, числами с плавающей точкой. Вычислительные устройства соединяются таким образом, что выход любого из этих устройств может быть входом в любое из этих устройств в следующем цикле. Для этого служит внутренняя шина результатов (Р шина) напрямую соединяющая вычислительные устройства.

Все три вычислительных устройства содержат регистры ввода и вывода, доступные по шине данных памяти данных (ДПД). Вычислительные устройства, как правило, берут операнды из регистров ввода и загружают результат в регистры вывода. Эти регистры являются буферами между памятью и вычислительными устройствами. Благодаря этому вводится один уровень конвейерной обработки при вводе и один уровень - при выводе. Р шина позволяет использовать результат одного вычисления напрямую в качестве входного значения для другого вычисления. Это позволяет избежать задержки конвейерной обработки при выполнении серии различных вычислений.

2020-01-14

2020-01-14 135

135