Новая цифровая иерархия была задумана как скоростная информационная автострада для транспортирования цифровых потоков с разными скоростями. В этой иерархии объединяются и разъединяются потоки со скоростями 155,520 Мбит/с и выше. Поскольку способ объединения потоков был выбран синхронный, то данная иерархия получила название синхронной цифровой иерархии (Synchronous Digital Hierarchy — SDH) [3,6].

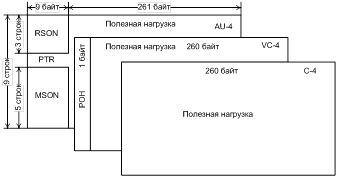

Для транспортирования цифрового потока со скоростью 155 Мбит/с создается синхронный транспортный модуль (Synchronous Transport Module) STM-1. Его упрощенная структура дана на рисунок 2.1.. Модуль представляет собой фрейм (рамку) 9•270 = 2430 байт. Кроме передаваемой информации (называемой в литературе полезной нагрузкой), он содержит в 4-й строке указатель (Pointer, PTR), определяющий начало записи полезной нагрузки.

Рисунок 2.2 – Структура модуля STM-1

Чтобы определить маршрут транспортного модуля, в левой части рамки записывается секционный заголовок (Section Over Head, SOH). Нижние 5•9 = 45 байтов (после указателя) отвечают за доставку информации в то место сети, к тому мультиплексору, где этот транспортный модуль будет переформировываться. Данная часть заголовка так и называется: секционный заголовок мультиплексора (MSOH). Верхние 3•9 = 27 байтов (до указателя) представляют собой секционный заголовок регенератора (RSOH), где будут осуществляться восстановление потока, "поврежденного" помехами, и исправление ошибок в нем.

Один цикл передачи включает в себя считывание в линию такой прямоугольной таблицы. Порядок передачи байтов — слева направо, сверху вниз (так же, как при чтении текста на странице). Продолжительность цикла передачи STM-1 составляет 125 мкс, т.е. он повторяется с частотой 8 кГц. Каждая клеточка соответствует скорости передачи 8 бит•8 кГц = 64 кбит/с. Значит, если тратить на передачу в линию каждой прямоугольной рамки 125 мкс, то за секунду в линию будет передано 9•270•64 Кбит/с = 155 520 Кбит/с, т.е. 155 Мбит/с.

Для создания более мощных цифровых потоков в SDH-системах формируется следующая скоростная иерархия: четыре модуля STM-1 объединяются путем побайтового мультиплексирования в модуль STM-4, передаваемый со скоростью 622,080 Мбит/с; затем четыре модуля STM-4 объединяются в модуль STM-16 со скоростью передачи 2488,320 Мбит/с; наконец четыре модуля STM-16 могут быть объединены в высокоскоростной модуль STM-64 (9953, 280 Мбит/с) [2].

2020-01-14

2020-01-14 134

134