Задание

Введение

Разработка функциональной схемы

Назначение основных элементов коммутатора и принцип их работы

Последовательно-параллельный и параллельно-последовательный преобразователи, стробирующие регистры

Дешифратор

Речевое и адресное запоминающие устройства

Счетчик

Мультиплексоры

Расчет блокировок коммутационного поля в режиме индивидуального искания

Заключение

Задание

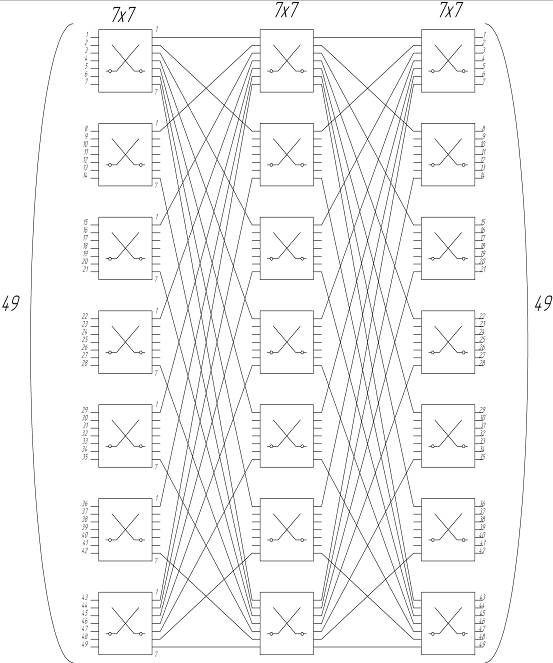

Разработать пространственно-временной коммутатор потоков DS1 (30 каналов) и рассчитать блокировки построенного на его основе коммутационного поля в режиме индивидуального искания.

Исходные данные: общее число входов коммутационного поля N=4;

число входов одного коммутатора n=2;

число коммутаторов в среднем звене m=4;

интенсивность нагрузки Y =0,8 Эрл.

Структура коммутационного поля, соответствующая исходным данным, представлена на рис. 1.1.

Рис. 1.1. Структура коммутационного поля.

Введение

Вторая половина ХХ века ознаменовалась переходом от так называемого индустриального способа общественного производства к информационному, в котором главенствующую роль начинает играть информация как основной критерий развития. Как следствие, повышаются требования к качеству систем коммутации и способам передачи, для повышения качества сигнала. Изобретение компьютеров тем более усилило процесс эволюции, так как резко возросшие объемы предаваемой информации, вводили проблему с ее обработкой, и введение дополнительного аналогового оборудования уже не могло решить эту проблему. Необходимо было создавать качественно новые системы связи.

Данную проблему удалось решить к началу 1980-х годов, когда началось чувствоваться влияние сетей ISDN, концепции Интеллектуальной сети, идеи Информационной магистрали. Одной из наиболее существенных технологий среди перечисленных выше являются цифровые АТС с программным управлением. Эпоху цифровой реализации телекоммуникационной сети предопределило наличие двух очень важных устройств: кодеков и модемов. Именно они, наряду с цифровизацией многоканальной электросвязи – систем передачи с ИКМ, обусловили появление цифровых систем коммутации.

Переход на цифровую передачу и коммутацию немедленно привел к резкому возрастанию числа обсуживаемых абонентов и улучшению качества речи, к уменьшению массогабаритных параметров, а как следствие экономия сырья на изготовление микросхем; значительно возросла надежность оборудования, ввиду использования автоматизированного процесса изготовления и настройки. Также были введены вспомогательные и дополнительные виды обслуживания абонентов (например, услуги Интеллектуальной сети).

Особенности цифровых коммутационных устройств с импульсно-кодовой модуляцией (ИКМ) сигналов: процессы на входах, выходах и внутри устройств согласованы по частоте и времени (синхронные устройства).

Разработка функциональной схемы

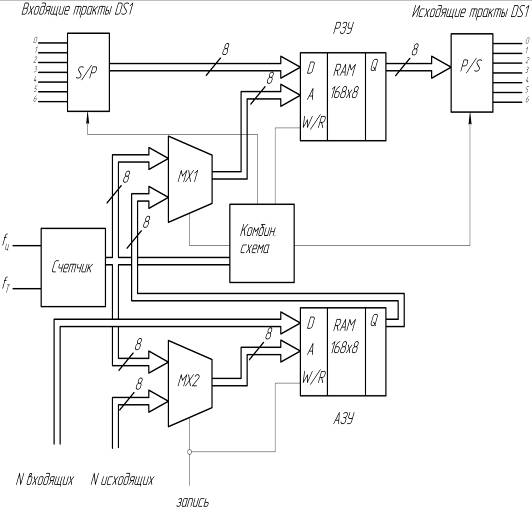

Структурная схема пространственно - временного коммутатора 7x7 представлена на рис. 3.1.

Рис. 3.1. Структурная схема пространственно - временного коммутатора 7x7:

S/P - последовательно-параллельный преобразователь;

P/S - параллельно-последовательный преобразователь;

РЗУ - речевое запоминающее устройство;

АЗУ - адресное запоминающее устройство;

СЧ - счетчик;

МX1 - мультиплексор адреса РЗУ;

МX2 - мультиплексор адреса АЗУ.

Данный коммутатор осуществляет пространственно-временную коммутацию входящих трактов ИКМ в исходящие.

Последовательно-параллельный преобразователь S/P осуществляет преобразование входящих ИКМ-трактов, представленных в последовательной форме, в параллельную.

РЗУ предназначено для записи и хранения в определенных ячейках, по адресам счетчика, кодовых комбинаций и считывания их в нужный момент времени.

АЗУ используется для записи и хранения информации о том, какой входящий и исходящий канал необходимо скоммутировать, и в последующем обеспечивает считывание в нужный момент времени номера входящего канала на адресные входы РЗУ при помощи счетчика.

Счетчик в свою очередь выдает адреса на РЗУ для записи по ним входящих каналов, а на АЗУ для считывания по ним номеров входящих каналов.

Дешифратор, получая адреса со счетчика, выдает логическую 1 на соответствующих выводах, что необходимо для разрешения параллельной загрузки информации на регистры S/P, и P/S при преобразовании кода в последовательную форму в исходящем тракте.

Мультиплексор MХ1 РЗУ осуществляет переключение сигналов со счетчика и сигналов, приходящих с АЗУ на выход, осуществляя тем самым запись и считывание по приходящим адресам.

Принцип работы мультиплексора МХ2 АЗУ аналогичен.

Параллельно-последовательный преобразователь P/S преобразует параллельную кодовую комбинацию с выхода РЗУ в последовательную форму для последующей коммутации с заданным исходящим каналом.

Пример коммутации 3-го входящего канала в 8-й исходящий представлен на временных диаграммах (Приложение В).

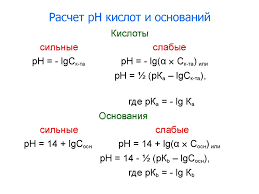

Установим основные требования к элементам функциональной схемы коммутатора:

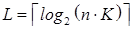

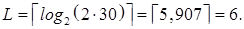

Разрядность шины счетчика  , где скобки

, где скобки  означают округленное до целого в большую сторону значение. Для коммутатора 7Ч7 входящих/исходящих трактов ИКМ-24 получим

означают округленное до целого в большую сторону значение. Для коммутатора 7Ч7 входящих/исходящих трактов ИКМ-24 получим

Так как при считывании с РЗУ под действием адресной информации, приходящей с выхода АЗУ (через мультиплексор адреса), содержимое каждой ячейки речевой памяти может быть извлечено в какой-либо канальный интервал исходящего тракта, то, очевидно, должны адресоваться все ячейки РЗУ. Поскольку таких ячеек в РЗУ  , то для их считывания необходима адресная шина шириной не менее

, то для их считывания необходима адресная шина шириной не менее  разрядов.

разрядов.

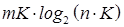

С другой стороны, при емкости коммутатора nЧm цифровых трактов, количество канальных интервалов на его выходе равно mK (содержание речевой памяти может считаться в mK временных интервалах, позиции которых определят моменты считывания адресных слов из АЗУ). Следовательно, емкость АЗУ должна быть равна  -разрядных ячеек. Для данного коммутатора

-разрядных ячеек. Для данного коммутатора  .

.

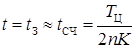

Очевидно, что для исключения потери информации содержимого входящих цифровых трактов, за время цикла (Тц) необходимо успеть осуществить запись nK восьмиразрядных слов в РЗУ и считать их оттуда. Т.е. на запись и считывание одного канального слова в РЗУ квадратного коммутатора должно отводиться время не более

,

,

что определяет требование по быстродействию речевого ОЗУ при заданном числе входных каналов или, наоборот, требования к количеству входящих канальных интервалов или цифровых трактов при заданном быстродействии ОЗУ

.

.

Все вышеперечисленные требования отражены на рис. 3.1.

2020-01-14

2020-01-14 202

202