ИЛИ-НЕ

И-НЕ

Если на выходе первого инвертора имеется логический 0, то он обеспечивает на выходе второго инвертора логическую 1, благодаря которой сам же и существует. Любое из двух состояний может существовать неограниченно долго. Чтобы управлять фиксатором, нужно иметь в логических элементах дополнительные входы.

На входы управления поступают внешние установочные сигналы:

R – установка в 0 или сброс (reset);

S – установка в 1 (set).

Состояние триггера считывается по значению прямого выхода Q, существует инверсный выход  .

.

Классификация триггеров производится по признакам логического функционирования и по способу записи информации:

Триггер типа RS имеет два входа, установки в 1 (S) и установки в 0 (R). Одновременная подача сигнала сброса и установки недопустима.

Триггер типа Д – триггер задержки, имеет 1 вход, его состояние повторяет входной сигнал, но с задержкой, определяемой либо тактовым сигналом, либо задержкой самого элемента.

Триггер типа Т инвертирует свое состояние каждый раз при поступлении входного сигнала, имеет 1 вход, называется триггером со счетным входом.

Триггер типа JK – универсальный вход установки J и вход сброса К (подобно RS). В отличие от RS-триггера допускается ситуация с одновременной подачей сигнала на вход J и вход К. Если J = К = 1, то он работает как счетный триггер относительно третьего тактового входа.

Триггер типа DV – наиболее используемый триггер. Это триггер типа Д, только информация будет записываться, если есть сигнал разрешения записи на входе V.

В комбинированных триггерах могут совмещаться несколько режимов. Это R, S, T-счетный триггер, имеющий входы установки и сброса.

Примером триггера со сложной логикой может служить JK-триггер с группами входа J1, J2, J3, К1, К2, К3. Между собой они связаны логическим соотношением:

J = J1*J2*J3; К = К1*К2*К3.

По способу записи различают асинхронные (нетактируемые) и синхронные (тактируемые) триггеры. В асинхронных триггерах переход в любое состояние вызывается непосредственным изменением входных информационных сигналов.

В синхронных триггерах есть специальный вход. Переход состояния происходит только при подаче на этот вход тактовых сигналов. Тактовые сигналы обозначаются С.

По способу восприятия тактов сигналов триггера делятся на управляемые уровнем и управляемые фронтом.

Управляемый уровнем означает, что при одном уровне тактового сигнала триггер воспринимает входные сигналы, а при другом уровне нет. При управлении фронтом разрешение на переключение дается только в момент перепада тактового сигнала. В остальное время независимо от уровня тактового сигнала триггер не воспринимает входные сигналы. Триггер, управляемый фронтом, называется триггером с динамическим управлением.

Динамический вход может быть прямым или инверсным. Прямой динамический вход означает, что разрешение на переключение появляется в момент изменения тактового сигнала с 0 значения на 1.

Инверсный динамический вход – переключение при изменении тактового сигнала с 1 на 0.

По характеру процесса переключения триггеры делятся на 1-ступенчатые и 2-ступенчатые (1-тактные и 2-тактные). В 1-ступенчатом триггере переключение в новое состояние происходит сразу, а в 2- ступенчатом поэтапно.

2-ступенчатые триггеры состоят из входной и выходной ступени. Переход в новое состояние происходит в обеих ступенях поочередно. Один из уровней тактового сигнала разрешает прием информации во входную ступень при неизменном состоянии выходной ступени. Другой уровень тактового сигнала разрешает передачу нового состояния из входной ступени в выходную.

Существует разное обозначение синхровхода в зависимости от управления:

1)

2)

3)

4)

5) ТТ – двухтактный триггер

Существует также триггер-защелка, который прозрачен при одном уровне тактового сигнала и переходит в режим хранения при другом уровне.

С синхронизацией триггера связаны два важных временных параметра:

время tsu – время предустановки;

время th – время задержки.

Эти времена свойственны не только триггерам, но и другим устройствам. Время предустановки tsu – это интервал до поступления синхроимпульса в течение которого сигнал должен оставаться неизменным.

th – время после поступления синхроимпульса необходимое для завершения переходного процесса.

Соблюдение th и tsu обеспечивает правильное восприятие триггером входной информации.

RS-триггеры

а) С использованием ИЛИ-НЕ.

Условно графическое обозначение элемента:

СР – схема реализации:

Q(t + 1) = S(t)  Q(t)

Q(t)  (t)

(t)

ТИ – таблица истинности: - запрещенное состояние.

| t | t+1 | |

| R | S | Q |

| Q(t) | ||

| — |

Это асинхронный триггер.

б) На элементах И-НЕ.

Условно графическое обозначение элемента:

Схема реализации:

Таблица истинности:

| t | t+1 | |

| R | S | Q |

| — | ||

| Q(t) |

в) Синхронные RS-триггеры.

Условно графическое обозначение элемента:

Схема реализации:

Таблица истинности: * - любое состояние.

| t | t+1 | ||

| С | R | S | Q |

| Q(t) | |||

| — | |||

| * | * | Q(t) | |

Временная диаграмма:

RS-триггер с синхровходом может работать не только по уровню 1, но и по уровню 0, для этого на синхровход подается инверсная синхросерия.

г) Двухтактный RS-триггер

Условно графическое обозначение элемента:

Схема реализации:

Д-триггер

Q(t+1) = Д(t)

а) Асинхронный Д-триггер.

Условно графическое обозначение элемента:

Схема реализации:

На информационные входы всегда будет приходить парафазный сигнал.

б) Синхронный Д-триггер.

Условно графическое обозначение элемента:

Схема реализации:

Д-триггер не может хранить информацию длительное время, только до момента прихода следующего синхроимпульса.

в) Двухтактный Д-триггер.

Условно графическое обозначение элемента:

Схема реализации:

Временная диаграмма:

Т-триггер

а) Асинхронный Т-триггер.

Особенность: Информация подается прямо на синхровход, который в этом случае называют счетный вход.

Т-триггер очень чувствителен к помехам.

Условно графическое изображение:

Схема реализации:

б) Синхронный Т-триггер.

Условно графическое изображение:

Схема реализации:

Т-триггер при поступлении 1 на вход, инвертирует значение выходного сигнала по преходу синхроимпульса.

JK-триггер

Наиболее универсальный из всех триггеров, на основе JK-триггера можно сделать практически все основные триггера. В качестве примера JK-триггера рассмотри двухтактный JK-триггер.

Условно графическое изображение:

Схема реализации:

Работает по приходу переднего фронта.

Таблица истинности:

| С | Y | K | Q |

| Q(t) | ||

| |||

| |||

| Q(t) | ||

| * | * | Q(t) | |

| * | * | Q(t) |

Типовые схемы на JK-триггерах

а) Д-триггер.

б) Т-триггер - синхронный

в) RS-триггер.

DV-триггер

Или триггер с динамическим управлением. Наиболее современный тип триггерных устройств. Основными достоинствами является то, что информация в триггере может сохраняться сколь угодно долго, независимо от поступления информации. Триггер срабатывает по переднему фронту и разрешение на запись происходит на специальный V вход.

Условно графическое изображение:

Схема реализации:

Таблица истинности:

| t | t+1 | ||

| C | D | V | Q |

| * | Q(t) | ||

| * | Q(t) | ||

| |||

| |||

| * | Q(t) | |

Примеры реализации логических функций с помощью триггеров разного типа

1) с = a  b

b

2) a:= b, если с

RSтриггер

R:

S: bc (одновременное присутствие)

Д-триггер

a:= b, если с

Д =

DV-триггер

D: b

V: c

Задача: a:= (bc  d), если (f

d), если (f  k).

k).

RS -? Д -? DV -?

Регистры

Регистры – это самые распространенные узлы цифровых устройств, они оперируют со множеством переменных, составляющий слово.

Над словами выполняется ряд операций:

- прием;

- выдача;

- хранение;

- сдвиг в разрядной сетке;

- поразрядные логические операции.

Обычно регистры состоят из набора триггеров и логических элементов. Регистры делятся:

а) по количеству линий передачи переменных:

- однофазные;

- парафазные;

б) по системе синхронизации:

- однотактные;

- двухтактные;

- многотактные;

в) по способу приема и выдачи данных:

- параллельные (статические);

- последовательные (сдвигающие);

- параллельно-последовательные.

В параллельных регистрах прием и выдача слов производятся по всем разрядам одновременно, в таких регистрах хранятся слова, которые могут быть подвергнуты поразрядным логическим преобразованиям.

В последовательных регистрах слова применяются и выдаются разряд за разрядом. Эти регистры называются сдвигающими, так как синхроимпульс при вводе и выводе слов перемещает их в разрядной сетке.

Сдвигающий регистр может быть:

- нереверсивным (со сдвигом в одном направлении);

- реверсивным (с возможностью сдвига в обоих направлениях).

Последовательно-параллельные регистры имеют входы и выходы одновременно последовательного и параллельного типа.

В параллельных регистрах схемы разрядов не обмениваются между собой данными.

Общими для разрядов являются цепи управления:

- синхросерии;

- сброс-установка;

- разрешение выдачи и приема.

Для современной схемотехники характерно построение регистров на DV-триггерах.

Параллельный регистр:

х0, хn – разряды слова;

L – обобщенный канал;

С – синхросерия, синхровходы обязательно объединяются в регистре, но на схеме это может быть не указано.

Последовательный регистр:

Если брать поразрядную информацию с выводов, обозначенных пунктирами, то получим последовательно-параллельный регистр.

У последовательного регистра информация загружается за определенное число тактов равное количеству триггеров.

«–»: более медленное устройство;

«+»: гораздо меньше выводов.

8.Регистры. Назначение и классификация. Примеры исполнения параллельных и последовательных регистров на триггерах D, J-K и R-S типов. Реверсивный сдвиговый регистр. Пример построения 4-х разрядного регистра на триггерах D-типа. Привести пример функциональной и принципиальной схем, временные диаграммы и краткое описание работы. Параллельный регистр на триггерах R-S и D-типа. Примеры принципиальных схем, временные диаграммы и краткое описание работы схем. Параллельный регистр на триггерах JK-типа. Пример принципиальной схемы, временные диаграммы и краткое описание работы регистра. Параллельно-последовательные регистры. Примеры построения на триггерах R-S-D и R-S-J-K. Привести принципиальные схемы 3-разрядных регистров. Универсальный реверсивный регистр (с возможностью параллельной записи и сдвига информации вправо и влево). Привести пример функциональной и принципиальной схем 3-разрядного регистра на триггерах R-S-J-K типа. Регистры с обратными связями. Привести пример схемы последовательного регистра с обратной связью, описание его работы и временные диаграммы сигналов в различных точках схемы.

Назначение регистров – хранение и преобразование многоразрядных двоичных чисел.Регистры наряду со счетчиками и запоминающими устройствами являются наиболее распространенными последовательными устройствами цифровой техники. При простоте схемы регистры обладают большими функциональными возможностями. Они используются в качестве управляющих и запоминающих устройств, генераторов и преобразователей кодов, счетчиков,

делителей частоты, узлов временной задержки. Элементами структуры регистров являются синхронные триггеры D-типа либо RS- (JK) типа с динамическим или статическим управлением. Одиночный триггер может запоминать (регистрировать) один разряд (бит) двоичной информации. Такой триггер можно считать одноразрядным регистром. Цифровая техника, как правило, оперирует с многоразрядными числами. Поэтому в качестве регистров в зависимости от назначения используются наборы либо цепочки

триггеров – по количеству разрядов числа. В схемы регистров входят также комбинационные элементы, роль которых в данном случае вспомогательная.

Занесение информации в регистр называют операцией ввода или записи. Выдача информации к внешним устройствам характеризует операцию вывода или считывания. Запись информации в регистр не требует его предварительного обнуления. Понятие "весовой коэффициент" к разрядам регистра в отличие от счетчика неприменимо, поскольку весовая зависимость между отдельными разрядами целиком определяется записанной в регистр информацией. По этой причине на условных изображениях регистров нумера-

ция меток информационных входов и выходов идет подряд.Все регистры в зависимости от функциональных свойств подразделяются на две катего-

рии: накопительные (регистры памяти, хранения) и сдвигающие. В свою очередь, сдвигающие регистры делятся:

· по способу ввода и вывода информации – на параллельные, последовательные и ком-

бинированные (параллельно-последовательные и последовательно-параллельные);

· по направлению передачи (сдвига) информации – на однонаправленные и реверсив-

ные.

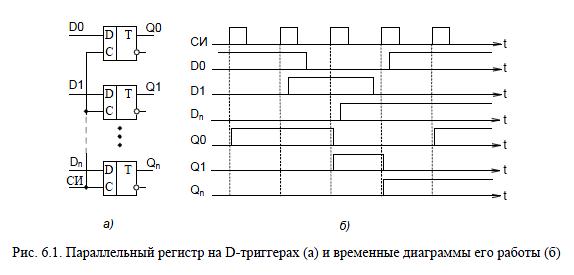

Параллельные регистры (регистры памяти) – простейший вид регистров. Их назначение хранить двоичную информацию небольшого объема в течение короткого промежутка времени. Эти регистры представляют собой набор синхронных триггеров, каждый из которых хранит один разряд двоичного числа. Ввод (запись) и вывод (считывание) информации производится

одновременно во всех разрядах параллельным кодом. Ввод обеспечивается тактовым командным импульсом. С приходом очередного тактового импульса происходит обновление записанной информации. Сигналы на выходах триггеров характеризуют выходную информацию. Считывание может производиться в прямом или в обратном коде (в последнем случае с инверсных выходов).

Регистры хранения представляют собой, по существу, наборы триггеров с независимыми информационными входами и обычно общим тактовым входом. В качестве регистров подобного рода могут быть использованы без дополнительных элементов многие типы синхронних триггеров. Особенно удобно использовать микросхемы, содержащие в одном корпусе несколько самостоятельных триггеров. На рис. 6.1,а приведен пример построения параллельного регистра на D-триггерах, а на рис. 6.1,б – временные диаграммы сигналов, поясняющие его работу. Каждый из триггеров записывает информацию, подаваемую на вход D, и сохраняет ее до прихода следующего синхроимпульса.

Типичный пример применения регистра памяти – это промежуточное запоминание показаний счетчика на время отсчета. Используя триггеры со статическим управлением, следует учитывать, что все особенности этого вида управления, о которых говорилось выше, распространяются и на регистры на их основе. Наращивание разрядности регистров памяти достигается добавлением нужного числа триггеров, тактовые входы которых присоединяют к шине синхронизации.

Основную массу регистров, используемых на практике, представляют регистры сдвига или последовательные регистры. Этот вид регистров отличается большим разнообразием, как в функциональном отношении, так и в отношении схемных решений, временных параметров, емкости и т.п.

Регистры сдвига, помимо операции хранения, осуществляют преобразование последовательного двоичного кода в параллельный, а параллельного – в последовательный, выполняют арифметические и логические операции, служат в качестве цифровых элементов временной задержки.

В зависимости от количества каналов, по которым поступает информация на входы разрядов сдвигового регистра, различают регистры парафазные (информация на каждый разряд поступает по двум каналам – прямому и инверсному) и однофазные (информация поступает по одному каналу).

При проектировании сдвиговых регистров необходимо обязательно применять триггеры, синхронизируемые фронтом, так как во время действия синхросигнала изменяются состояния выходов триггеров, которые подключены к входам последующих триггеров. Таким образом, изменяется состояние входов последующих триггеров, и если синхроимпульс еще не кончился, то

триггеры, синхронизируемые уровнем, переключаются в новое состояние, т.е. за время действия одного синхросигнала (один такт) информация в регистре продвигается более чем на один разряд и нормальное функционирование регистра (сдвиг на один разряд за один такт) нарушается.

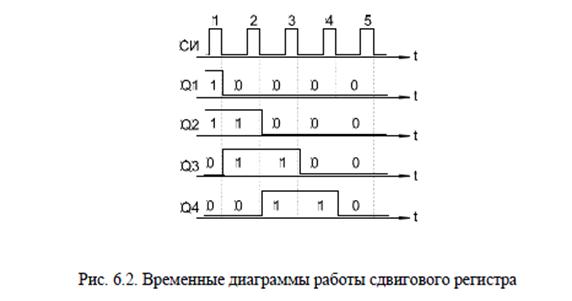

Своим названием они обязаны характерной для этих устройств операции сдвига. Сущность сдвига состоит в том, что с приходом каждого тактового импульса происходит перезапись (сдвиг) содержимого триггера каждого разряда в соседний разряд без изменения порядка следования, единиц и нулей. При сдвиге информации вправо после каждого тактового импульса

бит из старшего разряда сдвигается в младший, а при сдвиге влево – наоборот.

На схемах символом регистра служат буквы RG. Для регистров сдвига указывается так-

же направление сдвига: ® – вправо; – влево; ® – реверсивный (двунаправленный).

На рис. 6.1 приведена схема четырехразрядного регистра с последовательным вводом входной информации и сдвигом ее вправо. В схеме используются RSJK-триггеры с инверсными входами R и S, которые по этим входам управляются "0". Наличие "1" на этих входах разрешает работу JK-триггера. При наличии "0" на входах S триггеры устанавливаются в "1", а при наличии "0" на входах R триггеры устанавливаются в "0". Подача "0" на входы R и S одновременно запрещена. На схеме входы S триггеров никуда не подключены. Такой режим работы допустим только триггеров выполненных по технологии ТТЛ. В элементах ТТЛ отключение входа ИМС эквивалентно подаче на его вход уровня логической "1". В схеме на рис. 6.1 JK-триггеры используются в режиме D-триггера. Для этого входной сигнал подается на вход J первого триггера DD1 напрямую, а на вход K – через инвертор. В

остальных триггерах такой режим работы обеспечивается соединением входов J с прямыми выходами триггеров, а входов K – с инверсными выходами.

Допустим, что в регистр последовательно вводится со входа DI, начиная с младшего разряда, двоичный код 1101, который поступает от внешнего устройства синхронно с тактовими импульсами. С первым тактовым импульсом в триггер DD1 будет записана единица младшего разряда. Со следующим тактовым импульсом эта единица будет сдвинута в триггер DD2 и окажется на его выходе. Одновременно в первый триггер поступит нуль (следующий разряд кода). Таким же образом будут происходить сдвиги с выхода Q2 на вход DD3 и с Q3 в DD4. После четырех тактовых импульсов код на выходах триггеров Q4…Q1 будет соответствовать входному коду (рис. 6.2) и может быть считан внешним устройством. Таким образом, регистр преобразует последовательный код в параллельный. После очередного тактового импульса (в данном слу-

чае – пятого) информационный сигнал, бывший на выходе последнего триггера, выводится из регистра и пропадает.

На выходе Q4 каждый сигнал появляется через четыре такта, считая с момента подачи его на вход. Это свойство регистра сдвига часто используется для задержки цифровой информации на заданное число тактовых периодов.

Разрядность регистра сдвига, подобного показанному, может быть увеличена подключением дополнительных триггеров.

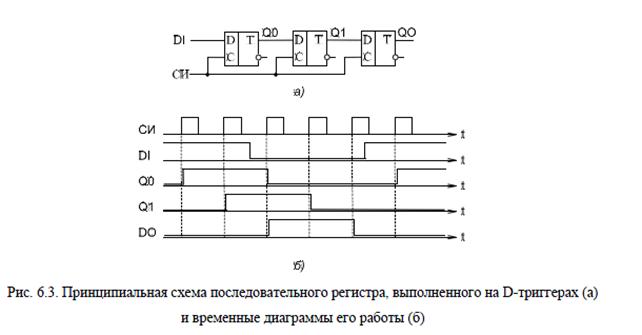

На рис. 6.3,а приведена схема последовательного регистра, выполненного на D-

триггерах, а на рис. 6.3,б – временные диаграммы сигналов, поясняющие его работу. На рисунке введены следующие обозначения: DI (Data Input) – вход данных, DO (Data Output) – выход данных.

Исследование работы однофазного параллельного регистра

Параллельные регистры или регистры памяти применяются для ввода, хранения и вывода двоичной информации в параллельном коде. Они могут быть образованы из асинхронных и синхронных, одноступенчатых и двухступенчатых триггерах.

Однофазный параллельный регистр (рисунок 2) построен на одноступенчатых асинхронных RS-триггерах. Так как на кодовые шины слова (КШС) параллельного регистра подается двоичное слово Х0 Х1 Х2 Х3 в прямом коде (однофазный код), то КШС с помощью элементов И-НЕ подключены к инверсным асинхронным входам S установки в 1 триггеров регистра. Прием двоичного словаХ0 Х1 Х2 Х3 в регистр осуществляется в два такта. По первому такту сигналом CLR на асинхронном входе R, регистр устанавливается в состояние "0000". По второму такту сигналом прием

слова (WR) в регистр записывается параллельный код двоичного слова Х0 Х1 Х2 Х3.

Рисунок 2 - Однофазный параллельный регистр на RS - триггерах

Записанный в регистр код двоичного слова может храниться до тех пор, пока регистр не будет установлен сигналом CLR (уст. «0») в состояние "0000".

Сигнал WR (прием информации - синхросигнал) обычно импульсный, так как кратковременное подключение регистра к КШС уменьшает вероятность занесения в регистр ошибочной информации.

Таким образом, при записи двоичного слова в регистр в худшем случае каждый его триггер будет переключаться дважды: один раз при установке регистра в нулевое состояние сигналом CLR и второй раз при приеме 1 в данный триггер по сигналу WR.

Быстродействие регистра – время записи в регистр Тргзап двоичной информации определяется минимально допустимым временем между поступлениями очередных кодов на входах регистра: Трг. зап = 2tT+ tИ, где tT – время задержки сигнала триггером; tИ – время задержки сигнала на элементе И.

Прямой и обратный код двоичного слова снимается соответственно с выходов соответствующих триггеров.

Рис. 1 Однофазный параллельный регистр

2020-05-21

2020-05-21 674

674