Application-specific integrated circuit (ASIC)

ASIC – интегральная схема, специализированная для решения конкретной задачи. В отличие от обычных интегральных схем стандартной логики, специализированные интегральные схемы применяются в конкретном устройстве и выполняют строго ограниченные функции, характерные только для данного устройства. По сути ASIC интегрирует внутри себя на одном полупроводниковом кристалле схему, которая может быть реализована путем соединения микросхем стандартной логики. Вследствие этого выполнение функций происходит быстрее, устройство становится компактнее и, в конечном счёте, дешевле. Примером ASIC может являться микросхема, разработанная исключительно для управления мобильным телефоном, микросхемы аппаратного кодирования/декодирования аудио- и видеосигналов (сигнальные процессоры). Современные ASIC часто содержат 32-битный или даже 64-битный процессор, иногда в количестве нескольких ядер, блоки памяти (как ПЗУ, так и ОЗУ) и другие крупные блоки. Такие ASIC часто называют однокристальной системой или системой на кристалле System-on-Chip (SoC). При разработке цифровых ASIC для описания их функциональности используют языки описания аппаратных устройств (HDL), такие как Verilog и VHDL.

Основными типами ПЛИС, которые используются в современной электронике являются CPLD и FPGA.

В отличие от обычных цифровых микросхем, рассмотренных ранее (стандартная логика и ASIC), логика работы ПЛИС не определяется при изготовлении, а задаётся посредством программирования. Для программирования используются программатор и IDE (среда разработки), позволяющие задать желаемую структуру цифрового устройства в виде принципиальной электрической схемы или описания на специальных языках описания аппаратуры – Hardware Description Language (HDL). HDL – не язык программирования, хотя внешние сходства имеются. HDL – это язык, который описывает схему цифрового устройства в текстовом виде.

Complex programmable logic device (CPLD)

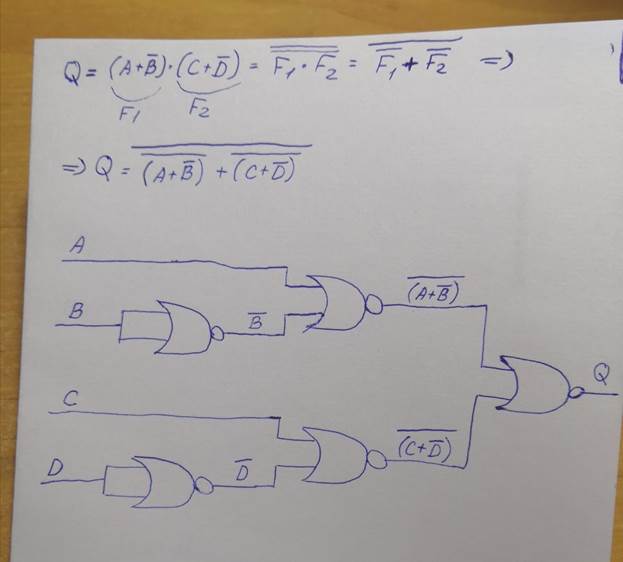

Программируемая логическая интегральная схема CPLD (еще ее называют в русскоязычной литературе программируемая логическая матрица или ПЛМ) состоит из нескольких макроячеек, расположенных на одном кристалле (см. Рисунок 1). Каждая макроячейка соединена с блоками ввода-вывода, осуществляющими формирование необходимого вида входов или выходов для работы с внешними схемами. Кроме того, все макроячейки и блоки ввода-вывода связаны между собой внутренними параллельными шинами. Приведенная на рисунке 3 микросхема CPLD состоит из четырех макроячеек, которые связаны между собой внутренними шинами и соединяются с блоками ввода-вывода. Макроячейка представляет универсальную схему (см Рисунок 2), с помощью которой можно реализовать любую логическую схему путем создания соединений или разрывов цепи на месте условных перемычек. Этот процесс называют конфигурированием или программированием CPLD. В качестве этих условных перемычек могут быть собственно плавкие перемычки или ячейки EEPROM или FLASH. Входы D1 и D2 проходят через инверторы, которые создают прямую и инверсную сигнал-«копию» этих входов внутри макроячейки, которые могут быть соединены (если перемычка соединена) или разорваны (перемычка оборвана) с многовходовыми вентилями «И», которые идут на вход вентилей «ИЛИ». На выход Q с помощью мультиплексора можно подать либо выход вентиля «ИЛИ» непосредственно, либо через D-триггер. С помощью данной схемы макроячейки, можно реализовать любую комбинаторную функцию от двух входов (как мы говорили ранее, любую цифровую комбинаторную схему можно реализовать, имея базисный набор вентилей И-ИЛИ-НЕ). А с помощью нескольких макроячеек в CPLD, можно реализовать комбинаторную функцию и на большее число входов. Входящий в макроячейку триггер позволяет создавать регистровые схемы. Например, если замкнуть перемычки F2, F4, F7, а остальные разомкнуть, то 𝑄1 = 𝐷1 ∙ 𝐷2 + 𝐷2. При этом, если SEL = 1, то Q = Q1, а если SEL = 0, то Q – это выход триггера, вход которого Q1. К недостаткам мож но отнести то, что трудно обеспечить эффективное применение всех макроячеек. Всегда часть макроячеек остается неиспользуемыми. Часто из макроячейки используется только триггер или логический элемент "И" (“ИЛИ"). Остальная часть схемы зря занимает площадь кристалла и потребляет ток от источника питания. (Рисунки на 8 странице лекций)

2)

2020-06-29

2020-06-29 184

184