Лекция № 18

Важнейшим видом знакового моделирования является математическое моделирование, при котором исследование объекта осуществляется посредством модели, сформулированной на языке математики с использованием тех или иных математических методов.

Такое моделирование носит теоретический характер.

Идеальное моделирование основано на аналогии идеальной, т.е. мысленной.

Основными разновидностями материального моделирования являются физическое и аналоговое моделирование.

Физическим принято называть моделирование, при котором реальному объекту противопоставляется его увеличенная или уменьшенная копия, допускающая исследование с помощью перенесения свойств изучаемых процессов и явлений с моделей на объект на основе теории подбора.

Аналоговое моделирование основано на аналогии процессов и явлений, имеющих различную физическую природу, но одинаково описываемых формально (одними и теми же математическими уравнениями, логическими схемами и т.п.)

Отметим, что оба типа материального моделирования по своей природе являются эксизэиментальными методами.

Различают два типа идеального моделирования: интуитивное и знаковое.

Под интуитивным методом понимают моделирование, основанное на интуитивном представлении об объекте исследования, не поддающимся формализации или не нуждающимся в нем.

Например: Наш с вами (у каждого свой) жизненный опыт считаться интуитивной моделью окружающего мира.

Знаковым называется моделирование, использующее в качестве моделей знаковые преобразования какого-либо вида: схемы, графики, чертежи, формулы, набор символов и т.д.

Транзисторно-транзисторная логика (ТТЛ) удачно совмещает хорошее быстродействие, помехоустойчивость, нагрузочную способность с умеренным потреблением энергии и невысокой стоимостью.

Особенность ТТЛ логики состоит к том, что в ней используется многоэмиттерный п-р-п транзистор, который имеет от 2 до 8 эмиттepoв и общие области базы и эмиттера.

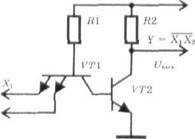

Схема простейшего элемента ТТЛ

Электрическая схема простейшего (малосигнального) ЛЭ ТТЛ состоит из входного двухэмиттерного транзистора VT1, в цепь базы которого включен резистор R1, и выходного инвертора на транзисторе VТ2, и резисторе R2. Многоэмиттерный транзистор выполняет логическую операцию И. Простейшие элементы ТТЛ широко пользуются и БИС и как составная часть более сложных логических схем.

Пусть на одни вход ЛЭ подается напряжение логического нуля U uxl = U°, а на второй вход - высокое напряжение U к2 = U1. Первый переход эмиттер-база транзистора VT1 будет смещен в прямом направлении. Второй змиттерпый переход, нa который подается напряжение высокого уровня Uцх2 > U1, смещен в обратном на правлении, ток его близок к пулю. Потенциал базы транзистора VT1 составляет

U = U + U*,

Где U = 0,8 В - прямое падение напряжения на эмиттерном.переходе при Т- 300 К. Напряжение Ufl приложено в прямом направлении к последовательно включенным переходам база- коллектор транзистора VТl и база- эмиттер транзистора VТ2 Однако этого потенциала недостаточно для отпирания этих переходов (Uб< 2U*), поэтому Ik1=Iб2=О. Транзистор VT2 закрыт Ток протекает от источника питании через резистор Rl, переxoд база -эмиттер транзистора VТl и источник напряжения U °. Он является входным током ЛЭ. Транзистор VТ2 закрыт, а через резистор R2 протекает небольшой ток нагрузки, поэтому на выходе ЛЭ устанавливается напряжение высокого уровня - U'. Подобное же состояний устанавливается и схеме ЛЭ, если на нее входы подается напряжение низкого уровня U°.

При подаче на все входы ЛЭ напряжения высокого уровня эмиттерные переходы транзистора VТl смещены в обратном направлении. Транзистор VТ1-находится к инверсном режиме.

Основной ток протекает от источника питания через резистор R1, переходы база - коллектор транзистора VTIи база -эмиттер транзистора VT2. Транзистор VT2открыт и находится в режиме насыщения.

Таблица истинности двухвходового ЛЭ ТТЛ имеет вид, соответствующий логической функции 2И НЕ. Описанный ЛЭ может работать при напряжении источника питания U = 3...5 В и имеет логические уровни U0 < 0,5 В, U '> 2 В. Нагрузочная способность простейшего ЛЭ ТТЛ ограничена, хотя при малых значениях емкости нагрузки (в структурах СИС, БИС) задержка распространения может составлять единицы наносекунд.

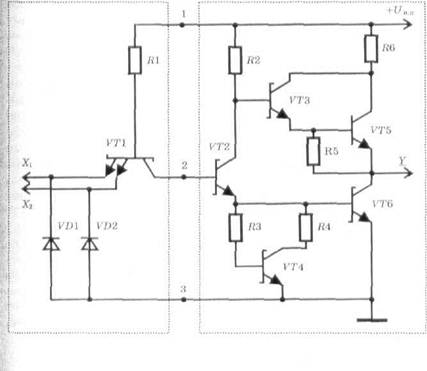

Базовые логические элементы, которые используются в качестве отдельных микросхем или как выходные каскады БИС, для повышения помехоустойчивости, нагрузочной способности и обеспечения высокого быстродействия имеют более сложную электрическую схему, которая представлена на рисунке 1.

Рисунок 1 Схема элемента ТТЛ со сложным инвертором.

Схема содержит на входе многоэмиттерный транзистор Т1, который выполняет логическую функцию И, фазоразделяющий каскад на транзисторе VT2 и резисторах R 2, RЗ, Входной каскад на транзисторах VT3 и VT4, диоде VD3, резисторе R 4.

При подаче на вход сигнала низкого уровня UBK = U° транзистор VT2 будет закрыт. Ток эмиттера транзистора VT2, который делится между резистором R3 и базой транзистора VT4, равняется нулю, поэтому транзистор VT4 будет закрыт. Уровень напряжения на коллекторе VT2 (Uk2= Vи.п.) достаточный для отпирания транзистора VT3. В цепи базы VT3 протекает ток от источник питания через резистор R 2. Транзистор VT3 открыт.

На выходе ЛЭ напряжение

При подаче на все входы ЛЭ напряжения высокого уровня многоэмиттерный транзистор VT1 будет находиться в инверсном активном режиме, в базу VT2 потечет ток, VT2 отопрется, потенциал коллектора VT2 уменьшается и транзистор VT3 закроется. Часть эмиттерного тока VT2 поступает в базу транзистора VT4, этот транзистор отпирается и входит в режим насыщения. Выходное напряжение имеет низкий уровень.

Потенциал базы транзистора VT l определяется суммой падения напряжения натрех открытых переходах: коллекторном VT l, эмиттерном VT2, эмиттерном VT З. Поэтому для отпирания VT2 это напряжение должно быть UB] > 3U = 2,4 В. Процесс переключения транзисторов VT3 и VT4 начинается одновременно, поэтому некоторое время оба транзистора открыты и через них протекает импульс сквозного тока, величину которого ограничивает резистор R4 (50...150 Ом). Этот же резистор защищает схему от случайного короткого замыкания выхода ЛЭ на общую шину. Резко уменьшение напряжения U вых в сочетании с импульсом сквозного тока возбуждает цикл затухающих колебаний в паразитных индуктивностях и емкостях схемы и соединительных проводников Эти импульсы могут вызывать ложное срабатывание подключенных к выходу логических элементов. Для предотвращения этого, ко входам ЛЭ ТТЛ подключены демпфирующие «антизвонные»диоды VD1 и VD2. В нормальном состоянии диоды VD1 и VD2 закрыты, но с появлением отрицательного полупериода затухающих колебаний открываются и ограничивают эти импульсы на уровне – U*, тем самым предотвращают дальнейшие колебания.

Логические уровни ЛЭ ТТЛ-типа: U1 = 2,4 В; U0 = 0,4В; максимально допустимая емкость нагрузки Сн = 200 пФ.

ТТЛ с структурами Шоттки (ТТЛШ).

Как отмечалось ранее, значительную часть длительности переходного процесса при запирании биполярного транзистора составляет процесс рассасывания заряда неосновных носителей. Для предотвращения этого между базой и коллектором биполярного транзистора включается диод

Шоттки (переход металл – полупроводник). В процессе отпирания транзистора потенциал коллектора снижается и становится отрицательным относительно потенциала базы. Когда разность потенциалов базы и коллектора достигнет Uдш ( где Uдш- прямое падение напряжения на диоде Шоттки). Отпирается диод Шоттки и напряжение между базой и коллектором фиксируется на уровне Uдш.. Величина Uдш. равняется 0,3…0,45В. Поэтому коллекторный переход остается практически запертым. Если коллекторный переход при отпирании транзистора не переходит в открытое состояние, накопление инжектированных неосновных носителей в области коллектора не происходит и продолжительность процесса рассасывания сокращается. Электрическая схема логического элемента транзисторно-транзисторной логики Шоттки (ТТЛШ) представлена на рисунке 2.

Рисунок 2. Схема базового элемента ТТЛШ.

Все транзисторы этой схемы, кроме транзистора VT5, имеют структуру с переходом Шоттки. Транзистор VT5 имеет обычную структуру,так как он не переходит в режим насыщения.

Благодаря резкому сокращению времени рассасывания заряда неосновных носителей, быстродействие ЛЭ ТТЛШ в несколько раз выше, чем в ЛЭ ТТЛ.

Для улучшения параметров в современных ЛЭ ТТЛШ вместо МЭТ для реализации логической функции применяют входные каскады.

2014-02-02

2014-02-02 2321

2321