Триггеры

Для хранения информации в компьютере могут использоваться различные типы элементов памяти. В зависимости от способа хранения информации элементы памяти могут быть статическими, позволяющими хранить двоичную информацию сколь угодно долго, и динамическими, хранящими информацию в течение ограниченного отрезка времени. В качестве статических элементов памяти в настоящее время применяют триггеры.

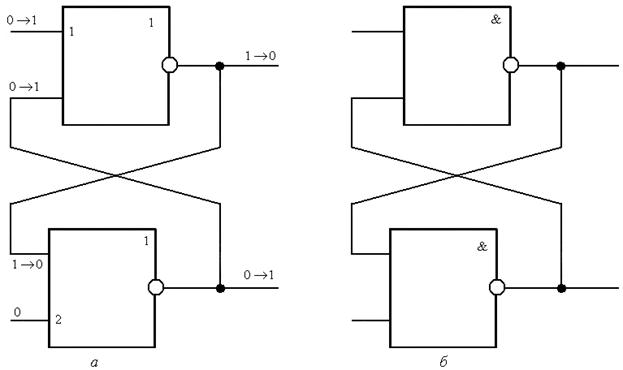

Основу триггера составляет бистабильная ячейка, имеющая два устойчивых состояния. Бистабильные ячейки могут быть построены на двух логических элементах И-НЕ или ИЛИ-НЕ, соединенных перекрестными связями (рис. 2.12).

Существование двух устойчивых состояний бистабильной ячейки объясняется наличием в ее схеме обратных связей, позволяющих сигналу с выхода элемента поступать на его же вход через второй элемент. Так, если на рис. 2.12, а сигнал на верхнем выходе равен «1» и на оба входа подается сигнал «0», то сигнал «1» с выхода элемента 1 поступает на вход элемента 2 и формирует на его выходе сигнал «0». Этот сигнал поступает на вход элемента 1 и поддерживает такое состояние схемы, делая его устойчивым. В этом состоянии на выходе элемента 1 сигнал равен «1», а на выходе элемента 2 сигнал равен «0».

Рис. 2.12. Бистабильная ячейка:

а – на элементах ИЛИ-НЕ; б – на элементах И-НЕ

Для изменения состояния схемы необходимо подать на верхний вход элемента 1 сигнал «1». При этом на выходе элемента 1 сигнал становится равным «0». Тогда на выходе элемента 2 формируется сигнал «1», который вместе с единичным входным сигналом устанавливает выходной сигнал элемента 1 равным «0». Такое состояние схемы также является устойчивым и после того, как сигнал на входе элемента 1 станет равным «0». В этом состоянии на выходе элемента 1 сигнал равен «0», а на выходе элемента 2 – «1». При поступлении сигнала «1» на вход элемента 2 происходит возвращение схемы в начальное состояние. Таким образом, схема имеет два устойчивых состояния, которые можно устанавливать подачей сигнала «1» на вход элемента 1 или 2. Аналогично работает бистабильная ячейка на элементах И-НЕ (см. рис. 2.12, б).

Триггер – это цифровая электронная схема с двумя устойчивыми состояниями, которые устанавливаются при подаче соответствующей комбинации входных сигналов и сохраняются.

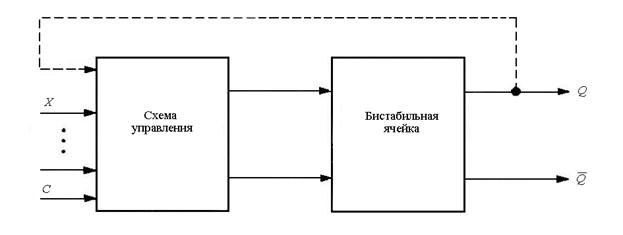

Кроме бистабильной ячейки в состав триггера входит схема Управления (рис. 2.13). Схема управления – это комбинационная схема, при помощи которой осуществляется запись информации в триггер (изменение состояний триггера). Конкретный вид схемы Управления зависит от типа триггера.

Рис. 2.13. Общая структура триггера

Триггер имеет два выхода: прямой и инверсный (Q и  ). Сигналы на выходах триггера всегда имеют различные значения. Если на прямом выходе сигнал равен «1», то на инверсном – «0» и наоборот. Состояние триггера определяется значением сигнала на прямом выходе (Q). Если сигнал на прямом выходе равен «1», то триггер находится в состоянии «1». Можно также сказать, что состояние триггера – это информация, записанная в триггере. Таким образом, если триггер находится в состоянии «1», то в нем записана единица.

). Сигналы на выходах триггера всегда имеют различные значения. Если на прямом выходе сигнал равен «1», то на инверсном – «0» и наоборот. Состояние триггера определяется значением сигнала на прямом выходе (Q). Если сигнал на прямом выходе равен «1», то триггер находится в состоянии «1». Можно также сказать, что состояние триггера – это информация, записанная в триггере. Таким образом, если триггер находится в состоянии «1», то в нем записана единица.

Триггеры могут быть асинхронными или синхронными. В асинхронных триггерах используются только основные или информационные входы. Изменение состояния асинхронного триггера может происходить в произвольные моменты времени, определяемые изменениями сигналов на информационных входах.

В синхронных триггерах кроме информационных входов имеется вход синхронизации. На этот вход подается сигнал синхронизации С, который выполняет функции сигнала, разрешающего переключение триггера из одного состояния в другое. Если сигнал синхронизации С равен «0», то состояние синхронного триггера не изменяется при любой комбинации сигналов на информационных входах. Для переключения синхронного триггера необходимо подать на информационные входы определенную, зависящую от типа триггера, комбинацию сигналов и, кроме того, установить значение сигнала С, равное «1».

Логика переключения триггера определяется его типом и зависит от числа и назначения входов. Наиболее часто в цифровой технике используют RS -, JK -, D - и T -триггеры, а также комбинированные триггеры. Буквами R, S, J, К, D и Т обозначаются информационные входы триггеров (X).

2.12.2. Асинхронный RS -триггер

Он имеет два информационных входа R и S. Вход S (set) используется для установки триггера в состояние «1», а вход R (reset) – в состояние «1», поэтому RS- триггер называют триггером с установочными входами.

Работу триггера описывает таблица переходов (табл. 2.4).

Таблица 2.4. Переходы RS -триггера

| Входы | Состояния | ||

| R | S | ||

| – | – |

Входами служат значения входных сигналов R и S, а так же значения состояний триггера в текущий момент времени (Qt). B таблице переходов приведены значения состояний триггера в следующий момент времени (Qt +1). Переходы триггера из одного состояния в другое происходят, если на вход R или S подается сигнал «1».

При R = 0 и S = 0 состояние триггера не меняется. Такой режим называется режимом хранения. В случае если R = 0 и S = 1 триггер переходит в состояние «1» независимо от того, в каком состоянии он находился до изменения входных сигналов. При R = 1 и S = 0 триггер переходит в состояние «0». Таким образом, для записи «1» в RS -триггер необходимо подать на его входы сигналы R =0 и S = 1, для записи «0» – сигналы R = 1 и S = 0. Комбинация сигналов R =1 и S =1 является запрещенной, состояние триггера при этом не определено.

Таблица переходов триггера может быть интерпретирована как таблица истинности комбинационной схемы, в которой значения сигналов на входах Rt, St и значение текущего состояния Qt можно рассматривать как логические переменные, a Qt + l – как логическую функцию (табл. 2.5).

Таблица 2.5. Таблица переходов RS -триггера

| Входы | Текущее состояние | Следующее состояние | |

| R | S | Qt | Qt +1 |

| Запрещенная комбинация | |||

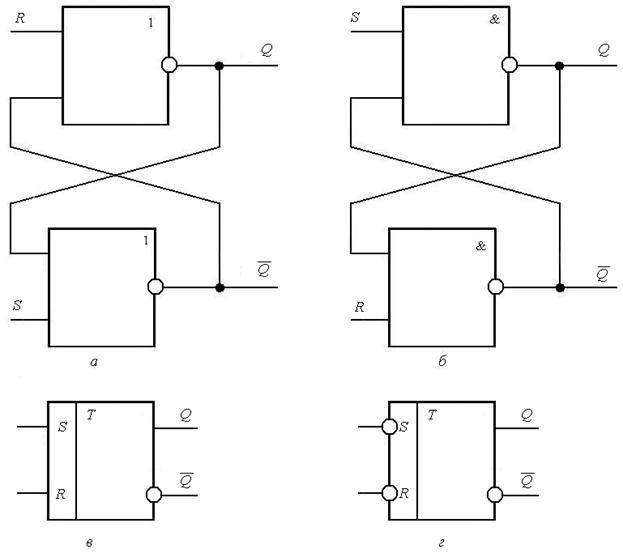

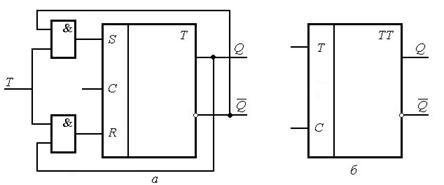

RS -триггер может быть построен на различных логических элементах. Функциональная схема асинхронного RS -триггера, построенного на элементах И-НЕ и ИЛИ-НЕ, а также его графическое обозначение показаны на рис. 2.14.

Рис. 2.14. Асинхронный RS -триггер:

а – на элементах ИЛИ-НЕ; б – на элементах И-НЕ;

в – условное графическое обозначение RS -триггера с прямыми входами;

г – условное графическое обозначение RS -триггера с инверсными входами

Асинхронный RS -триггер представляет собой бистабильную ячейку, поэтому он используется как основа при построении всех триггеров.

2.12.3. Синхронный RS -триггер

Этот триггер имеет дополнительно вход С, на который поступает синхросигнал. Информационные сигналы R и S могут изменять состояние триггера только при значении синхросигнала С = 1. Таблица переходов синхронного RS -триггера состоит из двух частей. Первая часть таблицы описывает переходы триггера при С = 1 и совпадает с таблицей переходов асинхронного триггера (табл. 2.4). Когда С = 0, триггер не меняет своего состояния при любой комбинации сигналов на информационных входах и логика его переходов может быть описана табл. 2.6.

Таблица 2.6. Переходы синхронного RS -триггера

| Входы | Состояния | |||

| R | S | C | ||

| Запрещенная комбинация |

При С = 0 разрешенными являются любые комбинации входных сигналов, в том числе R = 1, S = 1.

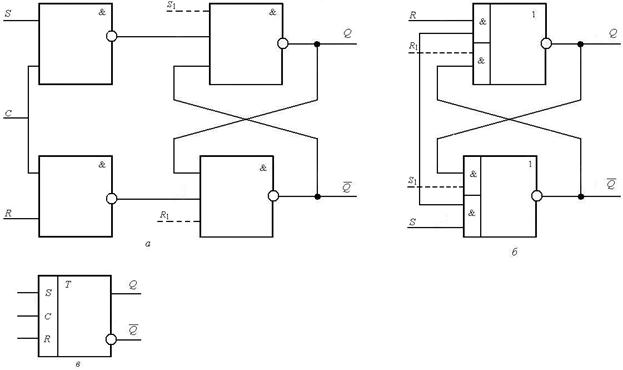

На рис. 2.15 приведены функциональные схемы синхронных RS -триггеров, реализованных на элементах И-НЕ и И-ИЛИ-НЕ, и их условное графическое обозначение. Кроме основных входов R и S там показаны дополнительные входы R 1и S 1, которые являются асинхронными. При подаче сигналов на них состояние триггера может изменяться независимо от значения сигнала С. В каждый момент времени можно управлять переходами триггера только с помощью синхронных или только с помощью асинхронных входов.

Рис. 2.15. Синхронный RS-триггер:

а – на элементах И-НЕ; б – на элементах И-ИЛИ-НЕ;

в – условное графическое обозначение

2.12.3. Двухтактный RS -триггер

Триггеры используются в различных узлах ЭВМ, между которыми осуществляется передача информации. Устойчивая работа цепочки триггеров происходит только в том случае, когда запись новой информации в триггер производится после считывания прежней и передачи ее в следующий по цепочке триггер.

Это возможно при использовании двух серий синхроимпульсов, сдвинутых относительно друг друга на полпериода. Такой принцип управления и синхронизации применяется в двухтактных триггерах. Двухтактные триггеры используются в сдвигающих регистрах, а также в качестве элементов памяти в цифровых автоматах с памятью для устранения эффекта гонок.

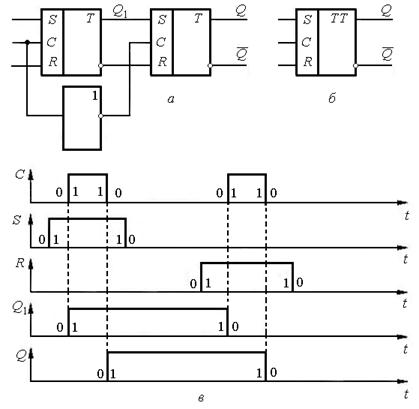

Простейшая схема двухтактного RS -триггера может быть построена из двух однотактных, причем синхросигналы на входы С первого и второго триггеров должны подаваться в противофазе. Это делается с помощью инвертора (рис. 2.16, а).

Рис. 2.16. Двухтактный RS-триггер:

а – схема; б – условное графическое обозначение;

в – временная диаграмма работы

В основном поле условного графического обозначения двухтактного триггера записываются две буквы Т (рис. 2.16, б). Особенности переключения двухтактного триггера из одного состояния в другое поясняются временной диаграммой (рис. 2.16, в).

Пусть оба триггера находятся в состоянии «0» и на входы триггера поступают сигналы S = 1 и R = 0 (запись в триггер сигнала «1»). При поступлении на вход RS -триггера сигнала С = 1 входная информация по переднему фронту сигнала С запоминается в первом однотактном триггере (он переходит в состояние «1»). Второй однотактный триггер хранит информацию о предыдущем состоянии, так как на его входе С = 0.

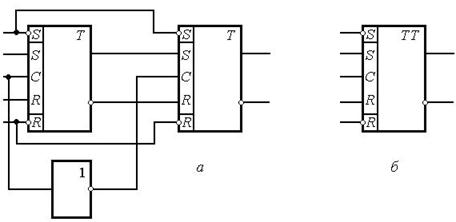

По окончании действия синхросигнала (по заднему фронту), т.е. при С = 0, первый триггер переходит в режим хранения, а информация с выходов первого триггера передается на вход второго триггера. Так как на входе второго триггера сигнал С = 1, он также переходит в состояние «1». В результате к началу следующего такта на выходе двухтактного RS -триггера появится сигнал состояния, соответствующего входной информации. Аналогичным образом производится запись в двухтактный триггер сигнала нуля. Для установки RS -триггера в «0» или «1» независимо от присутствия сигнала на входе С в схему вводят прямые или инверсные входы R и S асинхронной установки (рис. 2.17, а) и отображают их на условном графическом обозначении (рис. 2.17, б).

Рис. 2.17. Двухтактный RS -триггер с дополнительными входами R и S:

а – схема; б – условное графическое обозначение

2.12.4. Асинхронный и синхронный D -триггеры

В вычислительной технике широко применяют D -триггеры, которые реализуют функцию временной задержки входного сигнала. Также D -триггеры имеют один информационный вход. Логика работы асинхронного D -триггера описывается таблицей переходов (табл. 2.7).

Таблица 2.7. Переходы асинхронного D -триггера

| Вход | Состояния | |

| D | ||

В асинхронном D -триггере состояние (выходной сигнал) Qt +1повторяет значение входного сигнала Dt, поэтому асинхронный D -триггер по существу не является элементом памяти и рассматривается только как основа для построения синхронного D -триггера.

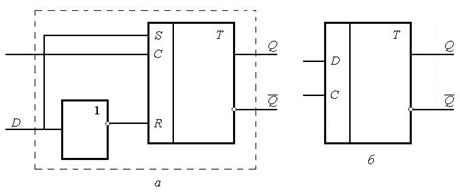

Функциональная схема и условное графическое обозначение синхронного D -триггера, построенного на основе синхронного RS -триггера, показаны на рис. 2.18. Для преобразования RS -триггера в D -триггер сигнал D подается на вход S непосредственно, а на вход R – через инвертор. Если при С = 1 на вход D подать сигнал «1», то триггер перейдет в состояние «1», а при подаче сигнала D = 0 в триггер будет записан «0». Таким образом, для записи в D -триггер единицы на вход D нужно подать сигнал «1», а для записи нуля – сигнал «0» (так как триггер синхронный, на вход С необходимо в обоих случаях подавать сигнал «1»). Это делает D -триггер удобным для использования в схемах статической памяти, так как для записи достаточно иметь одну линию на разряд данных. При этом сигнал С является общим для всех разрядов записываемых данных.

Рис. 2.18. Синхронный D -триггер:

а – схема; б – условное графическое обозначение

Логику работы синхронного D -триггера описывает табл. 2.8. Эту логику можно охарактеризовать выражением «что надо записать в D -триггер, то и подается на его вход».

Таблица 2.8. Переходы синхронного D -триггера

| Входы | Состояния | ||

| D | C | ||

Наличие входа синхронизации позволяет записывать новые данные в триггер только в определенные моменты времени (при С = 1). В промежутках между ними данные в триггере сохраняются без изменения. При чтении данных из триггера его состояние также не меняется.

2.12.5. T -триггер

Этот триггер имеет один информационный вход. Логику работы асинхронного Т -триггера характеризует таблица переходов (табл. 2.9).

Таблица 2.9. Переходы асинхронного Т -триггера

| Входы | Состояния | |

| Т | ||

При Т = 1 асинхронный Т -триггер меняет свое состояние на противоположное, а при Т = 0 состояние триггера не изменяется.

Так как Т -триггер суммирует (или подсчитывает) по модулю два числа единиц, поступающих на его информационный вход, то Т -триггер называют также триггером со счетным входом.

Логику работы синхронного Т -триггера описывает табл. 2.10.

Таблица 2.10. Переходы синхронного Т -триггера

| Входы | Состояния | ||

| С | Т | ||

При С = 0 триггер не изменяет своего состояния, а при С = 1 работает как асинхронный Т -триггер.

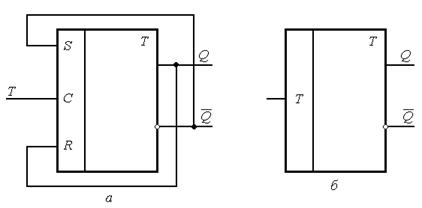

Функциональная схема Т -триггера может быть построена на основе синхронного RS -триггера (однотактного или двухтактного). Схемы асинхронного и синхронного Т -триггеров показаны на рис. 2.19 и 2.20 соответственно.

Рис. 2.19. Асинхронный Т -триггер:

а – схема; б – условное графическое обозначение

Рис. 2.20. Синхронный N-триггер:

а – схема; б – условное графическое обозначение

Поскольку на этих схемах сигнал с выхода триггера поступает на его же вход, триггер должен во время переключения сохранять состояние и одновременно воспринять новую информацию. Для устойчивой работы в этом случае целесообразно использовать двухтактные триггеры.

2.12.6. JK -триггер

Такие триггеры называют универсальными. Универсальность схемы JK -триггера состоит в том, что простой коммутацией входов и выходов можно получать схемы других типов триггеров.

JK -триггер имеет два информационных входа. Вход J используется для установки триггера в состояние «1», а вход К – в состояние «0», т.е. входы J и K аналогичны входам S и R RS -триггера. Отличие JK -триггер от RS -триггера заключается в том, что на входы J и K могут одновременно поступать сигналы «1». В этом случае JK -триггер изменяет свое состояние. Таким образом, он работает так же, как RS -триггер, за исключением комбинации сигналов J = 1; K = 1, при которой он работает как Т -триггер.

При С = 1 переходы JK -триггера описывает табл. 2.11.

Таблица 2.11. Переходы JK-триггера

| Входы | Состояния | ||

| J | K | ||

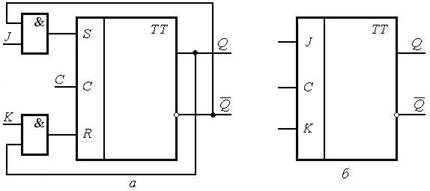

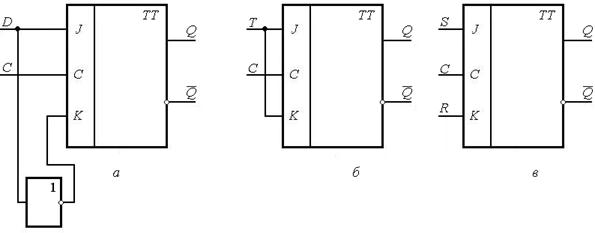

Функциональная схема двухтактного JK -триггера и его условное графическое изображение показаны на рис. 2.21. Этот триггер представляет собой комбинацию RS - и Т -триггеров, что согласуется с логикой его работы. Примеры построения других типов триггеров на основе JK -триггера представлены на рис. 2.22. Следует отметить, что триггер любого типа можно преобразовать в любой другой триггер.

Рис. 2.21. Двухтактный JK-триггер:

а – схема; б – условное графическое обозначение

Рис. 2.22. Схемы преобразования JK -триггера:

а – в D -триггер; б – в Т -триггер; в – RS -триггер

2014-02-02

2014-02-02 10711

10711