Цель: получить основные сведения о цифровых логических автоматах без памяти.

Образовательные результаты по ФГОС:

Знать: сущность физических процессов, протекающих в электронных приборах и устройствах; принципы включения электронных приборов и построения электронных схем;

типовые узлы и устройства электронной техники.

Уметь: определять и анализировать основные параметры электронных схем и устанавливать по ним работоспособность устройств электронной техники; производить подбор элементов электронной аппаратуры по заданным параметрам.

Задание: составить конспект лекции, выделить главное, ответить на контрольные вопросы.

План.

Тема: Цифровые логические автоматы без памяти.

Цифровыми логическими автоматами без памяти, или комбинационными логическими устройствами, называются электронные цифровые устройства, логические значения на выходах которых однозначно определяются совокупностью логических значений на входах в данный момент времени. К логическим автоматам без памяти относятся дешифраторы, шифраторы, мультиплексоры, демультиплексоры, сумматоры и другие цифровые устройства, выпускаемые в виде интегральных схем.

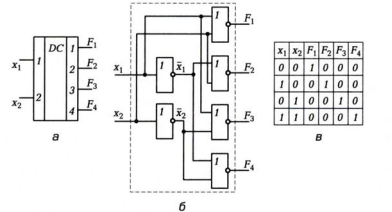

Дешифратором называется устройство, вырабатывающее сигнал логической 1 только на одном из своих 2л выходов в зависимости от кода двоичного числа на п входах. На рисунке 1а-в приведены: условное обозначение интегральной схемы дешифратора наm = 2 входа и 2n = 4 выхода, его функциональная схема и таблица истинности. Часто схемы дешифраторов изготовляются с дополнительными входами, например входом разрешения (стробирования). Стробирование позволяет исключить появление на выходах дешифратора ложных сигналов, запрещая его работу в интервале времени переходного процесса при изменении цифрового кода на входе.

Рисунок 1-Условное обозначение интегральной схемы дешифратора его функциональная схема и таблица истинности

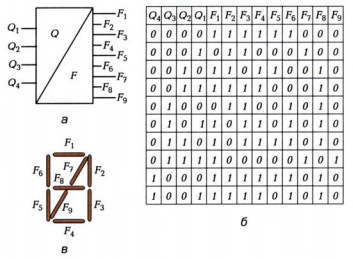

Преобразователь кодов (шифратор) отличается от дешифратора тем, что каждому набору логических 1 и О на входе ставит в однозначное соответствие набор логических 1 и О на выходе. Примером может служить интегральная схема и ее таблица истинности на рисунке 2а и б, преобразующая код двоичного числа Q4,Q3,Q2,Q1 (цифры в индексах указывают номера разрядов) в сигналы управления F1 - F9 девятью сегментами светового индикатора (рисунок 2в). Шифратор выполняет функцию, обратную дешифратору. Он имеет 2n входов, на один из которых подается логическая 1, а на остальные -0. При этом на п выходах код двоичного числа должен соответствовать номеру единичного входа.

Рисунок 2-Условное обозначение интегральной схемы шифратора и его таблица истинности

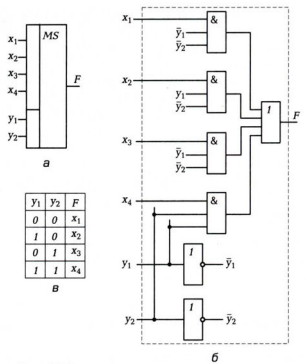

Мультиплексором называется устройство для коммутации одного из 2m информационных входов на один выход. Для реализации необходимой коммутации мультиплексор имеет кроме информационных входов также m адресных входов. Значение числа в двоичном коде на адресных входах определяет адрес коммутируемого информационного входа. Условное обозначение интегральной схемы мультиплексора с двумя адресными m = 2 (y1 и y2) и четырьмя информационными 2m = 4 (х1,x2,x3,x4) входами, его функциональная схема и таблица истинности приведены на рисунке 3а-в.

Рисунок 3-Условное обозначение интегральной схемы мультиплексора, его функциональная схема и таблица истинности

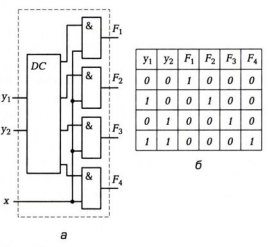

Демультиплексор выполняет функцию, обратную мультиплексору. С его помощью осуществляется коммутация одного информационного входа на один из 2m информационных выходов в зависимости от значения числа в двоичном коде на т адресных входов. Пример схемной реализации демультиплексора с двумя адресными m = 2 (y1 и y2) входами и четырьмя информационными m = 4 (F1, F2, F3, F4) выходами и его таблица истинности, в которой учтена таблица истинности дешифратора (см. рисунок 1в), приведены на рисунке 4а и б.

Рисунок 4-Схемная реализация демультиплексора

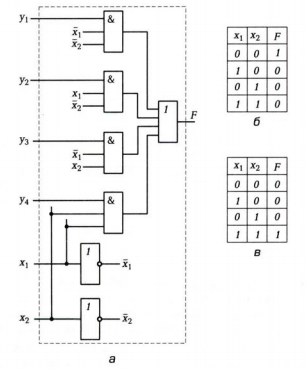

Генератором логических функций называется устройство, позволяющее получить на своем выходе желаемую функцию значений логических величин на его информационных входах. Такие генераторы реализуются на основе мультиплексоров (см. рисунок 3б), в которых назначение управляющих и информационных входов следует поменять местами. Так, задавая на управляющих входах y1, y2, y3, y4 генератора логических функций (рисeyrt5а) соответствующие значения логических 1 и О, получим на выходе любую функцию F величин на информационных входах x1 и x2. Например, логическим функциям  и

и  , таблицам истинности на рисунке 5б и в, соответствуют значения y1, y2, y3, y4 = 1000 и 0001. Такой способ получения логических функций позволяет унифицировать элементную базу в интегральном исполнении и сократить время проектирования логических автоматов.

, таблицам истинности на рисунке 5б и в, соответствуют значения y1, y2, y3, y4 = 1000 и 0001. Такой способ получения логических функций позволяет унифицировать элементную базу в интегральном исполнении и сократить время проектирования логических автоматов.

Рисунок 5-Схемная реализация генератора логических функций

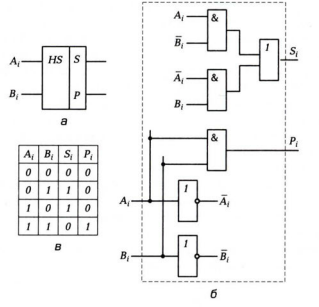

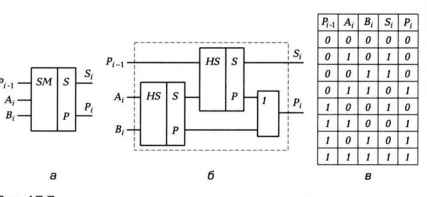

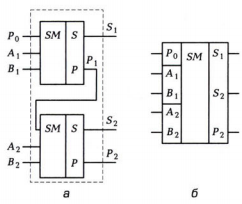

Сумматором называется устройство для арифметического сло жения двух двоичных чисел. Сложение двух одноименных i-x ра рядов с учетом переносов из младшего (i - 1)-го разряда в старший (i + 1)-й разряд осуществляется одноразрядным сумматором, который составляется из одноразрядных полусумматоров. Последние не учитывают перенос из младшего разряда. На рисунке 6а-в приведены условное обозначение интегральной схемы одноразрядного полусумматора, его функциональная схема и таблица истинности, где Аi и Вi - одноименные разряды двух двоичных чисел; Si- сумма; Рi- перенос в старший разряд. Условное обозначение интегральной схемы одноразрядного сумматора, его функциональная схема и таблица истинности приведены на рисунке 7а-в. Из одноразрядных составляются многоразрядные сумматоры. Схема и условное обозначение интегральной схемы двухразрядного сумматора приведены на рисунке 8а и б.

Рисунок 6-Условное обозначение интегральной схемы одноразрядного полусумматора, его функциональная схема и таблица истинности

Рисунок 7-Функциональная схема и таблица истинностиодноразрядного сумматора

Рисунок 8-Схема и условное обозначение интегральной схемы двухразрядного сумматора

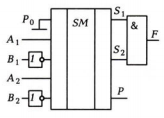

Цифровым компаратором называется устройство сравнения двоичных чисел. Одна из возможных схем реализации с применением сумматора приведена на рисунке 9. Действительно, если в одноименных разрядах Аi= Вi, где i - номер разряда, то сумма значений Аi и Bi равна Si = 1 и перенос в старший разряд Pi = 0.Таким образом, при равенстве двух двоичных чисел на выходе сумматора S1 = S2 = 1 и Р = О, а на выходе логического лемента F = 1. Приведенная схема цифрового компаратора может также фиксировать неравенство двух двоичных чисел А2А1 >B2B1, при котором на выходе сумматора перенос в старший разряд Р = 1.

Рисунок 9-Схема реализациицифрового компаратора

Контрольные вопросы.

1. Назовите основные признаки логических автоматов с памятью.

2. Приведите примеры логических автоматов с памятью.

2021-08-14

2021-08-14 316

316