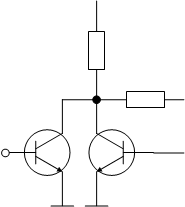

1. Режим раздельного переключения

+UП

Rк Rк

Rб Rб +UП

Rк Rк

Rб Rб

VT3 VT1 VT2 VT4 Iвх.1 Iвх.2 |

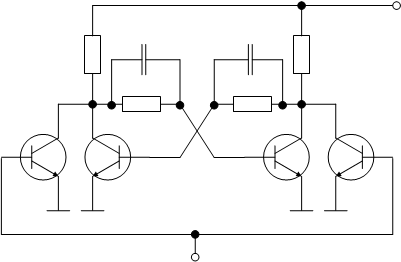

Триггер переключается поочередной подачей отпирающих (или запирающих) сигналов на два раздельных входа.

В данной схеме параллельно транзисторам VT1 и VT2, входящим в состав БЯ, подключены управляющие транзисторы VT3 и VT4. Эти ключи управляются отпирающими импульсами тока Iвх.1 и Iвх.2 соответственно. В отсутствие управляющих токов транзисторы VT3 и VT4 закрыты и не влияют на состояние триггера. Это режим хранения. При подаче тока Iвх.1 открывается и входит в насыщение VT3, что приводит к запиранию VT2 низким потенциалом коллекторов VT1 и VT3. При этом откроется и войдет в насыщение VT1. После окончания импульса тока Iвх.1 триггер останется в новом состоянии: на выходе левого плеча низкий уровень напряжения  , а на выходе правого – высокий уровень

, а на выходе правого – высокий уровень  .

.

Повторные импульсы тока Iвх.1 не влияют на состояние триггера. Переключение триггера в другое устойчивое состояние произойдет при поступлении на второй вход импульса тока Iвх.2. Недопустима подача отпирающих импульсов тока Iвх.1 и Iвх.2 одновременно на оба входа. Во время их действия откроются оба транзистора VT3 и VT4, и после окончания импульсов Iвх.1 и Iвх.2 откроются транзисторы VT1 и VT2 и окажутся в активной области. В результате регенеративного процесса триггер с равными вероятностями может оказаться в любом из устойчивых состояний, т.е. результат будет неопределенным. Рассмотренный вариант схемы называется триггером RS –типа: вход S (set) – установка “1”, вход R (reset) – установка “0”.

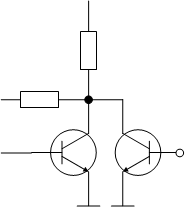

2. Режим общего входа

Управляющий сигнал (импульс тока) подается на оба соединенных вместе входа триггера, и по каждому очередному сигналу триггер переключается в противоположное состояние. Для того, чтобы устойчивые состояния менялись регулярно после каждого входного импульса, схема должна иметь внутреннюю память. Функция этой памяти состоит в том, чтобы хранить информацию о предыдущем состоянии триггера в течение всего времени действия очередного управляющего сигнала, а после его окончания обеспечить принудительный переход БЯ в новое состояние, противоположное предыдущему.

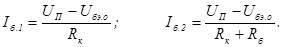

Схема триггера с емкостной памятью

+UП

Rк +– С1 С2 Rк

Rб Rб

VT3 VT1 VT2 VT4

Iвх

VT3 VT1 VT2 VT4

Iвх

|

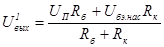

Пусть в исходном состоянии VT1 закрыт, а VT2 насыщен. Конденсатор С1 заряжен: UC1=

а С2 разряжен: UС2 =0.

а С2 разряжен: UС2 =0.

При по-даче управля-ющего сигнала ключи VT3 и VT4 отпираются до насыщения, потенциалы их коллекторов падают до нуля, и потенциал базы VT2 оказывается отрицательным: Uб.2 =–UС1, а базы VT1 – нулевым. Во время действия входного сигнала транзистор VT1 остается закрытым, а VT2 выходит из насыщения и закрывается. Если длительность входного импульса меньше постоянной времени разряда конденсатора С1, напряжение UC1 до конца этого сигнала сохранится.

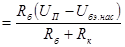

По окончании сигнала в базы VT1 и VT2 поступают неодинаковые отпирающие токи:

Так как Iб.1 > Iб.2 , ток коллектора VT1 нарастает с большей скоростью, чемв VT2. Поэтому ток Iк.1 будет подавлять ток базы Iб.2. В результате регенеративного процесса VT2 окажется закрытым, а VT1 через некоторое время войдет в насыщение. Таким образом, триггер изменил свое первоначальное состояние.

2014-02-24

2014-02-24 663

663