Исследование JK-триггера

Исследование D-триггера

Триггер D выполняет функцию задержки информации, поступающей на управляющий вход на один такт синхросигналов, поэтому такие триггеры называются синхронными. После поступления тактового импульса синхронизации D -триггер устанавливается в состояние соответствующее входу D.

Рисунок 56 - Принципиальная схема исследования D-триггера в динамическом режиме и его условное изображение

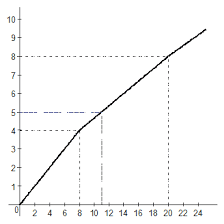

Рисунок 57 - Временная диаграмма D-триггера. Частота на входе С равна 1 кГц (сверху), частота синхроимпульсов на входе D – 400 Гц (посередине). На выходе Q (внизу) видно, как происходит задержка

Характеристическое уравнение D -триггера имеет вид:

Qn+1 = D.

Триггер JK является наиболее распространенным синхронным триггером. Вход J служит для установки «1», вход K – для установки «0».

Отличие JK -триггера от RS -триггера заключается в том, что он не имеет запрещенных комбинаций входных сигналов и при J = K = «1» меняет значения выходных сигналов на противоположные. Это позволяет использовать его как счетный T -триггер.

Рисунок 58 - Принципиальная схема исследования JK-триггера в динамическом режиме и его условное обозначение

Таблица 11 - Экспериментальная таблица истинности JK-триггера

| Вход | Выход | |||

| C | J | K | Q | НЕ Q |

| Без изменения | ||||

| Противоположное |

Характеристическое уравнение T -триггера имеет вид:

Qn+1 = J (~Q)n + (~ K) Qn.

4.Вопросы:

1. Основные обозначения триггера.

2. Схема простейшего RS- триггера.

3. Статистический RS-триггер.

4. Экспериментальная таблица истинности статическихRS-триггеров.

5. Экспериментальная таблица истинности синхронногоRS-триггера.

6. Экспериментальная таблица истинности JK-триггера.

Тема 9:

"Шифраторы и дешифраторы"

Содержание:

- Шифратор

- Дешифратор

- Вопросы

Шифратор (кодер) — (англ. encoder) логическое устройство, выполняющее логическую функцию (операцию) — преобразование позиционного n-разрядного кода в m-разрядный двоичный, троичный или k-ичный код.

Двоичный шифратор выполняет логическую функцию преобразования унитарного n-ичного однозначного кода в двоичный. При подаче сигнала на один из n входов (обязательно на один, не более) на выходе появляется двоичный код номера активного входа.

Если количество входов настолько велико, что в шифраторе используются все возможные комбинации сигналов на выходе, то такой шифратор называется полным, если не все, то неполным. Число входов и выходов в полном шифраторе связано соотношением:

где:

n— число входов,

m— число выходных двоичных разрядов.

Троичный шифратор выполняет логическую функцию преобразования унарно n-ичного однозначного (одноединичного или однонулевого) кода в троичный. При подаче сигнала («1» в одноединичном коде или «0» в однонулевом коде) на один из n входов на выходе появляется троичный код номера активного входа.

Число входов и выходов в полном троичном шифраторе связано соотношением:

, где:

n— число входов,

m— число выходных троичных разрядов.

Число входов и выходов в полном k-ичном шифраторе связано соотношением:

, где

n— число входов,

m— число выходных k-ичных разрядов,

k— основание системы счисления.

Приоритетный шифратор отличается от шифратора наличием дополнительной логической схемы выделения активного уровня старшего входа для обеспечения условия работоспособности шифратора (только один уровень на входе активный). Уровни сигналов на остальных входах схемой игнорируются.

2014-02-24

2014-02-24 982

982