Особенности динамической памяти

Алгоритм записи и считывания информации

Структурная схема ИС

Основные запоминающие элементы динамической памяти

1.1 Динамические ячейки БИС ОЗУ строятся в основном по n-МОП технологии и характеризуются отсутствием транзисторов, работающих в качестве нагрузочных резисторов. Роль "хранилища" информации во всех схемах играет емкость затвор-исток n-МОП транзистора. Применение динамических ячеек позволяет значительно упростить топологию БИС-ЗУ и повысить плотность компоновки ячеек на кристалле.

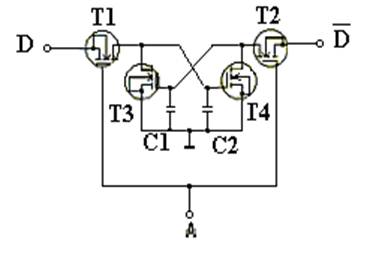

1.2 Простейшая динамическая ячейка показана на рисунке 1. Во время записи управляющий импульс на шине адреса А открывает транзисторы Т1 и Т2. При этом емкости затворов С1 и С2 заряжаются парафазными токами линий шины данных.

Рисунок 1 – Динамическая ячейка ЗУ с двумя запоминающими емкостями

- линии записи/ считывания шины данных i – разряда;

- линии записи/ считывания шины данных i – разряда;

А – адресная шина записи – считывания i – разряда;

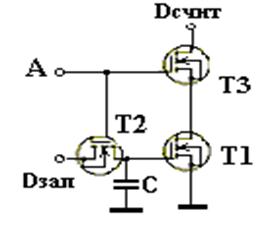

1.3 В динамической ячейке ЗУ, схема которой приведена на рисунке 2, информация хранится на конденсаторе С.

Рисунок 2 – Динамическая ячейка ЗУ с одной запоминающей емкостью и одной адресной шиной

Dзап - линия записи шины данных i – разряда;

Dсчит - линия считывания i – разряда шины данных;

А – адресная шина записи – считывания i – разряда;

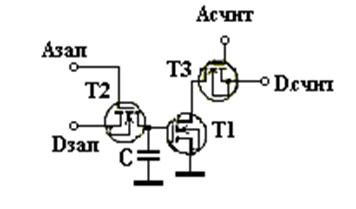

1.4 Схема, показанная на рисунке 3, выполнена аналогичным образом, но имеет раздельные адресные шины для записи и считывания информации. При записи «1» емкость заряжается в течении действия импульса "запись", поступающего на затвор Т2. Считывание информации производится через транзистор Т3, отпираемый сигналом "считывание", при этом потенциал на выходе ячейки зависит от напряжения на емкости С. При высоком уровне напряжения на емкости транзистор Т1 открыт и на выходе будет напряжение, близкое к нулю. При отсутствии заряда на емкости будет считываться сигнал 1.

Рисунок 3– Динамическая ячейка ЗУ с одной запоминающей емкостью и раздельными шинами считывания и записи

Dзап - линия записи шины данных i – разряда;

Dсчит - линия считывания i – разряда шины данных;

Асчит – адресная шина записи – считывания i – разряда;

Азап – адресная шина записи;

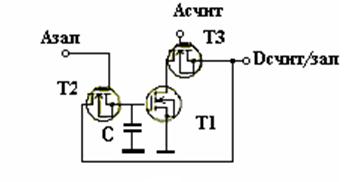

1.5 Схема динамической ячейки памяти на рисунке 4 характеризуется наличием раздельных адресных шин записи и считывания при общей информационной шине "записи-считывания" данных.

Рисунок 4 –Динамическая ячейка ЗУ с одной запоминающей емкостью, с раздельными шинами считывания и записи и с одной шиной данных

Dзап/счит - линия записи/считывания шины данных i – разряда;

Асчит – адресная шина записи – считывания i – разряда;

Азап – адресная шина записи;

2014-02-09

2014-02-09 882

882