Архитектура Intel Core (ядро Intel) содержит следующие компоненты:

· Wide Dynamic Execution;

· Advanced Smart Cache;

· Smart Memory Access;

· Advanced Digital Media Boost.

Компонент Wide Dynamic Execution (широкое динамическое выполнение) позволяет каждому процессору загружать, диспетчировать и выполнять с высокой пропускной способностью команды программ. Основными характеристиками этого компонента являются:

· эффективный конвейер, содержащий 14 этапов;

· три арифметико-логических устройства – ALU (Arithmetic-Logical Units);

· 4 декодера для декодирования до 5 команд за цикл;

· слияние макроопераций и микроопераций для повышения пропускной способности входной шины;

· пиковая скорость диспетчирования до 6 микроопераций в цикле;

· пиковая пропускная способность отмены команд до 4 микроопераций в цикле;

· улучшенное предсказание переходов;

· узел слежения за указателем стека, позволяющий повысить эффективность выполнения вызова процедур.

Компонент Advanced Smart Cache (улучшенная интеллектуальная кэш-память) обеспечивает высокую пропускную способность при обмене между кэш-памятью L2 и ядром. Этот компонент имеет следующие характеристики:

· объем кэш-памяти L2 до 4 Мбайт;

· оптимизация для мультиядерной и однопоточной среды выполнения команд;

· 256-битовый внутренний путь к данным для повышения пропускной способности между кэш-памятью L2 и кэш-памятью данных L1.

Компонент Smart Memory Access (интеллектуальный доступ к памяти) предварительно загружает данные из памяти в ответ на шаблоны доступа к памяти и уменьшает задержку тактов при неправильном предсказании перехода. Этот компонент имеет следующие характеристики:

· аппаратные предварительные загрузчики данных из памяти для уменьшения задержки при отсутствии данных в кэш-памяти L2 и/или кэш-памяти данных L1;

· разрешение конфликтов между операциями чтения и записи по адресам обращения к памяти для улучшения механизма упреждающего выполнения команд.

Компонент Advanced Digital Media Boost (поддержка улучшенного цифрового медиа) улучшает выполнение большинства 128-битовых команд SIMD, а также позволяет выполнять до 8 операций с плавающей точкой за цикл. Кроме того, этот компонент обеспечивает три порта для диспетчирования выполнения команд SIMD.

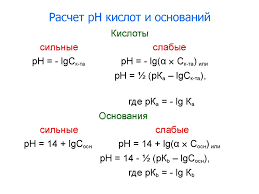

Основные компоненты архитектуры Intel Core и их связь представлены на рис. 1.3.21.

Разделяемая кэш-память L2 (в последних семействах процессоров Intel) доступна всем ядрам процессора (двум или четырем), причем объем память для каждого ядра определяется динамически. Например, в двухядерном процессоре из общего объема памяти 2 Мбайта первому процессору может быть выделено 1,5 Мбайт, а второму – 0,5 Мбайт.

Узел загрузки и предварительного декодирования выполняет предварительную загрузку команд в узел формирования очереди команд для поддержки постоянного запаса команд в узле декодирования. Загруженные команды также являются разделяемым, т.е. доступны и другим ядрам. При загрузке команд узел пытается «угадать», какие команды могут выполняться следующими, и загружает эти команды. «Угаданная» последовательность команд называется шаблоном команд. Кроме того, для повышения производительности узел формирования очереди команд выполняет кэширование коротких циклов.

Узел декодирования может декодировать в цикле 4 команды или 5 команд (при использовании слияния макроопераций). Для повышения пропускной способности узел сливает последовательность из двух макро- и микроопераций в одну микрооперацию. Такое слияние возможно для определенных последовательностей команд. Так, обычно после команды сравнения двух данных обычно следует команда условного перехода (например, при равенстве операндов). В этом случае эти команды можно объединить и при дальнейшей обработке они будут рассматриваться как одна команда.

Узел памяти Microcode ROM, как в архитектуре NetBurst, содержит коды микрокоманд, которые могут потребоваться узлу декодирования и узлу переименования/назначения.

Узел переименования/назначения выполняет те же действия, что и этапы 5-8 узла ядра в архитектуре NetBurst, т.е. замену имен регистров в команде именами одного из внутренних регистров процессора в RAT и назначение этих внутренних регистров команде.

Узел освобождения ресурсов (буфер переупорядочения) совмещает функции диспетчеризации ресурсов узла ядра, т.е. наличие данных и ресурсов для их выполнения, а также станции резервирования и узла освобождения ресурсов в архитектуре NetBurst.

Рис. 1.3.21. Основные компоненты архитектуры Intel Core и их связь

Планировщик направляет команды на выполнение на один из пяти портов.

Порт 1 выполняет команды работы с целыми числами и логические команды, команды перехода, перемещения, команды с плавающей точкой, а также команды MMX и SSE.

Порт 2 выполняет команды работы с целыми числами и логические команды, команды сложения с плавающей точкой, а также команды MMX и SSE.

Порт 3 выполняет команды работы с целыми числами и логические команды, команды умножения с плавающей точкой, а также команды MMX и SSE.

Порт загрузки обрабатывает команды, запрашивающие данные из оперативной памяти, а порт сохранения – команды, записывающие данные в оперативную память.

При загрузке и сохранении данных используется кэш-память данных L1 и кэш-память L2.

2014-02-10

2014-02-10 667

667