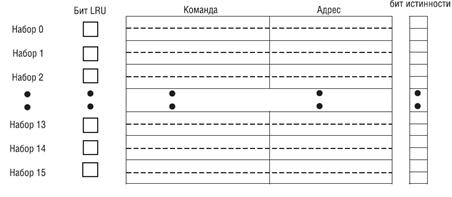

На рис. 3.15 показана блок_схема кэша команд. Кэш имеет 32 элемента. Элемент

состоит из пары регистров, содержащих команду и ее адрес. Каждый элемент

имеет бит «истинности», который установлен, если элемент содержит истинную

команду.

Элементы разделены на 16 наборов (пронумерованных от 0 до 15), содержащих

по два элемента каждый – элемент 0 и элемент 1. Каждый набор имеет бит LRU

(LRU – Least Recently Used), значение которого указывает, какой из двух

элементов содержит последнюю из недавно используемых команд (1=элемент 1,

0=элемент 0).

Рис. 3.15

Адрес любой возможной команды отображается в один из наборов в кэше, используя 4 младших бита адреса в качестве номера набора. Когда процессору необходимо выбрать команду из кэша, он использует 4 младших бита адреса как индекс определенного набора. Внутри этого набора он проверяет адреса двух элементов на наличие необходимой команды. Если команда обнаружена, происходит удачное обращение к кэшу. Бит LRU обновляется, если необходимо обозначить элемент, который не содержит необходимую команду.

Если ни один элемент в наборе не содержит необходимой команды, происходит неудачное обращение к кэшу. В этом случае новая команда и ее адрес загружаются в последний из недавно использованных элементов набора, адрес которого определяется 4 младшими битами адреса. Бит LRU переключается для того, чтобы указать, что сейчас другой элемент в наборе является последним недавно использованным.

Поскольку команды отображаются в набор с использованием 4 младших бит их адреса, нет необходимости хранить эти биты в кэше; 4 младших бита являются номером набора, в котором команда была сохранена. Фактически в элементе кэша хранятся только биты 23_4.

2015-01-30

2015-01-30 407

407