Рассмотрим для данной команды ФСА цикла ее исполнения

Цикл исполнения команд – это интервал времени, начиная с выборки команды из памяти, до ее завершения. Этот цикл можно представить в виде следующей диаграммы [1] (рис.1):

|

Рис. 1

ТЦ –время цикла исполнения команды.

Этапы цикла:

1.ТВК – время выборки команды и дешифрации кода операции.

2.∑ТАi – суммарное время выборки операндов.

3.ТОП – время выполнения операции.

4.ТРЕЗ – время размещения результата.

5.ТАК – время вычисления адреса следующей команды.

На рис.2 приведен ФСА цикла исполнения данной команды, на котором цифрами отмечены вышеперечисленные этапы. Рассмотрим подробно последовательности необходимых микроопераций в ФСА по этапам. При этом полезно обратиться к [1], стр.30-33.

Этап 1 соответствует выборке любой команды. Адрес текущей команды формируется на СЧАК в цикле исполнения предыдущей команды. Этот адрес по ША поступает на РАОЗУ и происходит обращение к ОЗУ в режиме «чтение».

Команда из соответствующей ячейки ОЗУ выбирается на РСОЗУ и по ШД передается на РК. Затем происходит дешифрация КОП. Для этого в контрольной работе достаточно ввести условную вершину, так как считаем, что ФСА разрабатывается только для одной заданной команды «сложение». Если КОП не соответствует нашей команде, устанавливается признак ошибки КОП, взводится триггер «ошибки» (Тош.), и все остальные процедуры не производятся – конец алгоритма.

Если присутствует команда «сложение», выполняются микрооперации 2-го этапа цикла исполнения – формирование исполнительных адресов и выборка операндов. Исполнительный адрес первого операнда Аисп.1 вычисляется сложением базовой константы, записанной в базовом регистре, со смещением [1], стр. 60-62. Предварительно анализируем значение поля В. Если программа находится в начале адресного пространства ОЗУ, базовая константа равна нулю, и обращения к РОН не требуется. Индикатором данной ситуации для процессора может служить наличие кода нуля в поле B. Тогда Аисп.1= А1, первый операнд выбирается из ОЗУ с помощью прямой укороченной адресации и пересылается с РСОЗУ в АЛУ на первый входной регистр.

Рис. 2

Если поле В не равно нулю, выполняются микрооперации вычисления исполнительного адреса или с помощью штатной арифметики (в стандартном АЛУ), если в алгоритме не предусматривается параллелизм процедур, или в автономном сумматоре. В рассматриваемом примере Аисп.1 формируется в дополнительном автономном сумматоре на регистре результата (РРсм), после чего первый операнд выбирается из ОЗУ.

Второй операнд по условию находится в перевернутом стеке, реализованном как область ОЗУ. Для его выборки предварительно инкрементируется УС, что осуществляет адресацию последней занятой ячейки. Затем следует обращение к стеку через РАОЗУ. Операнд выбирается на РСОЗУ и пересылается на второй входной регистр АЛУ.

3-й этап – выполнение операции. Процедуры, выполняемые в АЛУ для операции «сложение», в алгоритме заменены ждущей вершиной.

Результат операции формируется на РРАЛУ, и на 4-м этапе осуществляется его запись в РОН или в ОЗУ в зависимости от признака адресации ПА3. Если ПА3=1, то R адресует РОН, из которого читается адрес результата, и по этому адресу результат записывается в ОЗУ. ШАРОН вводится в схему процессора для возможности осуществления в одном такте обращения к РОН в режиме чтения адреса операнда и пересылки считанного адреса по ША на РАОЗУ. Если используется только одна ША, эта процедура разбивается на два такта.

При значении ПА3=0 поле R интерпретируется процессором, как прямой регистровый адрес, то есть результат записывается непосредственно из АЛУ в РОН.

Цикл команды завершается формированием на программном счетчике адреса следующей команды программы (5-й этап). Эта процедура может выполняться на первом этапе цикла и совмещаться с приемом команды на РК.

По функциональной схеме алгоритма строится структурная электрическая схема центральной части ЭВМ для реализации данной команды (рис.3). При построении данной схемы и всех последующих необходимо руководствоваться ГОСТ [3].

Задача №2. Перед разработкой МПА необходимо от ФСА первой задачи перейти к граф-схеме алгоритма (ГСА). Для этого строятся таблицы микроопераций и логических условий. В таблицу микроопераций (Табл. 4) необходимо выписать все неповторяющиеся микрооперации, а в таблицу логических условий (Табл. 5) – все неповторяющиеся осведомительные сигналы из ФСА.

Таблица 4

| Микрооперации | Логические условия | Микрооперации | Логические условия |

| ША:=СЧАК | y1 | ША:=РРсм | y16 |

| РАОЗУ:=ША | y2 | Р1АЛУ:=ШД | y17 |

| Чтение ОЗУ | y3 | УС:=УС+1 | y18 |

| ШД:=РСОЗУ | y4 | ША:=УС | y19 |

| РК:=ШД | y5 | чтение СТ | y20 |

| Тош.:=1 | y6 | Р2АЛУ:=ШД | y21 |

| ША:=А1 | y7 | ШАРОН:=R3 | y22 |

| ШАРОН:=В1 | y8 | ШД:=РРАЛУ | y23 |

| РАРОН:=ШАРОН | y9 | РСРОН:=ШД | y24 |

| Чтение РОН | y10 | запись РОН | y25 |

| ШД:=РСРОН | y11 | ША:=ШД | y26 |

| Р1см:=ШД | y12 | РСОЗУ:=ШД | y27 |

| ШД:=А1 | y13 | запись ОЗУ | y28 |

| Р2см:=ШД | y14 | СЧАК:=СЧАК+1 | y29 |

| РРсм:=Р1см+Р2см | y15 |

Таблица 5

| Логические условия | Осведомительные сигналы |

| ОЗУ слож В=0 СТ МП Слож ПА3 | x1 x2 x3 x4 x5 x6 |

Следует отметить, что в нашем примере мы различаем обращение к стеку и обращение к ОЗУ. Однако по условию стек является областью ОЗУ, и обращение к стеку происходит через РА ОЗУ. Поэтому при выполнении аналогичного задания не будет являться ошибкой замена управляющего сигнала y20 «чтение СТ» на сигнал y3 «чтение ОЗУ». Соответственно можно заменить осведомительный сигнал x4 «СТ» на сигнал x1 «ОЗУ».

ГСА строится на базе ФСА: микрооперации заменяются управляющими сигналами {y}, а логические условия - осведомительными сигналами {x}. Эти сигналы отображаются на схеме центральной части ЭВМ (Рис. 3).

В результате получаем ГСА следующего вида (рис. 4).

Рис. 4

Реализация блока управления на базе МПА с жесткой логикой (автомат МИЛИ).

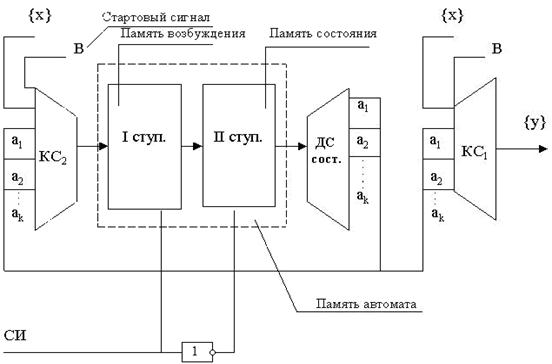

В состав (рис.5) микропрограммного автомата (МПА) входят следующие структурные элементы [2]: 2-х ступенчатая память автомата, дешифратор состояния (ДСсост.) и две комбинационные схемы КС1 и КС2. Память служит для запоминания состояния автомата. Во II ступени фиксируется текущее состояние, по которому комбинационная схема КС1 формирует набор управляющих сигналов. I ступень предназначена для формирования следующего состояния в зависимости от предыдущего и значений осведомительных сигналов. Переключение I ступени памяти осуществляет схема КС1. Двухступенчатая память применяется для исключения «гонок» из-за разницы в величине задержек в КС1 при переключении различных разрядов памяти.

Для ГСА (Рис.4) выходы операторных вершин, отмеченные символами а1, а2, …, а15 соответствуют состояниям памяти МПА.

Рис. 5

Рис. 5

Выход вершины «начало» и вход в вершину «конец» отмечен одним и тем же символом а1. Это соответствует одному и тому же состоянию памяти и означает, что после выполнение своих функций по генерации { y } в соответствии заданной ГСА, МПА возвращается в исходное положение до следующей инициализации. Для этого в ГСА после вершины «Начало» необходимо поставить ждущую вершину:

Начало работы автомата обеспечивает сигнал «В», устанавливаемый извне в «1» (интерпретируется как осведомительный сигнал). После этого он сбрасывается в «0», а МПА после завершения работы снова переходит в состояние покоя «а1».

Для реализации МПА необходимо по ГСА построить таблицу состояний и переходов автомата (Табл. 6) В ней отмечаются состояния МПА, управляющие сигналы, формируемые в каждом состоянии при наличии определенных значений осведомительных сигналов. Кроме того, в правой колонке таблицы записываются сигналы возбуждения памяти, формируемые по кодам состояния текущего и следующего состояния памяти. Значения сигналов определяются таблицами переключения триггеров, выбранных для построения памяти. В данном случае память реализована на RS-триггерах.

Таблица 6

| Текущее состояние | Код текущего состояния. | Управляя-ющие сигналы (вход. набор) | Осведомительные сигналы (условие) | Следующее состояние | Код следующего состояния | Сигналы возбуждения памяти |

| а1 | y1, у2, у3 - | В  | а2 а1 | S1 - | ||

| а2 | у4, y5 - |   | а3 а2 | R1, S2 - | ||

| а3 | у8,у9,у10 у6 у7,у2,у3 |    | а5 а1 а4 | R2 S3 S1 | ||

| а5 | у11,у12 | а6 | S1 | |||

| а6 | у13,у14 | а7 | R1, S2 | |||

| а7 | у15 | а8 | S1 | |||

| а8 | у16,у2,у3 | а4 | R3 | |||

| а4 | у4,у17 - |   | а9 а4 | R1, R2, S4 - | ||

| а9 | у18 | а10 | S1 | |||

| а10 | у19,у2,у20 | а11 | R1, S2 | |||

| а11 | у4,у21 - |   | а11 а12 | - S1 | ||

| а12 | - у22,у9,у10,у11,у26,у2 у22,у9,у23,у24,у25 |    | а12 а13 а15 | - R1, R2, S3 R1, S3 | ||

| а13 | у23,у27,у28 | а14 | S1 | |||

| а14 | - - |   | а14 а15 | - R1, S2 | ||

| а15 | у29 | а1 | R2, R3, R4, |

Таблица позволяет описать логическую организацию схем КС1 и КС2, т.е. произвести их абстрактный синтез

По полученным логическим выражениям производится структурный синтез схем КС1 и КС2 и строится электрическая функциональная схема МПА в соответствии с ГОСТ [3].

Реализация блока управления на базе МПА с программируемой логикой.

В МПА с программируемой логикой ГСА реализуется посредством микропрограммы (МКП), хранимой в управляющей памяти. Микропрограмма состоит из микрокоманд (МК), последовательность которых описывает граф-схему алгоритма управления.Микрокоманда представляет собой машинное слово, состоящее из двух полей (Рис. 6). Одна микрокоманда может соответствовать одной или двум вершинам ГСА.

| ОП | АП |

Рис. 6

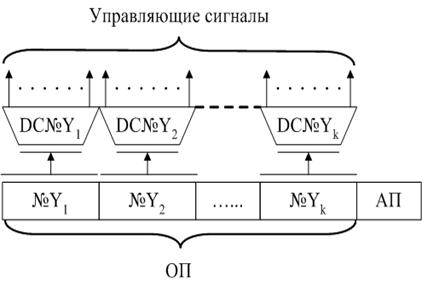

В операционном поле (ОП) микрокоманды записываются управляющие сигналы или их коды. В адресном поле (АП) – коды номеров условных вершин ГСА и адрес или адреса перехода к следующей микрокоманде. Организация поля ОП определяется выбранным способом микропрограммирования [2].

Для построения МПА требуется:

1. Выбрать способ микропрограммирования и способ перехода к следующей микрокоманде. Определить разрядность полей МК;

2. Для выбранного способа распределить управляющие сигналы по разрядам ОП;

3. Разработать микропрограмму;

4. Определить параметры управляющей памяти и всех регистров;

5. Описать работу блоков формирования управляющих сигналов и адреса перехода.

Предположим, что ОП организованно горизонтально - вертикальным способом. При этом способе операционное поле разбивается на сегменты (№Yi), число которых определяется максимальным количеством { y } в каких-либо операторных вершинах ГСА. После закрепления { y } за сегментами ОП, в каждом сегменте каждый управляющий сигнал представляется вертикальным способом (рис. 7), при котором управляющему сигналу ставится в соответствие двоичный код. Для получения управляющего сигнала двоичный код должен быть продешифрирован.

Рис. 7

В нашем случае ОП будет состоять из шести сегментов NY1 – NY6, по которым необходимо распределить управляющие сигналы. В каждом сегменте необходимо присвоить управляющим сигналам двоичные коды. При закреплении  за сегментами следует учесть, что если сигналы формируются в одной операторной вершине, они должны принадлежать различным сегментам. Один и тот же yi, указанный в различных операторных вершинах, должен принадлежать одному сегменту. Если в вершине ГСА записан только один yj, то его код записывается в соответствующем сегменте ОП. В остальных сегментах проставляется код отсутствия сигнала.

за сегментами следует учесть, что если сигналы формируются в одной операторной вершине, они должны принадлежать различным сегментам. Один и тот же yi, указанный в различных операторных вершинах, должен принадлежать одному сегменту. Если в вершине ГСА записан только один yj, то его код записывается в соответствующем сегменте ОП. В остальных сегментах проставляется код отсутствия сигнала.

Для рассматриваемой ГСА в табл. 7 приведено распределение  по сегментам ОП

по сегментам ОП

Таблица 7

| NY1 | NY2 | NY3 | NY4 | NY5 | NY6 | ||||||

| у2 | у1 | у3 | у11 | у7 | у2 | ||||||

| у4 | у5 | y10 | у24 | у22 | у2 | ||||||

| у6 | у9 | y15 | у27 | у27 | отс. | ||||||

| у8 | y14 | y17 | отс. | отс. | |||||||

| y12 | y16 | у20 | |||||||||

| y13 | y19 | у23 | |||||||||

| y18 | у21 | у29 | |||||||||

| отс. | отс. | отс. |

Способы перехода в микропрограммах к следующей микрокоманде определяются форматами адресных полей МК и правилами перехода. Принудительный переход выполняется по адресу, указанному в самой МК. Это соответствует безусловному переходу команд БП. При естественной адресации микрокоманд следующая микрокоманда адресуется посредством инкремента счетчика адреса микрокоманд (СЧАМК). Этот порядок может быть нарушен только управляющими микрокомандами. В зависимости от способа перехода к следующей МК различаются как микрокоманды, так и сами микропрограммные автоматы.

Микропрограммный автомат с принудительной адресацией МК.

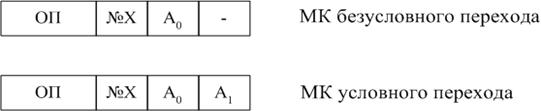

Форматы МК при принудительной адресации могут иметь следующий вид (рис. 8)

Рис. 8

По МК безусловного перехода (БП) адрес следующей микрокоманды определяется полем А0. Переход по МК условного перехода выполняется в зависимости от значения осведомительного сигнала xi, соответствующего анализируемой условной вершине №Xi. Если xi=0, то переход осуществляется по адресу А0, иначе по адресу А1.

Для идентификации МК УП и БП в поле №X записываются следующие коды: МК БП соответствует код «0»;

В МК УП каждой условной вершине присваивается свой двоичный код, записываемый в поле «NX».

Рассчитаем разрядность МК для нашего примера и напишем микропрограмму. Разрядность операционных полей МК определяется суммарной разрядностью сегментов NY1 – NY6. и составляет 15 двоичных разрядов (Табл. 7). Разрядность адресных полей МК в общем случае будет зависеть от количества микрокоманд МКП. При составлении микропрограммы целесообразно воспользоваться следующим правилом: обойти ГСА по «нулевым» выходам условных вершин, располагая микрокоманды по нарастанию адресов. Для микрокоманд, которые соответствуют «единичным» выходам условных вершин, отвести адреса свободных ячеек памяти. При этом каждой операторной вершине будет соответствовать одна микрокоманда. Если условная вершина следует за операторной, и на нее нет перехода, то обе эти вершины можно описать одной микрокомандой. При наличии перехода на условную вершину ей будет соответствовать отдельная микрокоманда. На ГСА (Рис.4) для удобства составления микропрограммы цифрами в кружках с правой стороны вершин графа отмечены номера ячеек всех микрокоманд микропрограммы для МПА с принудительной адресацией. В таблице 8. представлена МКП, описывающая рассматриваемый алгоритм управления.

Таблица 8

| Разр. | 0÷2 | 3÷5 | 6÷8 | 9÷10 | 11÷12 | 13÷14 | 15÷17 | 18÷22 | 23÷27 | Приме-чания |

| Адр. МКОП | NY1 | NY2 | NY3 | NY4 | NY5 | NY6 | NX | A0 | A1 | |

| <y2> | <y1> | <y3> | - | БП | ||||||

| NX1 | УП | |||||||||

| <y4> | <y5> | NX2 | УП | |||||||

| <y6> | - | БП | ||||||||

| <yk> | - | - | - | |||||||

| NX3 | УП | |||||||||

| <y8> | <y9> | <y10> | - | БП | ||||||

| <y12> | <y11> | - | БП | |||||||

| <y13> | <y14> | - | БП | |||||||

| <y15> | - | БП | ||||||||

| <y2> | <y16> | <y3> | - | БП | ||||||

| NX1 | УП | |||||||||

| <y4> | <y17> | - | БП | |||||||

| <y18> | - | БП | ||||||||

| <y2> | <y19> | <y20> | - | БП | ||||||

| NX4 | УП | |||||||||

| <y4> | <y21> | - | БП | |||||||

| NX5 | УП | |||||||||

| NX6 | УП | |||||||||

| <y9> | <y23> | <y24> | <y22> | <y25> | - | БП | ||||

| <y29> | - | БП | ||||||||

| <y2> | <y9> | <y10> | <y11> | <y22> | <y26> | - | БП | |||

| <y23> | <y27> | <y28> | БП | |||||||

| NX1 | УП | |||||||||

| <y2> | <y3> | <y7> | - | БП |

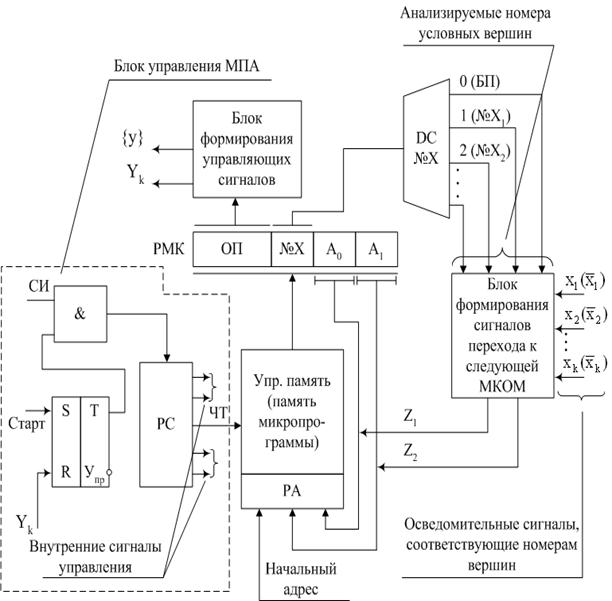

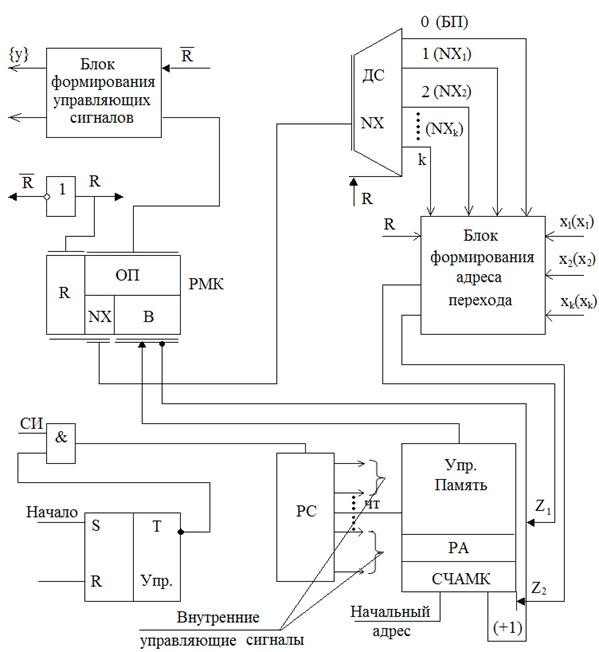

Рассмотрим структурную схему МПА с принудительной адресацией (Рис. 9). В состав МПА входят следующие блоки: управляющая память, регистр микрокоманд (РМК), блок формирования управляющих сигналов, блок формирования адреса перехода и блок управления МПА.

Управляющая память хранит различные микропрограммы управления. Может быть реализована как на ROM, так и на RAM. РМК хранит выбранную из памяти микрокоманду в течение такта работы процессора.Блок формирования управляющих сигналов генерирует по состоянию ОП на выходе множество управляющих сигналов в соответствующие временные такты.

Блок формирования адреса перехода анализирует состояние выходов DC№X и соответствующие осведомительные сигналы, и вырабатывает Z1 или Z2, которые обеспечивают передачу A0 или A1 на вход РА. В нашем случае:

,

,

где n = 6

Блок управления МПА строится на жестком временном распределителе сигналов (РС) и координирует работу всех блоков МПА.

Подробно с описанием работы МПА можно ознакомиться в [2].

Рис. 9

Микропрограммный автомат с естественной адресацией.

Рассмотрим вариант, предлагающий наличие двух типов микрокоманд (рис. 10): операционной, которая выполняет полезную работу и обрабатывает операторные вершины ГСА, и управляющей МК условного и безусловного переходов.

| R | ОП |

| R | NX | B |

Рис. 10

После выполнения операционной микрокоманды адрес следующей определяется естественным способом путем инкремента. В управляющих МК поле NX своим кодом (как и в МПА с принудительной адресацией) будет идентифицировать микрокоманды УП и БП. Для различения типов МК вводится одноразрядный признак R. Если R=0, то это операционная микрокоманда. Если R=1, то микрокоманда БП или УП. При данных форматах микрокоманд разряды ячеек памяти используются либо под операционную МК, либо под МК УП или БП.

Рассчитаем разрядность микрокоманд и напишем микропрограмму для ГСА, представленного на рисунке 4. Слева от вершин графа в квадратах отмечены номера ячеек управляющей памяти, содержащих соответствующие МК. Для принятого нами смешанного способа микропрограммирования операционная МК будет иметь 15 разрядов, управляющая МК –8 разрядов. Разрядность ячеек памяти определяется по микрокоманде, имеющей б о льшую разрядность.

При составлении микропрограмм можно пользоваться следующим правилом: обходить ГСА сверху вниз по «нулевым» выходам условных вершин, располагая МК в порядке очереди; МК, соответствующие «единичным» выходам условных вершин, располагать в следующих незанятых ячейках памяти. Микропрограмма представлена в таблице 9.

Структурная схема МПА с естественной адресацией МП (рис. 11) представляет собой композицию блоков, аналогичных по назначению тем, которые представлены на рис. 9 [2].

Отличие заключается лишь в наличие на входе управляющей памяти счетчика адреса микрокоманд (СЧАМК) и в описании функций блока формирования адреса перехода.

Таблица 9

| Адр. МКОП | R | NY1 | NY2 | NY3 | NY4 | NY5 | NY6 | Приме-чания | |

| Разр. | 1÷3 | 4÷6 | 7÷9 | 10÷11 | 12÷13 | 14÷15 | |||

| Адр. МКОП | R | NX | В | 00…………………………0 | |||||

| Разр. | 1÷3 | 4÷7 | 8 15 | ||||||

| <y2> | <y1> | <y3> | ОП МКК | ||||||

| NX1 | УП МКК | ||||||||

| <y4> | <y5> | ОП МКК | |||||||

| NX2 | УП МКК | ||||||||

| <y6> | ОП МКК | ||||||||

| <yk> | |||||||||

| NX3 | УП МКК | ||||||||

| <y8> | <y9> | <y10> | ОП МКК | ||||||

| <y12> | <y11> | ОП МКК | |||||||

| <y13> | <y14> | ОП МКК | |||||||

| <y15> | ОП МКК | ||||||||

| <y2> | <y16> | <y23> | ОП МКК | ||||||

| NX1 | УП МКК | ||||||||

| <y4> | <y17> | ОП МКК | |||||||

| <y18> | ОП МКК | ||||||||

| <y2> | <y19> | <y20> | ОП МКК | ||||||

| NX4 | УП МКК | ||||||||

| <y4> | <y21> | ОП МКК | |||||||

| NX5 | УП МКК | ||||||||

| NX6 | УП МКК | ||||||||

| <y9> | <y23> | <y24> | <y22> | <y25> | ОП МКК | ||||

| <y29> | ОП МКК | ||||||||

| УП МКК | |||||||||

| <y2> | <y3> | <y7> | ОП МКК | ||||||

| УП МКК | |||||||||

| <y2> | <y9> | <y10> | <y11> | <y22> | <y26> | ОП МКК | |||

| <y23> | <y27> | <y28> | ОП МКК | ||||||

| NX1 | УП МКК | ||||||||

| УП МКК | |||||||||

Рис. 11

Принципы работы автомата заключается в следующем. После занесения начального адреса и включение Тупр выбранная из памяти микрокоманда фиксируется на РМК. По значению R определяется тип МК. Если это операционная МК, то  - разрешает блоку формирования управляющих сигналов обрабатывать ОП МК и запрещает работу ДС NX и блока формирования адреса прихода. После выполнения текущей МК адрес следующей формируется на СЧАМК инкрементом.

- разрешает блоку формирования управляющих сигналов обрабатывать ОП МК и запрещает работу ДС NX и блока формирования адреса прихода. После выполнения текущей МК адрес следующей формируется на СЧАМК инкрементом.

Если R =1, то на РМК принята МК управления. В этом случае будет формироваться переход к следующей микрокоманде безусловно или по условию, т.е. при БП на СЧАМК заносится адрес перехода В, а при УП или В, если xi =1, или на СЧАМК формируется продвинутый адрес. В любом случае для перехода к следующей МК микропрограммы должны быть сформированы сигналы Z1 или Z2, которые формально описываются следующим образом:

,

,

где n = 6

После получения логических выражений для сигналов Z1 и Z2 для обоих типов МПА с программируемой логикой в соответствии с ГОСТ строятся электрические функциональные схемы.

2015-01-30

2015-01-30 1360

1360