Для многозадачных и многопользовательских операционных систем важна способность процессора к быстрому переключению выполняемых задач. Операция переключения задач процессора сохраняет состояние процессора и связь с предыдущей задачей, загружает состояние новой задачи и начинает ее выполнение. Состояние каждой задачи сохраняется в сегменте состояния задачи (TSS), который, как и любой другой сегмент, определяется дескриптором (см. рисунок 1.6).

Дескриптор TSS может быть расположен только в GDT. Ни в LDT, ни в IDT он не может быть расположен. При попытке обращения к TSS селектором сегмента с установленным флагом TI (который указывает на текущую LDT) генерируется исключение общей защиты #GP. Исключение общей защиты генерируется и в том случае, если производится попытка загрузки селектора TSS в сегментный регистр.

Флаг занятости (В) в поле типа говорит о том, занята задача, или нет. Занятой является выполняемая или приостановленная задача. Значение поля типа 1001b индицирует неактивную задачу, а 1011b – занятую. Задачи не являются рекурсивными.

Переключение задач выполняется по инструкции межсегментного перехода (JMP) или вызова (CALL), ссылающейся на сегмент состояния задачи (TSS) или дескриптор вентиля задачи в GDT или LDT. Переключение задач может происходить также по аппаратным и программным прерываниям и исключениям, если соответствующий элемент в IDT является дескриптором вентиля задачи. Дескриптор TSS указывает на сегмент, содержащий полное состояние процессора, а дескриптор вентиля задачи содержит селектор, указывающий на дескриптор TSS.

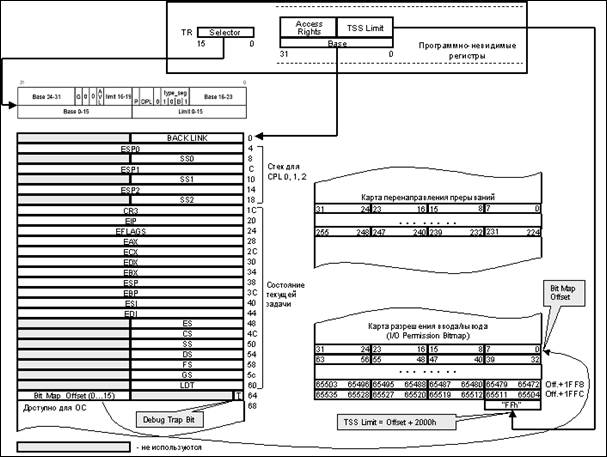

Каждая задача должна иметь связанный с ней TSS. 32-разрядные процессоры допускают и 16-битный формат TSS. Оба типа сегментов содержат образы регистров процессора, раздельные указатели стеков для уровней 0, 1 и 2, а также обратную ссылку на TSS вызвавшей задачи. Свободное поле TSS может использоваться по усмотрению операционной системы. TSS для процессоров 386+ содержит элементы, отсутствующие в TSS 80286: битовые карты разрешения ввода/вывода и перенаправления прерываний, а также бит отладочной ловушки Т (при Т= 1 переключение в данную задачу вызывает исключение отладки). Последним элементом TSS 386+ должен быть байт 0FFh. Значение поля лимита дескриптора для TSS 386+ должно превышать 0064h. Структура сегмента состояния задачи показана на рисунке 1.8.

Карта разрешения ввода/вывода (I/O Permission Bit Map), расположенная в конце TSS 386+, имеет по одному биту на каждый адрес портов ввода/вывода. Разрешению обращения соответствует нулевое значение бита. Максимальный размер таблицы (2000h), соответствующий всем 64 К адресам, может быть урезан лимитом TSS. Порты с адресами, не попавшими в усеченную таблицу, считаются недоступными.

Текущий TSS идентифицируется специальным регистром задачи TR (Task Register). Этот регистр содержит селектор, ссылающийся на дескриптор текущего TSS. Программно-невидимые регистры базового адреса и лимита, связанные TR, загружаются при загрузке в TR нового селектора.

Для возврата управления задаче, вызвавшей текущую задачу, или ей прерванной, используется инструкция IRET. В регистре флагов имеется флаг вложенной задачи NT (Nested Task), который управляет действием инструкции IRET. При NT = 0 IRET работает обычным образом, оставаясь в текущей задаче. При NT = 1 (текущая задача – вложенная) IRET выполняет переключение в предыдущую задачу.

Рисунок 1.8 – Структура сегмента состояния задачи

Когда инструкции CALL, JMP или INT выполняют переключение задач, старый (кроме случая JMP) и новый TSS помечаются занятыми (меняется значение Type в их дескрипторах), и в поле обратной ссылки в новом TSS устанавливается значение селектора старого TSS. Инструкции CALL и INT, переключающие задачи, устанавливают в новой задаче бит NT. Прерывание, не вызывающее переключение задач, сбросит бит NT. Этот бит может устанавливаться и сбрасываться инструкциями POPF и IRET.

Смена контекста сопроцессора при переключении задач автоматически не производится, так как новой задаче сопроцессор может и не понадобиться. Однако, если процессор обнаруживает первое использование сопроцессора после переключения задачи, он вырабатывает исключение #NM. Обработчик этого исключения сам определит, необходима ли смена контекста. Каждый раз при переключении задач процессор устанавливает бит TS (Task Switched) в MSW. Это указывает на то, что контекст процессора может относиться к другой задаче. При выполнении инструкций ESC или WAIT, если TS = 1 и MP = 1 (сопроцессор присутствует), вырабатывается исключение #NM (отсутствующий сопроцессор).

7 Лекция № 6. Страничное преобразование

Продолжительность: 2 часа (90 мин.)

2015-01-07

2015-01-07 520

520