ОЗУ – это наибольшая часть основной памяти. ОЗУ предназначено для хранения переменной (текущей, быстро изменяющейся) информации и допускает изменение своего содержимого в ходе выполнения процессором вычислений. Это означает, что процессор может выбрать (режим считывания) из ОЗУ команду или данные и после обработки поместить полученный результат (режим записи) в ОЗУ. Размещение новых данных возможно на тех же местах, где ранее находились исходные данные. Понятно, что прежние данные будут стерты. ОЗУ позволяет кратковременно (до выключения питания) хранить записанную информацию. Данные, адреса и команды, которыми процессор обменивается с памятью, часто называют операндами.

Выполняемая в данный момент компьютером программа (активная) чаще всего располагается в ОЗУ (и лишь иногда в ПЗУ).

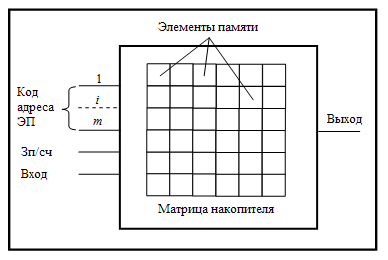

Основная составная часть ОЗУ – массив элементов памяти, объединенных в матрицу накопителя (рис. 9.1). Элемент памяти (ЭП) может хранить 1 бит информации (запоминать два состояния 0 или 1).

Рис. 9.1. Устройство ОЗУ

Каждый ЭП имеет свой адрес (по-другому можно сказать — порядковый номер). Для обращения к ЭП (с целью записи или считывания информации) его необходимо «выбрать» с помощью кода адреса. Оперативная память является электронной памятью, потому что она создается с помощью микросхем — изделий микроэлектроники.

Микросхемы памяти бывают одноразрядные и многоразрядные.

В одноразрядных микросхемах памяти код адреса (иногда говорят просто — адрес) выбирает один элемент памяти из множества элементов, расположенных в матрице накопителя. После выбора элемента в него можно записать информацию или, наоборот, считать из него 1 бит информации. Специальный управляющий сигнал Зп/сч (Write/Read) указывает микросхеме, что она должна делать: записывать или считывать информацию. Управляющие сигналы на этот вход поступают от процессора. В одноразрядных микросхемах памяти имеются один вход для записи информации и один выход для ее считывания.

Разрядность кода адреса m в одноразрядных микросхемах памяти определяет информационную емкость, т. е. число ЭП в матрице накопителя. Емкость такой микросхемы рассчитывается по формуле 2 m. Например, если у одноразрядной микросхемы памяти имеется 10 адресных входов, то информационная емкость составит N = 210 = 1024 бита.

Некоторые микросхемы памяти имеют многоразрядную структуру, называемую также словарной. У таких микросхем памяти имеется несколько информационных входов и столько же выходов. Поэтому они допускают одновременную запись (или считывание) многоразрядного кода, который принято называть словом. Один адрес позволяет считать информацию сразу из нескольких ЭП. Группа элементов памяти, из которых одновременно считывается информация, называется ячейкой памяти. Таким образом, ячейка памяти — это несколько ЭП, имеющих общий адрес.

На английском языке оперативная память называется Random Access Memory (RAM) — память с произвольным доступом. Термин «произвольный доступ» означает, что можно считать (записать) информацию в любой момент времени из любого (в любой) ЭП. Заметим, что существует и другая организация памяти, при которой, прежде чем считать нужную информацию, нужно «вытолкнуть» ранее поступившие операнды.

Используется два основных типа оперативной памяти: статическая (SRAM — Static RAM) и динамическая (DRAM — Dynamic RAM).

Эти две разновидности памяти различаются быстродействием и удельной плотностью (емкостью) хранимой информации. Быстродействие памяти характеризуется двумя параметрами: временем доступа (access time) и длительностью (cycle time).

Эти величины, как правило, измеряются в наносекундах. Чем меньше эти величины, тем выше быстродействие памяти.

Время доступа представляет собой промежуток времени между формированием запроса на чтение информации из памяти и моментом поступления из памяти запрошенного машинного слова (операнда).

Длительность цикла определяется минимальным допустимым временем между двумя последовательными обращениями к памяти.

В статической памяти элементы построены на триггерах – схемах с двумя устойчивыми состояниями. Для построения одного триггера требуется 4 – 6 транзисторов. После записи информации в статический элемент памяти он может хранить информацию сколь угодно долго (пока подается электрическое питание).

Конструктивно микросхема памяти выполняется в виде прямоугольной матрицы, причем ЭП располагаются на пересечении строк и столбцов. При обращении к микросхеме статической памяти на нее подается полный адрес, который разбивается на две части. Одна часть адреса используется для выбора строк матрицы накопителя, а другая – для выбора столбцов.

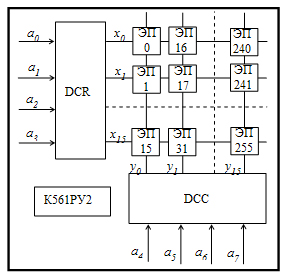

На рис. 9.2. приведена структурная схема микросхемы памяти К561РУ2, у которой 8 адресных входов: a 7 a 6, …, a 0. Это позволяет разместить в матрице 28 = 256 элементов памяти. Адресные входы разделены на две равные части (матрица квадратная). Младшая часть адреса a 3 a 2 a 1 a 0позволяет выбрать одну из 16 строк x 0, x 1, x 2, …, x 15. При помощи старшей части адреса a 7 a 6 a 5 a 4 происходит выбор одного из 16 столбцов y 0, y 1, …, y 15.

Рис. 9.2. Структурная схема микросхемы памяти К561РУ2

Чтобы выбрать какой-либо ЭП, нужно активизировать строку и столбец, на пересечении которых располагается нужный ЭП.

Например, чтобы выбрать ЭП 0, нужно на все адресные входы микросхемы подать нули, тогда дешифратор строк DCR (Decoder Row) и дешифратор столбцов DCC (Decoder Column) активизируют соответственно строку x0 и столбец y0. На их пересечении располагается ЭП 0, в который, после его выбора, можно записать (или считать) информацию.

Аналогично выбираются другие ЭП. Так, для выбора ЭП 241 нужно активизировать строку x 1 и столбец y 15. Для этого на младшую группу адресов (a 3, …, a 0) нужно подать двоичный код 0001, а на старшую группу адресов (a 7, …, a 4) – все единицы.

Статическая память имеет высокое быстродействие и низкую удельную плотность размещения хранящихся данных. В динамической памяти ЭП построены на основе полупроводниковых конденсаторов, занимающих гораздо меньшую площадь, чем триггеры в статических ЭП. Для построения динамического элемента памяти требуется всего 1–2 транзистора.

Подключение и отключение конденсаторов в динамических ЭП осуществляется с помощью полупроводниковых транзисторов (ключей), которые в закрытом состоянии имеют сопротивление порядка 1010 Ом. Несмотря на то, что сопротивление закрытого транзистора велико, оно все же конечно, и по этой причине через закрытый транзистор происходит разряд конденсатора. Самопроизвольный разряд конденсатора не позволяет без специальных мер долгое время хранить записанную информацию. Для устранения влияния нежелательного разряда конденсатора через так называемые паразитные цепи утечки приходится периодически подзаряжать конденсаторы. Этот процесс называется регенерацией заряда.

Регенерация заряда должна происходить достаточно часто. Подтверждением этого являются следующие рассуждения. Так как необходимо получить высокую удельную плотность хранения информации, емкость конденсатора не может быть большой (практически величина емкости запоминающих конденсаторов составляет порядка 0,1 пФ). Постоянная времени разряда определяется как произведение емкости конденсатора на сопротивление закрытого транзистора. Это произведение составляет величину порядка

τ = RC = 1010· 0,1 · 10-12 = 10-3 c.

Таким образом, постоянная времени разряда составляет 1 мс и, значит, регенерация заряда должна происходить примерно 1000 раз в 1 с.

Необходимость частой подзарядки запоминающих конденсаторов в матрице накопителя приводит к снижению быстродействия динамической памяти. Однако благодаря малым размерам конденсатора и малому числу дополнительных элементов удельная плотность хранения информации динамической памяти выше, чем у статической памяти.

Емкость микросхем динамической памяти составляет десятки мегабит на один корпус. Возможность размещения на одном кристалле большого числа ЭП вызывает другую конструкторскую проблему: необходимо использовать большое число адресных входов. Для снижения остроты этой проблемы используют мультиплексирование.

Мультиплексирование — это технический прием временного уплотнения информации, благодаря которому удается по одним и тем же электрическим цепям передать разную информацию для различных приемников (потребителей) информации. Так, конструкторы вдвое уменьшают число адресных входов у микросхем памяти. Адрес делят на две равные части и вводят его в микросхему поочередно: сначала младшую часть, а затем старшую часть адреса. При этом первая часть осуществляет выбор нужной строки в матрице накопителя, а вторая часть активизирует соответствующий столбец.

Для того чтобы микросхема памяти «знала», какая часть адреса вводится в данный момент времени, ввод каждой группы адреса сопровождается соответствующим управляющим сигналом.

Так, синхронно с вводом младшей части адреса на микросхему подается сигнал RAS (Row Address Strobe) – сигнал стробирования (сопровождения) адреса строки. Практически одновременно с вводом старшей части адреса на микросхему памяти подается сигнал CAS (Column Address Strobe) – стробирование адреса столбца.

После завершения выбора какого-либо ЭП требуется время, в течение которого происходит восстановление микросхемы в исходное состояние. Данная задержка связана с необходимостью перезарядки внутренних цепей микросхемы. Длительность этой задержки существенна и составляет до 90% от времени цикла.

Обходят это нежелательное явление различными конструктивными ухищрениями. Например, при записи нескольких следующих друг за другом операндов их располагают на одной строке матрицы, но в разных столбцах. Экономия времени достигается тем, что не нужно ожидать завершения переходных процессов при смене адреса строк.

Другой способ повышения быстродействия заключается в том, что память разбивают на блоки (банки), из которых процессор считывает данные попеременно. Таким образом, пока считываются данные из одной области памяти, другая получает время на завершение переходных процессов.

Разработаны различные модификации статической и динамической памяти.

FPM DRAM (Fast Page Mode DRAM) – динамическая память с быстрым странич-ным доступом. Память со страничным доступом отличается от обычной динамической памяти тем, что после выбора одной строки матрицы удерживается сигнал выбора строки RAS и производится многократное изменение адресов столбцов (с помощью сигнала CAS). В этом случае не тратится время на завершение переходных процессов при изменении адреса строки. Другими словами, адрес строки остается некоторое время постоянным, а изменяются адреса столбцов. В этом случае страницей называют элементы памяти, расположенные на одной строке матрицы.

EDO (Extended Data Out) – эти микросхемы характеризуются увеличенным временем удержания данных на выходе. Фактически представляют собой обычную память FPM DRAM, на выходе которой установлены регистры – защелки данных. Регистры – это цифровые устройства, построенные на триггерах и позволяющие хранить сразу несколько бит информации (слово). При страничном обмене такие микросхемы удерживают на выходах микросхемы содержимое последней выбранной ячейки памяти, в то время как на их входы уже подается адрес следующей выбираемой ячейки памяти. Это позволяет примерно на 15% по сравнению с FРM ускорить процесс считывания последовательно расположенных массивов данных.

SDRAM (Synchronous DRAM – синхронная динамическая память) – память с синхронным доступом, работающая быстрее обычной асинхронной памяти. Основу этого типа памяти составляет традиционная схема DRAM. Однако SDRAM отличается тем, что использует тактовый генератор для синхронизации всех сигналов, применяемых в микросхеме памяти. Помимо синхронного метода доступа, SDRAM использует внутреннее разделение массива памяти на два независимых банка, что позволяет совмещать по времени выборку из одного банка с установкой адреса в другом банке.

2015-02-24

2015-02-24 2203

2203