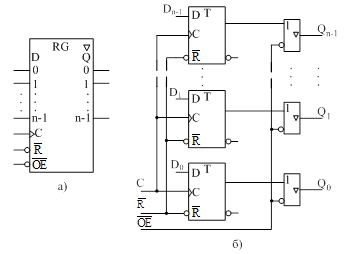

В параллельных регистрах схемы разрядов не обмениваются данными между собой. Общими для разрядов обычно являются цепи синхронизации (тактирования), сброса/установки, разрешения приема или выдачи, т.е. цепи управления. В современной цифровой схемотехнике регистры обычно строят на D-триггерах с прямым динамическим входом синхронизации, которые обеспечивают простоту схемы и высокое быстродействие. Пример схемы параллельного регистра, построенного на таких триггерах, имеющего входы сброса  и выходы с третьим состоянием, управляемые сигналом

и выходы с третьим состоянием, управляемые сигналом  , показан на рисунке 21. УГО регистра представляет собой прямоугольник с аббревиатурой RG (от англ. Register) во внутреннем поле (рисунок 21, а).

, показан на рисунке 21. УГО регистра представляет собой прямоугольник с аббревиатурой RG (от англ. Register) во внутреннем поле (рисунок 21, а).

Рисунок 21 – Параллельный регистр на D-триггерах с прямым динамическим входом синхронизации. Условное графическое обозначение (а) и логическая схема (б)

Для сброса регистра в исходное нулевое состояние на вход сброса  (рисунок 21) следует подать нулевой сигнал. Кодовое слово, подлежащее записи в регистр, подается одновременно всеми разрядами на информационные входы Dn-1...D0. Запись входного слова происходит по положительному фронту сигнала синхронизации на входе C. При единичном значении сигнала на входе разрешения

(рисунок 21) следует подать нулевой сигнал. Кодовое слово, подлежащее записи в регистр, подается одновременно всеми разрядами на информационные входы Dn-1...D0. Запись входного слова происходит по положительному фронту сигнала синхронизации на входе C. При единичном значении сигнала на входе разрешения  регистр работает в режиме хранения. Для выдачи кодового слова на параллельные выходы Qn-1…Q0 подается нулевой сигнал на вход разрешения OE.

регистр работает в режиме хранения. Для выдачи кодового слова на параллельные выходы Qn-1…Q0 подается нулевой сигнал на вход разрешения OE.

Некоторые параллельные регистры относятся к числу буферных, т.е. рассчитаны на работу с большими емкостными и/или низкоомными активными нагрузками. Это обеспечивает их работу непосредственно на шину (магистраль) без дополнительных схем интерфейса.

2015-02-27

2015-02-27 1232

1232