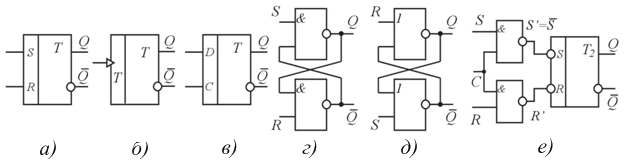

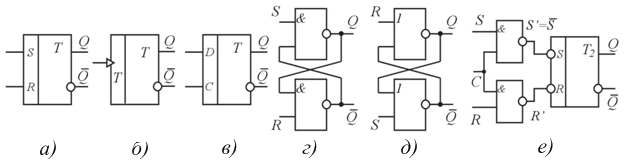

По способу записи информации триггеры могут быть несинхронизируемыми (асинхронный) и синхронизируемыми (синхронными). Синхронизируемые триггеры имеют импульсный вход C, на который поступает синхронизирующий (тактирующий) сигнал, разрешающий триггеру принять новую информацию (вызывающий срабатывание триггера).

По способу логического функционирования триггеры разделяют на следующие типы: RS – триггеры с раздельным запуском (триггеры с установочными входами); Т – триггеры со счетным входом; Д – триггеры с поступлением информации по одному входу (триггеры задержки); универсальные.

Рисунок 90 Рисунок 90 |

Рисунок 91 Рисунок 91 |

– прямой выход,

– прямой выход,  – инверсный выход.

– инверсный выход. RS – триггер – наиболее простой (рисунок 91), содержит минимальное количество логических элементов два элемента И–НЕ или ИЛИ–НЕ.

Синхронный RS – триггер имеет дополнительный тактовый вход (рисунок 82).

Т – триггер.

Счетный (рисунок 92)

Рисунок 92 Рисунок 92 |

Д – триггер.

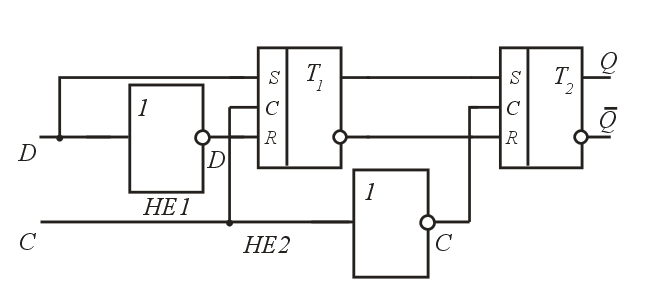

Запись информации происходит в момент поступления синхронизирующего импульса, а ее использование возможно при поступлении следующего синхронизирующего импульса, т.е. с задержкой на такт (рисунок 93).

Рисунок 93 Рисунок 93 |

Так как Д – триггер запоминает сигнал на входе и хранит до следующего тактового импульса, поэтому Д – триггеры являются элементами памяти.

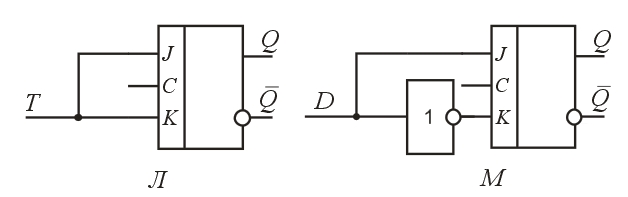

Универсальный JК – триггер. Синхронный имеет тактовый вход (рисунок 94). Наиболее сложный и не имеет неопределенных состояний. Роль входа S и R играют соответственно J и К. При этом роль S и R входов играют соответственно J и К. Отличительной особенностью JК – триггера является переход в режим Т – триггера при  , т.е. при объединении входов.

, т.е. при объединении входов.

Рисунок 94 Рисунок 94 |

Для реализации Д – триггера объединяют вход К через инвертор с входом J.

2015-02-14

2015-02-14 869

869