Павлов Г.В., Обрубов А.В., Щербинін Т.В. Розрахунок цифрових систем управління імпульсних перетворювачів постійної напруги. Миколаїв: НУК, 2011 - 96 с.

Навчальний посібник містить теоретичні відомості, необхідні для розробки імпульсних перетворювачів постійної напруги із цифровими системами управління та приклади інженерних розрахунків перетворювачів. Зокрема, розглянуто принцип дії та перебіг електромагнітних процесів в силовій частині понижуючого, підвищуючого та полярно-інвертуючого імпульсних перетворювачів постійної напруги, структуру та можливі варіанти побудови систем управління даними типами перетворювачів. Наведено приклади розрахунків силової частини та системи управління. Розглянуто питання стійкості систем управління перетворювачів та синтезу ПІД-регуляторів, які забезпечують високі показники якості керування перетворювачами..

Навчальний посібник призначений для допомоги студентам, що навчаються за напрямами 6.050702 “Електромеханіка” та 6.050201 “Системна інженерія” всіх форм навчання під час виконання курсових робіт з курсу “Електроніка і мікросхемотехніка”.

Рецензенти: В.С. Блінцов, д.т.н., проф. А.К. Жук, к.т.н., доц.

ВСТУП

Імпульсні перетворювачі постійної напруги широко застосовуються в якості блоків живлення радіоелектронних пристроїв, обчислювальної техніки, джерел освітлення, як регулятори напруги в електроприводах постійного струму.

Проектування систем управління сучасними імпульсними перетворювачами постійної напруги – комплексна задача, яка потребує від розробника теоретичних знань із трьох розділів курсу “Електроніка і мікросхемотехніка” – аналогової, цифрової та силової електроніки. Закріплення цих знань є метою курсового проекту з дисципліни “Електроніка і мікросхемотехніка”.

Виконання даного курсового проекту є заключним етапом вивчення курсу “Електроніка і мікросхемотехніка”. Цей етап підготовляє студента до самостійної діяльності у проектуванні електронних систем, зокрема, імпульсних перетворювачів постійної напруги. Набуті ним знання принципів побудови мікропроцесорних систем управління можуть бути застосовані при розв’язанні аналогічних задач, зокрема – під час дипломного проектування.

Навчальний посібник, а також довідкова інформація, що міститься у літературних джерелах, наведених у кінці, дають теоретичну базу для ознайомлення студентів з принципами побудови, реалізації і функціонування цифрових систем управління сучасними імпульсними перетворювачами постійної напруги.

1. ТЕОРЕТИЧНІ ВІДОМОСТІ ПРО ІМПУЛЬСНІ ПЕРЕТВОРЮВАЧІ ПОСТІЙНОЇ НАПРУГИ

1.1. Принцип дії і характеристики імпульсних перетворювачів постійної напруги

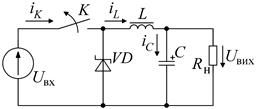

Принцип дії імпульсних перетворювачів постійної напруги (ППН) полягає в періодичному підключенні та відключенні (комутації) кола навантаження до первинного джерела електроенергії з напругою  . В результаті виникають регульовані імпульси напруги прямокутної форми, які згладжуються фільтруючими індуктивностями і емностями. Середня напруга імпульсів виділяється на навантаженні. Комутація здійснюється за допомогою електронних силових ключів – транзисторів, діодів, тиристорів. На рис. 1.1 зображені ключові схеми силових контурів ППН понижуючого (а) та підвищуючого (б) типа. В схемі на рис. 1.1, а струм буде протікати від джерела живлення до навантаження коли ключ К замкнено. Напруга на навантаженні

. В результаті виникають регульовані імпульси напруги прямокутної форми, які згладжуються фільтруючими індуктивностями і емностями. Середня напруга імпульсів виділяється на навантаженні. Комутація здійснюється за допомогою електронних силових ключів – транзисторів, діодів, тиристорів. На рис. 1.1 зображені ключові схеми силових контурів ППН понижуючого (а) та підвищуючого (б) типа. В схемі на рис. 1.1, а струм буде протікати від джерела живлення до навантаження коли ключ К замкнено. Напруга на навантаженні  дорівнюватиме різниці напруги

дорівнюватиме різниці напруги  та падінь напруги на елементах контуру. Якщо періодично розмикати ключ К, середнє значення напруги

та падінь напруги на елементах контуру. Якщо періодично розмикати ключ К, середнє значення напруги  буде тим менше, чим довше розімкнений ключ К. В такому перетворювачі напруга

буде тим менше, чим довше розімкнений ключ К. В такому перетворювачі напруга  завжди менша за

завжди менша за

|  |

| а | б |

| Рис.1.1. Ключові схеми силових контурів ППН |

В схемі на рис. 1.1, б струм буде протікати від джерела до навантаження в проміжках часу коли ключ К розімкнено. Коли ключ замкнено, струм буде протікати лише через індуктивність L. В індуктивності буде накопичуватись енергія. Коли ключ К знову буде розімкнено, індуктивність L віддасть накопичену енергію до джерела, відіграючи роль ще одного джерела ЕРС, підключеного послідовно з джерелом ЕРС  . Напруга

. Напруга  буде становити різницю між сумою

буде становити різницю між сумою  та падіннями напруги на елементах контуру. В цьому перетворювачі вихідна напруга може бути більшою за вхідну. Напівпровідниковий діод VD в обох випадках спрямовує протікання струму у потрібному напрямку.

та падіннями напруги на елементах контуру. В цьому перетворювачі вихідна напруга може бути більшою за вхідну. Напівпровідниковий діод VD в обох випадках спрямовує протікання струму у потрібному напрямку.

Дані два види контурів являються базовими. Шляхом їх комбінацій можливо побудувати ППН із необхідними властивостями.

Частота замикань та розмикань ключа К, яка називається частотою комутації, або частотою перетворення  , знаходиться в межах від одиниць до десятків-сотень кГц (тиристори та біполярні транзистори), або до одиниць МГц (МОП-транзистори). Період перетворення

, знаходиться в межах від одиниць до десятків-сотень кГц (тиристори та біполярні транзистори), або до одиниць МГц (МОП-транзистори). Період перетворення  складається з відрізків часу, коли силовий ключ замкнено та часу розімкненого стану цього ключа, тобто

складається з відрізків часу, коли силовий ключ замкнено та часу розімкненого стану цього ключа, тобто  . Час замкненого стану зручно задавати за допомогою відносної тривалості імпульсу

. Час замкненого стану зручно задавати за допомогою відносної тривалості імпульсу  :

:  . Коефіцієнт

. Коефіцієнт  також називають коефіцієнтом заповнення імпульсу. За допомогою зміни відносної тривалості можна регулювати або стабілізувати вихідну напругу ППН. Такий спосіб регулювання напруги при постійній частоті проходження імпульсів називається широтно-імпульсною модуляцією (ШІМ). Імпульси напруги в схемі ППН мають, головним чином, прямокутну форму, а імпульси струму – трикутну.

також називають коефіцієнтом заповнення імпульсу. За допомогою зміни відносної тривалості можна регулювати або стабілізувати вихідну напругу ППН. Такий спосіб регулювання напруги при постійній частоті проходження імпульсів називається широтно-імпульсною модуляцією (ШІМ). Імпульси напруги в схемі ППН мають, головним чином, прямокутну форму, а імпульси струму – трикутну.

Основні переваги ППН у порівнянні з лінійними стабілізаторами, в яких транзистор працює в підсилювальному, а не ключовому режимі, – більший коефіцієнт корисної дії (ККД), менші маса та габарити. До недоліків можна віднести наявність пульсацій та додаткових завад, що зумовлено імпульсним регулюванням, гірші динамічні характеристики та відносна складність. Однак у багатьох випадках застосування ППН є найбільш раціональним технічним рішенням.

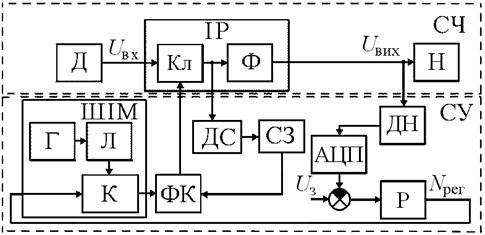

Структурна схема ППН показана на рис. 1.2. До неї входять: імпульсний регулятор ІР, через який енергія передається від джерела Д до навантаження Н; дільник напруги ДН; аналого-цифровий перетворювач АЦП; датчик струму ДС; схема струмового захисту СЗ; регулятор Р; широтно-імпульсний модулятор ШІМ; формуючий каскад ФК.

|

| Рис.1.2. Блок-схема ППН |

ІР містить силові ключі Кл та фільтруючі реактивні елементи Ф. ШІМ складається з генератора тактуючих імпульсів Г, лічильника імпульсів Л та компаратора К. Електричні кола, що містять елементи ІР і з'єднують джерело Д з навантаженням Н, утворюють силову частину СЧ ППН. Схема управління СУ формує сигнал управління силовими ключами таким чином, щоб стабілізувати вихідну напругу. Для цього відстежується фактичне значення  та порівнюється з бажаною вихідною напругою

та порівнюється з бажаною вихідною напругою  . Окрім цього СУ виконує функцію струмового захисту. СУ містить ДН, АЦП, Р, ДС, СЗ, ШІМ і ФК.

. Окрім цього СУ виконує функцію струмового захисту. СУ містить ДН, АЦП, Р, ДС, СЗ, ШІМ і ФК.

Сигнал на виході ДН, що пропорційний напрузі на навантаженні, потрапляє до АЦП, де перетворюється на двійковий код. Отримане значення порівнюється із значенням  . Різниця між

. Різниця між  і

і  опрацьовується в Р за обраним законом керування. Найчастіше застосовується пропорційно-інтегрально-диференційний закон

опрацьовується в Р за обраним законом керування. Найчастіше застосовується пропорційно-інтегрально-диференційний закон  , де

, де  =

=

,

,  - поточне значення коефіцієнта

- поточне значення коефіцієнта  в двійковому коді. Отримане значення

в двійковому коді. Отримане значення  подається на ШІМ. На виході ШІМ утворюються прямокутні імпульси, відносна тривалість яких відповідає коефіцієнту

подається на ШІМ. На виході ШІМ утворюються прямокутні імпульси, відносна тривалість яких відповідає коефіцієнту  . Модульовані за шириною імпульси надходять на ФК, який відповідно до них створює необхідний сигнал управління силовими ключами. Силові ключі Кл періодично підключають з частотою перетворення джерело Д до елементів Ф, відбираючи енергію від нього визначеними “порціями”. Завдяки згладжувальної дії Ф до навантаження Н енергія надходить рівномірно. Якщо струм силового ключа перевищує визначене значення, СЗ формує сигнал заборони включення, який “зрізає” частину імпульсу, що надходить від ШІМ.

. Модульовані за шириною імпульси надходять на ФК, який відповідно до них створює необхідний сигнал управління силовими ключами. Силові ключі Кл періодично підключають з частотою перетворення джерело Д до елементів Ф, відбираючи енергію від нього визначеними “порціями”. Завдяки згладжувальної дії Ф до навантаження Н енергія надходить рівномірно. Якщо струм силового ключа перевищує визначене значення, СЗ формує сигнал заборони включення, який “зрізає” частину імпульсу, що надходить від ШІМ.

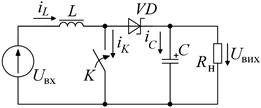

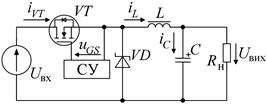

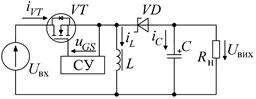

Три основні варіанти (топології) силових схем ППН [2,7,8,9,11], у котрих використовується один керований ключ – МОП-транзистор, показані на рис. 1.3,а,б,в.

|  |

| а | б |

| |

| в | |

| Рис.1.3. Топології силових схем ППН |

Класифікуються вони як понижуючий (англ. Buck Converter), підвищуючий (англ. Boost Converter) та полярно-інвертуючий (англ. Buck-Boost Converter) ППН. У понижуючому ППН, який відповідає ключовій схемі на рис. 1.1, а, вихідна напруга завжди менше за вхідну. Коли транзистор VT відкрито черговим імпульсом напруги затвор-виток (gate-source)  тривалістю

тривалістю  (рис.1.4,а), енергія від джерела

(рис.1.4,а), енергія від джерела  надходить до навантаження

надходить до навантаження  і накопичується в дроселі

і накопичується в дроселі  та конденсаторі

та конденсаторі  фільтра. Спадання напруги виток-стік (source-drain) на транзисторі

фільтра. Спадання напруги виток-стік (source-drain) на транзисторі  (

( ) при цьому невелике, порядку 1В, та відповідає напрузі насичення

) при цьому невелике, порядку 1В, та відповідає напрузі насичення  транзистора. До діода

транзистора. До діода  прикладено зворотню напругу

прикладено зворотню напругу  , що близька за величиною до вхідної. Струм дроселя

, що близька за величиною до вхідної. Струм дроселя  наростає за експоненціальним законом від мінімального

наростає за експоненціальним законом від мінімального  до максимального

до максимального  значень.

значень.

|  |

| а | Б |

| Рис. 1.4. Електромагнітні процеси в силовій частині ППН |

Таким же чином міняється й струм транзистора  . По закінченні відкриваючого імпульсу

. По закінченні відкриваючого імпульсу  транзистор

транзистор  закривається, відключаючи дросель від джерела вхідної напруги. Струм через нього спадає. Як тільки струм дроселя починає зменшуватися, напругою його самоіндукції відкривається діод

закривається, відключаючи дросель від джерела вхідної напруги. Струм через нього спадає. Як тільки струм дроселя починає зменшуватися, напругою його самоіндукції відкривається діод  . В цей час дросель виявляється підключеним паралельно навантаженню і фільтруючої ємності. Контур струму замикається скрізь діод. Струм дроселя зменшується за експоненциальним законом від максимального до мінімального значень. Протягом даного проміжку часу

. В цей час дросель виявляється підключеним паралельно навантаженню і фільтруючої ємності. Контур струму замикається скрізь діод. Струм дроселя зменшується за експоненциальним законом від максимального до мінімального значень. Протягом даного проміжку часу  струм діода

струм діода  є струмом дроселя. Далі, після закінчення паузи

є струмом дроселя. Далі, після закінчення паузи  , транзистор знову відкривається і процеси повторюються. Струм дроселя при цьому має постійну (

, транзистор знову відкривається і процеси повторюються. Струм дроселя при цьому має постійну ( ) та змінну

) та змінну  складові. Практично, уся змінна складова цього струму проходить через конденсатор

складові. Практично, уся змінна складова цього струму проходить через конденсатор  (струм

(струм  на рис. 1.4,а). Постійна складова замикається крізь навантаження. Дросель у даній схемі увесь період фільтрує вихідну напругу. Тому понижуюча схема забезпечує принципово менші пульсації вихідної напруги в порівнянні з підвищуючою та інвертуючою. Схема, у якій дросель під час накопичення енергії підключається паралельно джерелу

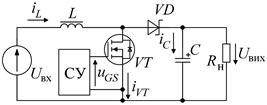

на рис. 1.4,а). Постійна складова замикається крізь навантаження. Дросель у даній схемі увесь період фільтрує вихідну напругу. Тому понижуюча схема забезпечує принципово менші пульсації вихідної напруги в порівнянні з підвищуючою та інвертуючою. Схема, у якій дросель під час накопичення енергії підключається паралельно джерелу  , може бути як підвищуючою, так і полярно-інвертуючою, в залежності від підключення навантаження і конденсатора фільтра (див. рис. 1.3,б,в). Вихідна напруга підвищуючої схеми, що базується на ключовій схемі рис. 1.1, б, як правило, більше за вхідну. У полярно-інвертуючому ППН, який поєднує властивості ключових схем рис. 1.1, а,б, вихідна напруга в залежності від навантаження і відносної тривалості імпульсу

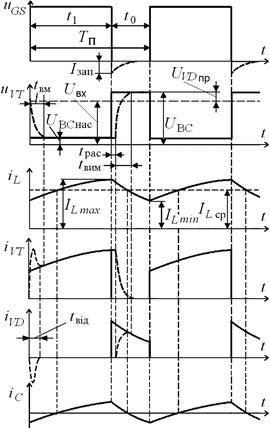

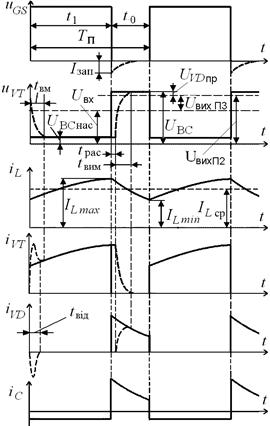

, може бути як підвищуючою, так і полярно-інвертуючою, в залежності від підключення навантаження і конденсатора фільтра (див. рис. 1.3,б,в). Вихідна напруга підвищуючої схеми, що базується на ключовій схемі рис. 1.1, б, як правило, більше за вхідну. У полярно-інвертуючому ППН, який поєднує властивості ключових схем рис. 1.1, а,б, вихідна напруга в залежності від навантаження і відносної тривалості імпульсу  може бути за величиною як більше, так і менше за вхідну. Часові діаграми для обох схем приведено на рис. 1.4,б. При відкриванні транзистора

може бути за величиною як більше, так і менше за вхідну. Часові діаграми для обох схем приведено на рис. 1.4,б. При відкриванні транзистора  імпульсом напруги

імпульсом напруги  дросель

дросель  підключається до напруги

підключається до напруги  . Діод

. Діод  закрито зворотньою напругою. Струм навантаження протікає крізь накопичувальний конденсатор

закрито зворотньою напругою. Струм навантаження протікає крізь накопичувальний конденсатор  . Струм дроселя

. Струм дроселя  збільшується за експоненціальним законом і енергія від первинного джерела

збільшується за експоненціальним законом і енергія від первинного джерела  надходить до дроселя. Коли транзистор закривається і струм

надходить до дроселя. Коли транзистор закривається і струм  через нього різко знижується, напругою самоіндукції дроселя відкривається діод

через нього різко знижується, напругою самоіндукції дроселя відкривається діод  . Енергія, що накопичена в дроселі, передається до накопичувального конденсатора та навантаження. У підвищуючому ППН при закритому транзисторі і відкритому діоді дросель підключається до навантаження послідовно з джерелом

. Енергія, що накопичена в дроселі, передається до накопичувального конденсатора та навантаження. У підвищуючому ППН при закритому транзисторі і відкритому діоді дросель підключається до навантаження послідовно з джерелом  . Тому енергія від джерела відбирається увесь час (при безперервному струмі дроселя). Пульсації вхідного струму даної схеми найменші. Безперервний струм дроселя має місце, коли при закритому транзисторі протягом часу

. Тому енергія від джерела відбирається увесь час (при безперервному струмі дроселя). Пульсації вхідного струму даної схеми найменші. Безперервний струм дроселя має місце, коли при закритому транзисторі протягом часу  струм

струм  не встигає знизитися до нуля, як показано на рис. 1.4,б. При невеликій індуктивності дроселя або малому струмі навантаження струм

не встигає знизитися до нуля, як показано на рис. 1.4,б. При невеликій індуктивності дроселя або малому струмі навантаження струм  стає переривчастим. ППН при цьому працездатний, однак такий режим небажаний через підвищені пульсації вихідної напруги. При однакових струмах навантаження та інших рівних умовах вихідна напруга підвищуючої схеми більше за вихідну напругу інвертуючої схеми на величину

стає переривчастим. ППН при цьому працездатний, однак такий режим небажаний через підвищені пульсації вихідної напруги. При однакових струмах навантаження та інших рівних умовах вихідна напруга підвищуючої схеми більше за вихідну напругу інвертуючої схеми на величину  . У фільтрації вихідної напруги в обох схемах бере участь тільки конденсатор

. У фільтрації вихідної напруги в обох схемах бере участь тільки конденсатор  , через який проходять великі імпульси струму, що рівні струму навантаження (рис.1.4,б). Пульсації вихідної напруги через це більше, ніж у понижуючої схемі.

, через який проходять великі імпульси струму, що рівні струму навантаження (рис.1.4,б). Пульсації вихідної напруги через це більше, ніж у понижуючої схемі.

Статичні характеристики ППН для безперервних струмів дроселя задаються у вигляді [8,9]

, (1.1)

, (1.1)

де  - відносна тривалість імпульсу;

- відносна тривалість імпульсу;  - відносна величина опору втрат;

- відносна величина опору втрат;  ;

;  - динамічний опір відкритих напівпровідникових ключів,

- динамічний опір відкритих напівпровідникових ключів,  - активний опір у колі дроселя. Функція (1.1) для трьох типів ППН має вигляд:

- активний опір у колі дроселя. Функція (1.1) для трьох типів ППН має вигляд:

- для понижуючого  ;

;

- для підвищуючого  ;

;

- для інвертуючого  .

.

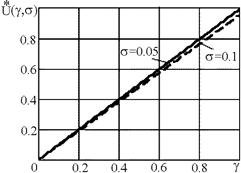

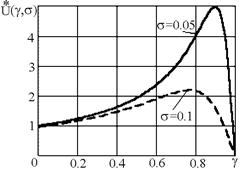

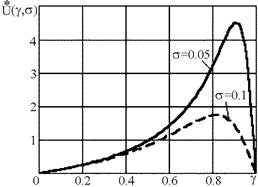

На рис. 1.5,а,б,в наведено регулювальні характеристики трьох типів перетворювачів ( ,

,  ,

,  ) для двох значень втрат

) для двох значень втрат  (безперервна лінія) і

(безперервна лінія) і  (пунктирна лінія).

(пунктирна лінія).

|  |

| а | б |

| |

| в | |

| Рис. 1.5. Регулювальні характеристики ППН |

Регулювальна характеристика понижуючого ППН лінійна і слабко залежить від втрат  у колі. У підвищуючого та інвертуючого ППН спостерігається залежність вихідної напруги від відносних втрат, особливо при максимумі. Якщо втрати спрямувати до нуля, максимальна напруга буде прагнути до нескінченності. Характеристики підвищуючого та інвертуючого ППН нелінійні. Існує межа

у колі. У підвищуючого та інвертуючого ППН спостерігається залежність вихідної напруги від відносних втрат, особливо при максимумі. Якщо втрати спрямувати до нуля, максимальна напруга буде прагнути до нескінченності. Характеристики підвищуючого та інвертуючого ППН нелінійні. Існує межа  , до якої характеристики зростають. Тому для роботи використовується діапазон

, до якої характеристики зростають. Тому для роботи використовується діапазон  .

.

Прохідні характеристики  лінійні. При заданих

лінійні. При заданих  і

і  визначаються коефіцієнтом передачі ППН

визначаються коефіцієнтом передачі ППН  . Зовнішні характеристики можна одержати, якщо покласти

. Зовнішні характеристики можна одержати, якщо покласти  та

та  і змінювати опір навантаження

і змінювати опір навантаження  .

.

1.2. Особливості цифрової системи управління імпульсним перетворювачем постійної напруги

Принцип дії системи управління імпульсним перетворювачем постійної напруги (СУ ППН) був коротко описаний вище (рис. 1.2). Він залишається майже незмінним за аналогової та цифрової реалізації системи управління. Однак цифрова СУ має певні особливості, які зумовлюють її переваги над аналоговими системами:

1. Точність. У ЦСУ сигнали представлені числами кінцевої розрядності, але точність може бути збільшена за рахунок збільшення кількості розрядів.

2. Погрішності обробки. Обробка аналогових сигналів виконується з використанням таких елементів, як резистори, конденсатори та транзистори в підсилювальному режимі, дійсні властивості яких можуть значно відрізнятися від заявлених (розрахункових). Обробка цифрових сигналів здійснюється за допомогою логічних схем, в яких транзистори працюють в ключовому режимі. Сигнали можуть приймати лише два значення – логічної одиниці (+3.3…+5В) та логічного нуля (0В).

3. Гнучкість. Важко перепроектувати реалізований апаратно аналоговий регулятор. Алгоритм функціонування цифрової системи управління може бути легко змінений.

4. Побудова складних систем. ЦСУ можуть мати складну структуру й функціонувати за розгалуженими алгоритмами, що тяжко реалізувати за допомогою аналогових елементів.

5. Мікропроцесорні системи можуть бути підключені до комп'ютерної мережі, що дозволить вносити зміни й контролювати поточний стан системи з віддаленого термінала.

Основними недоліками ЦСУ є дискретність по рівню, а також відслідковування керованої величини (у випадку ЦСУ ППН – вихідної напруги) лише в певні моменти часу, інтервал між якими залежить від швидкодії АЦП. З огляду на це бажано робити схему струмового захисту аналоговою, незалежною від мікропроцесора. Також необхідно підсилити сигнал ШІМ до величини, достатньої для відкриття силового ключа Кл. Цю задачу вирішує аналоговий формуючий каскад (ФК).

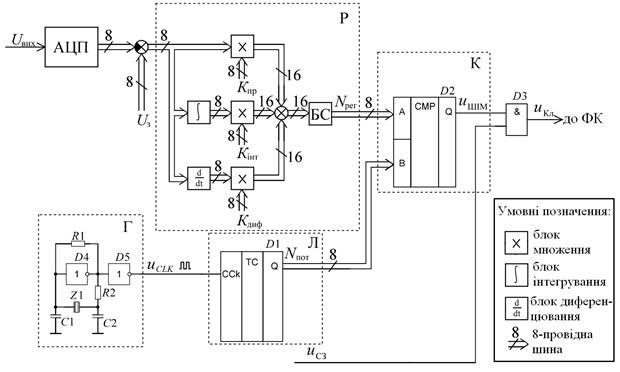

Структура цифрової частини СУ ППН наведено на рис. 1.6. Блоки, обведені пунктирною лінією, відповідають функціональним блокам на рис. 1.2.

|

| Рис. 1.6. Структурна схема цифрової частини СУ ППН |

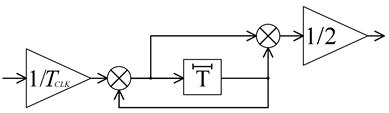

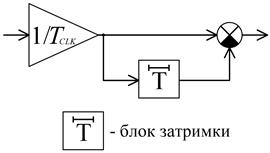

Блоки інтегрування та диференціювання виконуються на основі блоків затримки та суматорів, як показано на рис. 1.7 а та б відповідно. Алгоритмічна реалізація цих блоків описана у розділі 1.4.

|

| А |

|

| Б |

| Рис. 1.7. Цифрова реалізація блоків інтегрування та диференціювання |

Кварцовий генератор Г генерує імпульси прямокутної форми із частотою  , де

, де  в загальному випадку – максимальне число двійкового лічильника Л (D 1). У випадку 8-розрядного лічильника

в загальному випадку – максимальне число двійкового лічильника Л (D 1). У випадку 8-розрядного лічильника  . Період перетворення при цьому дорівнює

. Період перетворення при цьому дорівнює  . Аналоговий сигнал, пропорційний значенню вихідної напруги

. Аналоговий сигнал, пропорційний значенню вихідної напруги  , подається на АЦП, який перетворює його на двійковє число (на рис. 1.6 – 8-розрядний код). Це число надходить до обчислювального пристрою, в якому воно віднімається від значення бажаної вихідної напруги

, подається на АЦП, який перетворює його на двійковє число (на рис. 1.6 – 8-розрядний код). Це число надходить до обчислювального пристрою, в якому воно віднімається від значення бажаної вихідної напруги  . Отримана різниця

. Отримана різниця  надходить до регулятора Р, в якому обчислюється її похідна та інтегральна сума. Вони помножуються на відповідні коефіцієнти згідно формули

надходить до регулятора Р, в якому обчислюється її похідна та інтегральна сума. Вони помножуються на відповідні коефіцієнти згідно формули  . Коефіцієнти підбираються так, щоб забезпечити високі показники якості перехідного процесу на виході перетворювача. Методика визначення коефіцієнтів наведена в розділі 4 посібника. Сума отриманих добутків відповідає значенню відносної тривалості імпульсів

. Коефіцієнти підбираються так, щоб забезпечити високі показники якості перехідного процесу на виході перетворювача. Методика визначення коефіцієнтів наведена в розділі 4 посібника. Сума отриманих добутків відповідає значенню відносної тривалості імпульсів  . Це число вдвічі більшої розрядності, ніж

. Це число вдвічі більшої розрядності, ніж  . В більшості випадків ця розрядність є надлишковою. Оскільки 0<

. В більшості випадків ця розрядність є надлишковою. Оскільки 0<  <1, можна зменшити розрядність, відкинувши 5 старших (заповнених знаковим розрядом) та 3 молодших розряди (точність до 5 знаку після коми). Це здійснюється у блоку сполучення БС. Там же отримане число множиться на значення періоду перетворення. Результат, що відповідає абсолютній тривалості імпульсу, поділеній на тривалість одного синхронізуючого імпульса

<1, можна зменшити розрядність, відкинувши 5 старших (заповнених знаковим розрядом) та 3 молодших розряди (точність до 5 знаку після коми). Це здійснюється у блоку сполучення БС. Там же отримане число множиться на значення періоду перетворення. Результат, що відповідає абсолютній тривалості імпульсу, поділеній на тривалість одного синхронізуючого імпульса  , надходить до 8-розрядного порту А цифрового компаратора D 2. На порт В надходить поточна кількість синхронізуючих імпульсів

, надходить до 8-розрядного порту А цифрового компаратора D 2. На порт В надходить поточна кількість синхронізуючих імпульсів  . Якщо

. Якщо  , інверсний вихід компаратора скидається в «0». Цей процес ілюструє рис. 1.8. Сигнал з виходу компаратора

, інверсний вихід компаратора скидається в «0». Цей процес ілюструє рис. 1.8. Сигнал з виходу компаратора  надходить до логічного елементу ТА, вихідний сигнал якого

надходить до логічного елементу ТА, вихідний сигнал якого  буде дорівнювати «1», якщо «1» дорівнюють сигнали

буде дорівнювати «1», якщо «1» дорівнюють сигнали  та

та  . Останній сигнал генерується аналоговим компаратором струмового захисту та дорівнює «0» якщо струм в силовому ключі перевищує встановлене максимальне значення.

. Останній сигнал генерується аналоговим компаратором струмового захисту та дорівнює «0» якщо струм в силовому ключі перевищує встановлене максимальне значення.

|

| Рис. 1.8. Часові діаграми ШІМ |

Одного мікроконтролера достатньо для реалізації всієї схеми на рис. 1.6. Наприклад, мікроконтролер PIC18F1320 фірми Microchip має вбудований 10-бітний АЦП з 7 каналами (може почергово обробляти 7 аналогових сигналів), модуль ШІМ, 3 таймери, модуль послідовного інтерфейсу SPI/IIC для комунікації з пультом управління [23]. Також можливо і доцільно використання сигнальних процесорів.

1.3. Аналогова частина системи управління

1.3.1. Схема струмового захисту

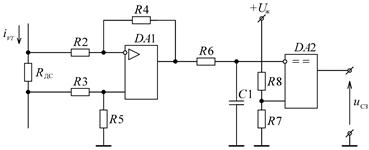

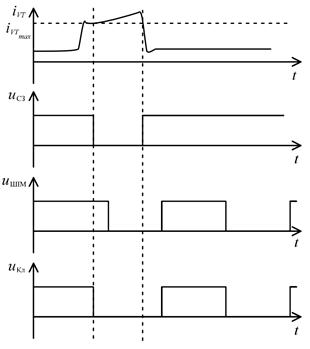

Схема струмового захисту (СЗ) наведена на рис. 1.9. Вона містить шунт R ДС, диференціальний підсилювач на операційному підсилювачі DA 1, фільтр низьких частот R 6, C 1, аналоговий компаратор DA 2. Принцип дії схеми ілюструє рис. 1.10.

|

| Рис. 1.9. Схема струмового захисту |

На шунті R ДС падає напруга, пропорційна струму через силовий ключ  . Опір шунта обирається таким чином, щоб втрати потужності на ньому були мінімальні. Найчастіше використовують для цього опори порядку 0,1 Ом. Ця напруга підсилюється диференційним підсилювачем DA 1. Якщо R 2= R 3, R 4= R 5, напруга на виході DA 1 складатиме

. Опір шунта обирається таким чином, щоб втрати потужності на ньому були мінімальні. Найчастіше використовують для цього опори порядку 0,1 Ом. Ця напруга підсилюється диференційним підсилювачем DA 1. Якщо R 2= R 3, R 4= R 5, напруга на виході DA 1 складатиме  .

.

|

| Рис. 1.10. Часові діаграми струмового захисту |

Фільтр R 6, C 1 не пропускає на вхід компаратора DA 2 високочастотні імпульси напруги, які утворюються в колі в момент замикання та розмикання силового ключа. Компаратор DA 2 порівнює напругу  із еталонним значенням

із еталонним значенням  . Якщо

. Якщо  , на виході DA 2 буде логічна «1». Якщо

, на виході DA 2 буде логічна «1». Якщо  , на виході DA 2 встановиться логічний «0». Сигнал з виходу DA 2 потрапляє до логічного елемента ТА (D 3, рис.1.6).

, на виході DA 2 встановиться логічний «0». Сигнал з виходу DA 2 потрапляє до логічного елемента ТА (D 3, рис.1.6).

1.3.2. Схеми драйверів силового ключа

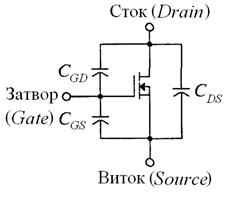

Найчастіше в якості силового ключа Кл використовується потужний польовий МОП-транзистор. Його втрати провідності в більшості випадків невеликі і відповідають падінню напруги порядку десятих долей вольта [2]. При керуванні ним між виводами затвора й витока повинна бути прикладена напруга 5-12В, щоб пропускати максимальний струм через стік. Час перемикання МОП-транзисторів звичайно складає 40-80 нс, тому необхідно враховувати його паразитні ємності (рис. 1.11).

|

| Рис. 1.11. Паразитні ємності МОП-транзистора |

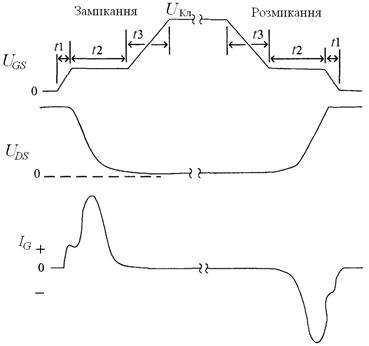

Ємність переходу виток-сток CDS не впливає на роботу формуючого каскаду. Ємності CGD та CGS зумовлюють затримки переключення МОП-транзистора, що можна побачити на часових діаграмах (рис. 1.12).

|

| Рис. 1.12. Часові діаграми перемикання транзистора |

Для того, щоб відкрити МОП-транзистор, необхідно зарядити ємності CGD та CGS. Найбільшою з них є ємність CGS або вхідна ємність МОП-транзистора (позначається також Ciss). Для її швидкого заряду необхідно генерувати потужні імпульси струму затвору IG. Вхідні ємності МОП-транзисторів малої потужності (до 1 Вт) можна підключати безпосередньо до системи управління. Ці малопотужні транзистори називають також МОП-транзисторами логічного рівня. Для їх відкриття та закриття достатньо струмів, стандартних для логічних мікросхем та мікроконтролерів.

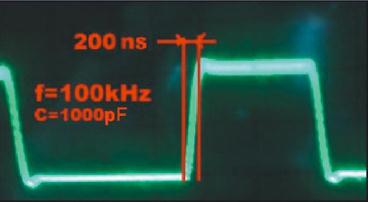

Якщо силовий МОП-транзистор має велику вхідну ємність, необхідно використати спеціальний формуючий каскад (ФК) або драйвер силового ключа, виконаний на дискретних транзисторах або у вигляді інтегральної мікросхеми. Задача драйвера – зарядити вхідну ємність МОП-транзистора за достатньо малий час (див. рис. 1.13).

|

| Рис. 1.13. Експериментальна осцилограма напруги «затвор-виток» силового МОП-транзистора із Ciss =1000 пФ |

При проектуванні ФК необхідно звернути увагу на включення МОП-транзистора в силовій схемі. У підвищуючому ППН (рис. 1.3 б) виток транзистора підключається до загальної точки («землі») силової схеми. У понижуючому та полярно-інвертуючому ППН (рис. 1.3 а,в) він включений послідовно між навантаженням та джерелом. В обох випадках для відкриття транзистора необхідний імпульс напруги між витоком та затвором. Точкою відліку амплітуди керуючого сигналу є потенціал витока. Але в першому випадку потенціал витока завжди нульовий, а в другому він варіюється. Тобто, для відкриття транзистора в першому випадку необхідний імпульс амплітудою U ж, а в другому U ж+ eS, де eS – потенціал витока. Схеми ФК для першого випадку прийнято називати «драйвер нижнього плеча», для другого – «драйвер верхнього плеча».

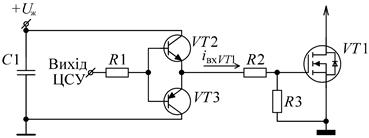

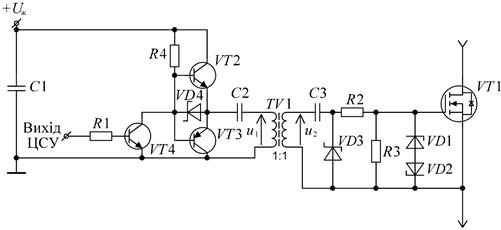

Розглянемо типову схему драйвера нижнього плеча (рис. 1.14).

|

| Рис. 1.14. Драйвер нижнього плеча |

Сигнал високого або низького рівня, необхідний для відкриття силового МОП-транзистора VT 1, надходить з виходу схеми ЦСУ (рис. 1.5). Два емітерні повторювачі на транзисторах різного типу провідності (VT 2, VT 3) забезпечують закриття та відкриття VT 1. Струм при відкритті VT 1 (і вх VT 1) значно перевищує струм виходу ЦСУ.

і вх VT 1 = (h 21E+1) і вихЦСУ,

де h 21E – коефіцієнт передачі за струмом транзистора VT 2 [11].

Це співвідношення показує, що можна одержати великий струм при відкритті MOП-транзистора і при цьому значно розвантажити вихідний каскад ЦСУ. Стала часу заряду вхідної ємності польового транзистора в схемі по рис. 1.12 виходить у багато разів менше, ніж при керуванні безпосередньо від ЦСУ, що забезпечує швидкий процес включення. Для вимикання VT 1 на виході ЦСУ повинен бути сигнал близький до нуля. При цьому відмикається біполярний транзистор VT 3 і розряд вхідної ємності VT 1 відбувається зі сталою часу, близькою до значення R 2∙ СGS. В цьому випадку вихідний струм ЦСУ також є невеликим, оскільки він обмежується сумою опорів R 1 і приведеного до бази VT 3 опору R 2.

Резистор R 3, показаний на рис. 1.14, начебто є зайвим елементом, який без втрат властивостей схеми можна виключити. Однак уявимо ситуацію, коли на перетворювач подана вхідна напруга, вона присутня на стоці транзистора VT 1, а напруга U ж, яка надходить від додаткового джерела, ще дорівнює нулю. Тому обидва біполярні транзистори закриті, ЦСУ ще не працює, а транзистор VT 1 може бути відкритий сигналом завади. Включення резистора R 3 запобігає виходу з ладу транзистора VT 1 у проміжку часу, коли напруга живлення U ж ще не подана або за якимись причинами відсутня. Звичайно опір R 3 багато більше, ніж опори R 1 і R 2, а потужність, що розсіюється на ньому, не перевищує декількох десятків міліват.

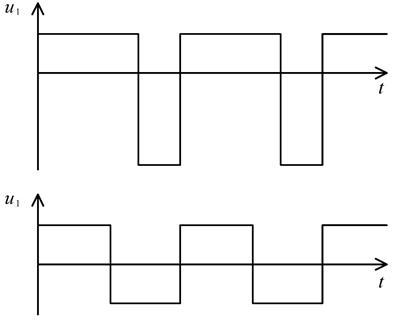

Схема драйвера верхнього плеча наведена на рис. 1.15.

|

| Рис. 1.15. Трансформаторна схема драйвера верхнього плеча |

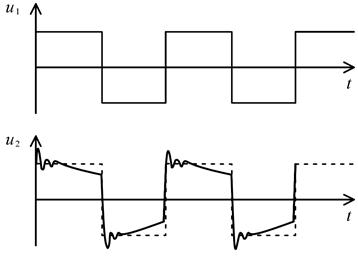

Вона заснована на комплементарній двотактній схемі драйвера нижнього плеча, але має кілька характерних особливостей. Перш за все, схема управління має бути гальванічно ізольована від силової частини. Для цього вводиться трансформатор управління. Розподільний конденсатор С 2 необхідний для того, щоб середній струм намагнічування трансформатора дорівнював нулю. Кількість вольт-секунд додатної та від’ємної півхвиль імпульсів напруги на обмотці завжди рівна (див. рис. 1.16).

|

| Рис. 1.16. Імпульси з рівною кількістю вольт-секунд |

Як можна побачити, умова рівності вольт-секунд за однакової амплітуди півхвиль виконується лише за коефіцієнта заповнення 0,5 або близького. Тому дана схема частіше всього використовується в півмостових та мостових перетворювачах постійної напруги [11]. За коефіцієнтів, близьких до 0,9, амплітуда від’ємної півхвилі в кілька разів більша за амплітуду додатної. Так, за амплітуди додатної півхвилі 12 В, амплітуда від’ємної може сягати 40 В. Тому потрібна напруга живлення драйвера U ж=40В. Це, по-перше, збільшує втрати в перетворювачі, а, по-друге, може виявитись, що напруга затвор-виток під час від’ємного імпульсу перевищує напругу пробою МОП-транзистора. Для боротьби з цим ефектом між затвором та витоком окрім обмежувального резистора зустрічно включаються два стабілітрони VD 1 та VD 2. Ще одним недоліком є затухання напруги на вторинній обмотці трансформатора (рис. 1.17).

|

| Рис. 1.17. Затухання напруги на вторинній обмотці |

Це явище зумовлює необхідність додаткового підвищення напруги живлення драйвера.

Для відновлення форми напруги затвор-виток, еквівалентної до вихідного сигналу ЦСУ, в контур включають конденсатор С 3 та діод VD 3, через який конденсатор С 3 заряджається до середньої напруги на вторинній обмотці трансформатора. Для компенсації несиметрії схеми, зумовленої рівністю вольт-секунд, вводиться додатковий транзистор VT 4, який працює паралельно із VT 3, пропускаючи струм при розмиканні МОП-транзистора VT 1.

Заощадити енергію, необхідну для живлення драйвера, та зменшити масу та габарити перетворювача дозволяє застосування інтегральних мікросхем. Сучасна індустрія напівпровідникових приладів пропонує мікросхеми драйверів верхніх та нижніх плечей, а також об’єднані драйвери в інтегральному виконанні. Ці мікросхеми забезпечують швидке перемикання силових МОП-транзисторів в перетворювальних схемах із вхідними напругами до 1200В. Найбільш відомі серії драйверів випускають компанії International Rectifier, Texas Instruments, Analog Devices.

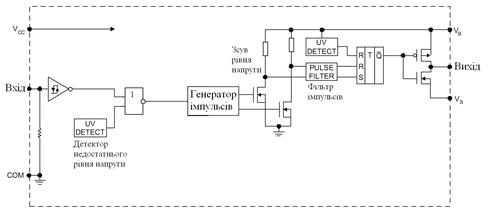

Внутрішня структура інтегральної мікросхеми драйвера верхнього плеча наведена на рис. 1.18.

|

| Рис. 1.18. Внутрішня структура інтегральної мікросхеми драйвера верхнього плеча |

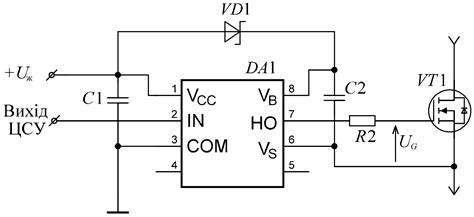

На рис. 1.19 наведено схему підключення інтегрального драйвера верхнього плеча.

|

| Рис. 1.19. Типове підключення інтегрального драйвера верхнього плеча |

Внутрішня структура інтегральної мікросхеми драйвера верхнього плеча є вдосконаленою модифікацією комплементарного двотактного драйвера на МОП-транзисторах. Мікросхема містить пристрої відстежування рівня напруги живлення та керуючих імпульсів.

Напруга живлення вихідного каскаду драйвера, як вже було сказано вище, має бути «плаваючою». Тобто, вона має становити U ж+ ES, де ES – потенціал витока. Для забезпечення цього застосовується так зване накопичуюче коло (bootstrap circuit), яке складається з резистора R 4, діода VD 1 та конденсатора C 2. Коли транзистор VT 1 закритий, конденсатор C 2 заряджається від джерела живлення драйвера до напруги U ж. Потенціал на вході VB, від якого живиться вихідний каскад мікросхеми, таким чином, буде дорівнювати U ж+ ES незалежно від величини ES. Однак для того, щоб конденсатор зарядився до напруги U ж, потенціал ES протягом часу заряду має дорівнювати нулю. В схемі понижуючого перетворювача ця умова виконується, оскільки при закритому транзисторі VT 1 струм в колі навантаження не протікає. В полярно-інвертуючому перетворювачі при закритому транзисторі VT 1 (при верхньому розташуванні ключа, див. рис. 1.24) потенціал ES =  . Конденсатор C 2 зарядиться до напруги U ж

. Конденсатор C 2 зарядиться до напруги U ж  . Ця напруга може перевищувати максимальну припустиму для мікросхеми драйвера. Тому при такому розташуванні транзистора VT 1 необхідно застосовувати трансформаторну схему драйвера. Це ускладнює розрахунок системи управління перетворювача та її реалізацію, оскільки трансформатор вимагає окремого розрахунку та копіткого процесу намотки. Спростити задачу можна, обравши «нижнє» розташування транзистора VT 1 (див. рис. 1.23). При такому розташуванні транзистор включається між контактом живлення та загальною «землею» схеми. Виток його підключається до «землі», тому його потенціал ES = 0. Включення інтегральної мікросхеми буде таким же, як і в понижуючому перетворювачі.

. Ця напруга може перевищувати максимальну припустиму для мікросхеми драйвера. Тому при такому розташуванні транзистора VT 1 необхідно застосовувати трансформаторну схему драйвера. Це ускладнює розрахунок системи управління перетворювача та її реалізацію, оскільки трансформатор вимагає окремого розрахунку та копіткого процесу намотки. Спростити задачу можна, обравши «нижнє» розташування транзистора VT 1 (див. рис. 1.23). При такому розташуванні транзистор включається між контактом живлення та загальною «землею» схеми. Виток його підключається до «землі», тому його потенціал ES = 0. Включення інтегральної мікросхеми буде таким же, як і в понижуючому перетворювачі.

1.4. Принципова схема перетворювача

Для зручності принципова схема буде розділена на дві частини. Цифрова частина, незмінна для всіх трьох типів перетворювачів, зображена на рис. 1.20. Схеми силової частини понижуючого, підвищуючого та полярно-інвертуючого (із інтегральним та трансформаторним драйверами) ППН зображені на рис. 1.21-1.24 відповідно. Точки сполучення силової та цифрової частини позначені «прапорцями» ( ).

).

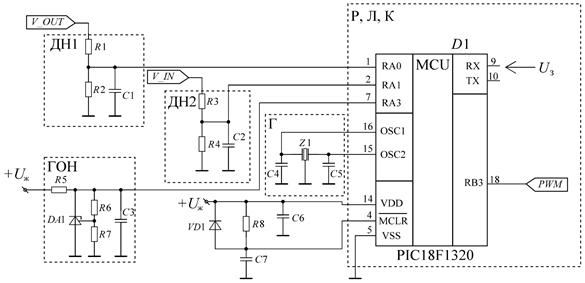

Цифрова частина системи управління ППН реалізована на 8-бітному мікроконтролері PIC18F1320 (рис. 1.19). Принципи побудови такої системи наведено в [19].

|

| Рис. 1.20. Цифрова частина системи управління ППН |

Вхідна та вихідна напруга перетворювача знімається в точках, позначених V_IN та V_OUT відповідно. Вбудований АЦП мікроконтролера може опрацювати сигнал, амплітуда якого не перевищує величини опорної напруги. Тому вхідна та вихідна напруги масштабуються за допомогою дільників напруги ДН1 (резистори R 1, R 2, конденсатор С 1) та ДН2 (резистори R 3, R 4, конденсатор С 2). Значення напруги на виході дільників дорівнює  ,

,  . Конденсатори призначені для фільтрації високочастотних імпульсів напруги, які з’являються в момент комутації силового ключа. Їх номінали вибираються таким чином, щоб час заряду дорівнював (10..50)∙

. Конденсатори призначені для фільтрації високочастотних імпульсів напруги, які з’являються в момент комутації силового ключа. Їх номінали вибираються таким чином, щоб час заряду дорівнював (10..50)∙  . Сигнал з виходу дільників надходить на входи вбудованого АЦП мікроконтролера RA0 та RA1 (1-й та 2-й контакти мікроконтролера).

. Сигнал з виходу дільників надходить на входи вбудованого АЦП мікроконтролера RA0 та RA1 (1-й та 2-й контакти мікроконтролера).

Опорна напруга формується за допомогою регульованого джерела опорної напруги (РДОН), яке містить стабілізатор DA 1 типу TL431, резистори R 5, R 6, R 7 та конденсатор С 3. Резистор R 5 обмежує струм у колі стабілізатора. Пара резисторів R 6, R 7 задає величину опорної напруги. Конденсатор С 3 фільтрує високочастотні шуми, які можуть наводитись в колі стабілізатора в моменти комутації. Опорна напруга з виходу РДОН надходить на спеціальний вхід АЦП RA3.

Тактовий генератор (Г) побудований на кварцовому резонаторі Z 1. Конденсатори С 4, С 5 стабілізують роботу резонатора. Резистори та інвертори в схемі генератора на рис. 1.6, вбудовані в схему мікроконтролера. Генератор підключається до входів OSC1 та OSC2.

Конденсатор С 6 захищає вхід живлення мікроконтролера VDD від високочастотних завад. На вхід скидання мікроконтролера  через підтягуючий резистор R 8 подається логічна одиниця (заборона скидання). Вхід захищається від високочастотних завад конденсатором С 7 та діодом VD 1.

через підтягуючий резистор R 8 подається логічна одиниця (заборона скидання). Вхід захищається від високочастотних завад конденсатором С 7 та діодом VD 1.

Значення бажаної вихідної напруги  надходить з панелі управління через інтерфейс універсального синхронно-асинхронного прийомника-передатчика (УСАПП, англ. USART). Вхід RX відповідає за прийом даних у послідовному форматі, вихід TX – за передачу даних в послідовному форматі. На панель управління по УСАПП може передаватись виміряне значення вихідної напруги.

надходить з панелі управління через інтерфейс універсального синхронно-асинхронного прийомника-передатчика (УСАПП, англ. USART). Вхід RX відповідає за прийом даних у послідовному форматі, вихід TX – за передачу даних в послідовному форматі. На панель управління по УСАПП може передаватись виміряне значення вихідної напруги.

Керуючий сигнал для силового ключа знімається з виходу модуля захвату-порівняння та ШІМ (Capture/Compare/PWM Module, CCP) RB3.

При включенні напруги живлення мікроконтролера конфігуруються периферійні пристрої: модулі АЦП, ШІМ та таймер 2, очищується пам'ять, необхідна для зберігання змінних, встановлюються початкові значення деяких змінних. Зовнішні контакти конфігуруються відповідно до їх функцій.

Контакти RA0, RA1, RA3 конфігуруються як аналогові входи. Контакти TX, RX конфігуруються як цифровий вихід та цифровий вхід відповідно. Джерелом опорної напруги АЦП встановлюється вхід RA3. Для модуля CCP встановлюється режим ШІМ. Встановлюються необхідні значення передподільника таймера 2 та регістру PR2 для завдання частоти перетворення за формулою  , де

, де  ‑ період синхронізуючого сигналу, що надходить від генератора Г.

‑ період синхронізуючого сигналу, що надходить від генератора Г.

Під час роботи контролера АЦП почергово перетворює сигнал з дільників напруги ДН1 та ДН2 на двійковий код. Якщо значення вхідної напруги (сигнал з ДН2) менше 10В, контролер зберігає змінні, розмикає силовий ключ та відключається.

Значення вихідної напруги зберігається в змінній VOUT, значення бажаної вихідної напруги – в змінній SETPOINT. Різниця між SETPOINT та VOUT зберігається в двохбайтній змінній E0H:E0. Старший байт E0H є розширенням знакового розряду. Якщо SETPOINT>VOUT, результат додатній.

E0 = SETPOINT – VOUT

Якщо сьомий біт змінної E0 E0<7>=0, E0H=0х00, інакше E0H=0хFF.

Пропорційний елемент забезпечує посилення сигналу помилки і швидко компенсує помилку виходу, але повністю її не усуває. При цьому значення помилки зі знаком множиться на коефіцієнт КР. Результат зберігається в 2-байтній змінній зі знаком РRОН:РRО.

РRОН:РRО = КР * Е0Н:Е0,

де КР ‑ пропорційний коефіцієнт.

Диференціальний елемент обчислює різницю між поточною й попередньою помилкою й множить її на коефіцієнт KD. Отриманий результат зберігається в 2-байтній змінній зі знаком DIFH:DIF. Попередня помилка Е1Н:Е1 отримується при виконанні попереднього циклу аналого-цифрового перетворення.

DIFH:DIF = KD * (Е1Н:Е1 - Е0Н:Е0),

де KD - коефіцієнт диференціювання.

Інтегральний елемент підсумує всі помилки, отримані починаючи з останнього скидання і компенсує всю помилку, але повільно. Поточна помилка множиться на коефіцієнт KI і додається до накопиченого значення в 2-байтній змінній без знака INTH:INT.

INTH:INT = INTH:INT + KI * Е0Н:Е0,

де KI ‑ коефіцієнт інтегрування.

Значення, отримані пропорційним, диференціальним й інтегральним елементами, сумуються разом, сума зберігається в 2-байтній змінній зі знаком PWMH:PWM.

PWMH:PWM = РRОН:РRО + DIFH:DIF + INTH:INT

Результат завжди повинен бути позитивним, негативне значення викликає антипереповнення. Якщо PWMH:PWM антипереповнюється (це можливо при відсутності навантаження), то вихідний сигнал PWM повинен бути нульовим, інакше вихід перетворювача може стати непередбаченим. При цьому включається індикатор перевантаження.

Якщо PWMH <7> = 1, то PWMH:PWM = 0x0000 і включається індикатор, інакше індикатор виключений.

Блок сполучення (БС на рис. 1.6) відкидає 3 молодших й 5 старших розрядів і використовує 8 розрядів, що залишилися, для формування часу включення ШІМ  . Із 8 розрядів, що залишилися, 2 молодших завантажуються в біти регістру CCP1CON <5:4>, а інші 6 розрядів (доповнюються 2 нулями в старших розрядах, щоб сформувати байт) завантажуються в регістр CCPR1L. Коефіцієнт аповнення імпульсів

. Із 8 розрядів, що залишилися, 2 молодших завантажуються в біти регістру CCP1CON <5:4>, а інші 6 розрядів (доповнюються 2 нулями в старших розрядах, щоб сформувати байт) завантажуються в регістр CCPR1L. Коефіцієнт аповнення імпульсів  , таким чином, буде визначено як

, таким чином, буде визначено як

.

.

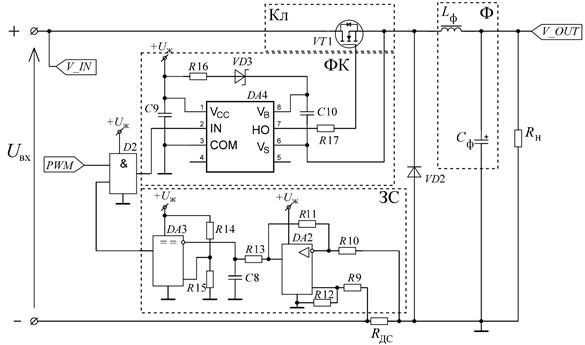

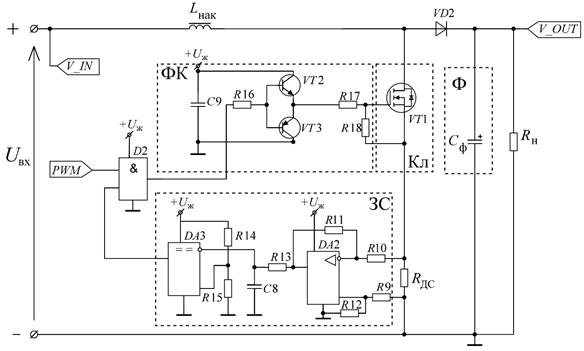

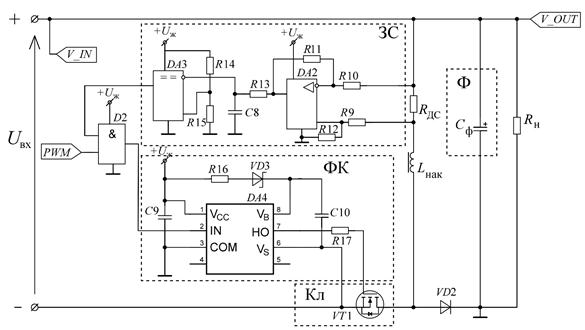

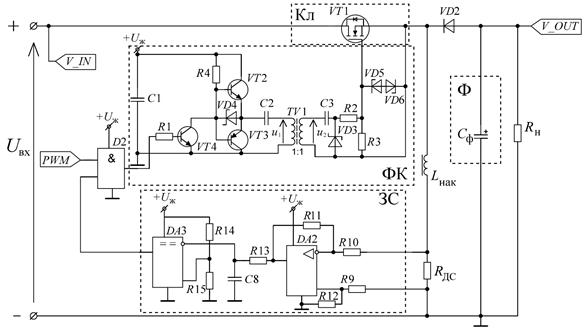

Сигнал з виходу PWM надходить на один з входів логічного елемента ТА D 2, показаного на рис. 1.21-1.24. На інший вхід елемента ТА в усіх трьох схемах перетворювачів надходить сигнал від аналогового компаратора схеми струмового захисту. Ці схеми ідентичні для всіх трьох типів ППН та побудовані в точності так, як було описано в розділі 1.3.1. Розрізняється лише місце підключення резистора датчика струму R ДС.

|

| Рис. 1.21. Силова частина та аналогова частина СУ понижуючого ППН |

|

| Рис. 1.22. Силова частина та аналогова частина СУ підвищуючого ППН |

|

| Рис. 1.23. Силова частина та аналогова частина СУ інвертуючого ППН із інтегральним драйвером |

|

| Рис. 1.24. Силова частина та аналогова частина СУ інвертуючого ППН із трансформаторним драйвером |

Силові схеми на рис. 1.21-1.24 розрізняються включенням силового ключа, реалізованого на МОП-транзисторі VT 1, конфігурацією формуючих каскадів (драйверів силового ключа) та розміщенням пасивних елементів силового контуру. Це зумовлене принципом дії кожної схеми (див. розділ 1.1). В понижуючому ППН (рис. 1.21) індуктивність L ф входить до складу вихідного фільтра та згладжує пульсації струму в колі навантаження. В підвищую чому та полярно-інвертуючому ППН індуктивність, позначена L нак, накопичує енергію, коли ключ VT 1 замкнено, та віддає її у навантаження, коли ключ VT 1 розімкнено.

В схемі підвищуючого ППН (рис. 1.22) формуючий каскад реалізовано як драйвер нижнього плеча на комплементарних транзисторах VT 2 та VT 3. В понижуючому ППН (рис. 1.21) застосовано типове включення інтегрального драйвера верхнього плеча (див. розділ 1.3.2). В полярно-інвертуючому ППН при нижньому розташуванні ключа (рис. 1.23) можливо використовувати формуючий каскад на основі інтегральної мікросхеми драйвера верхнього плеча (див. розділ 1.3.2). При верхньому розташуванні ключа (рис. 1.24) необхідно застосовувати трансформаторний драйвер верхнього плеча.

Принципові схеми ППН також можуть містити мережевий випрямляч, вхідний фільтр, схему живлення системи управління, демпфуюче коло (RC або RL- коло, яке розсіює сплески енергії на ключі в момент комутації), схему захисту від сплесків мережної напруги, схему корекції потужності та ін., проектування яких виходить за межі курсового проекту. Послідовність розрахунку та особливості проектування таких схем для розглянутих вище, а також інших типів перетворювачів, докладно описані в [2, 7-11].

Слід зазначити, що запропонована принципова схема СУ ППН є рекомендованою. Вона не може бути досконалою з усіх точок зору. Тому студенти можуть при вирішенні конкретної задачі проектування вносити зміни та спрощення у СУ, які, на їх погляд, можуть вдосконалити її роботу. Єдиною умовою при цьому є збереження основного принципу дії перетворювача, тобто типу силової схеми, кількості силових елементів.

2. РОЗРАХУНОК СИЛОВОЇ ЧАСТИНИ ІМПУЛЬСНИХ ПЕРЕТВОРЮВАЧІВ ПОСТІЙНОЇ НАПРУГИ

2.1. Приклади вихідних даних

У таблиці приведено вихідні дані для прикладів розрахунку схем понижуючого, підвищуючого та інвертуючого ППН (умовно П1, П2 і П3). Методику розрахунку у вигляді прикладів наведено нижче.

| Вихідні дані | П1 | П2 | П3 |

Номінальна вхідна напруга  , В , В | - | ||

Нестабільність середнього значення вхідної напруги,  |  0,1 0,1 |  0,15 0,15 |  0,1 0,1 |

Амплітуда пульсацій на вході,  | 0,05 | 0,05 | |

Значення вихідної напруги  ; ;  ; ;  , В , В | 70; 90; 110 | 20; 24; 27 | 7; 10; 13 |

Значення струму навантаження  ; ;  , А , А | 1; 5 | 0,2; 1 | 0,3; 1,5 |

Змінна складова вихідної напруги  , В , В | 0,1 | 0,1 | 0,15 |

| ККД | 0,77 | 0,74 | 0,76 |

Частота перетворення  , кГц , кГц |

2.2. Визначення вхідної напруги та коефіцієнтів заповнення імпульсів

Безтрансформаторні ППН найчастіше використовуються як вбудовані на плату локальні джерела живлення, які перетворюють величину напруги, що подається по шині живлення, на величину, яку потребують пристрої, що знаходяться на даній платі. Вбудовані ППН можуть живитись від мережевого випрямляча із блоком корекції коефіцієнта потужності, або, частіше, від основного джерела живлення (англ. front-end power supply). Основне джерело живлення – це звичайно перетворювач змінного струму у постійний із гальванічною розв’язкою виходу та входу.

Тому можливі два шляхи визначення вхідної напруги для вбудованих ППН. Якщо спочатку обирається основне джерело живлення, його номінальна вихідна напруга є номінальною вхідною напругою для вбудованого ППН. Вона зазначається в таблиці вхідних даних. Якщо ж спочатку проектуються вбудовані ППН, а потім для них проектується основне джерело, необхідно розрахувати бажану вхідну напругу для вбудованого ППН.

Якщо у вихідних даних зазначена номінальна вхідна напруга  , то на початку розрахунків слід знайти

, то на початку розрахунків слід знайти  і по ньому обчислити

і по ньому обчислити  . При цьому для П1 повинно бути

. При цьому для П1 повинно бути  , а для П2 і П3

, а для П2 і П3  при

при  (див. рис. 1.5). Якщо вхідна напруга не задана, то потрібно задатися максимальним коефіцієнтом заповнення та знайти мінімальну бажану вхідну напругу:

(див. рис. 1.5). Якщо вхідна напруга не задана, то потрібно задатися максимальним коефіцієнтом заповнення та знайти мінімальну бажану вхідну напругу:

- для П1  ;

;

- для П2,3  .

.

Мінімальна вхідна напруга:

- Для П1  В;

В;

- Для П2  В;

В;

- Для П3 номінальну вхідну напругу не вказано, тому слід використати формулу для обчислення мінімальної бажаної вхідної напруги (див. нижче).

Мінімальна бажана вхідна напруга визначається лише у разі відсутності номінальної вхідної напруги серед вхідних даних:

- для П1

В;

В;

- для П2

В;

В;

- для П3

В,

В,

де попередньо прийняте  В - пряме спадання напруги на комутуючому діоді

В - пряме спадання напруги на комутуючому діоді  ;

;  В - напруга насичення «вток-сток» регулюючого транзистора

В - напруга насичення «вток-сток» регулюючого транзистора  ;

;  - постійна складова напруги

- постійна складова напруги  на дроселі (спадання напруги на його активному опорі).

на дроселі (спадання напруги на його активному опорі).

Номінальна бажана вхідна напруга (у випадку відсутності серед вхідних даних):

;

;

Оскільки для П1 та П2 номінальна вхідна напруга задана, розрахуємо бажану номінальну вхідну напругу для П3:

В.

В.

Максимальна вхідна напруга:

,

,

де  ‑ номінальна вхідна напруга за таблицею (для П1, П2) або номінальна бажана вхідна напруга (для П3).

‑ номінальна вхідна напруга за таблицею (для П1, П2) або номінальна бажана вхідна напруга (для П3).

- для П1  В;

В;

- для П2  В;

В;

- для П3  В.

В.

Мінімальне, номінальне та максимальне значення коефіцієнтів заповнення імпульсів:

- для П1

;

;

;

;

;

;

- для П2

;

;

;

;

;

;

- для П3

;

;

;

;

.

.

Для П1-П3 повинна дотримуватися умова  , інакше потрібно відкоригувати припущення або вихідні дані. Перш за все, слід перевірити вхідні дані. Якщо для П1

, інакше потрібно відкоригувати припущення або вихідні дані. Перш за все, слід перевірити вхідні дані. Якщо для П1  , або для П2

, або для П2  , дані записані невірно, їх необхідно уточнити у викладача.

, дані записані невірно, їх необхідно уточнити у викладача.

2.3. Визначення індуктивності дроселя і ємності фільтруючого конденсатора

Маса та габарити перетворювача повинні бути за заданих параметрів напруги та струму якомога меншими. Найбільш габаритні елементи ППН – фільтруюча або накопичувальна індуктивність L ф (L нак для П2 та П3), фільтруюча ємність С ф та радіатор силового МО

2015-02-14

2015-02-14 1408

1408