Лабораторная работа № 4

Исследование регистров

Общие сведения

Регистром называется устройство, предназначенное для хранения и преобразования машинного слова. Так как машинное слово может быть разной разрядности, то регистр называется N-разрядным. Различают два типа регистров – последовательные и параллельные. Различие заключается в способе ввода и вывода информации при «загрузке» регистра данными. Выпускаемые промышленностью регистры, как правило, универсальны и позволяют работать как с последовательными, так и с параллельными данными.

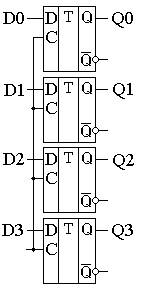

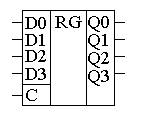

Параллельный (буферный) регистр служит для запоминания многоразрядного двоичного слова. Чаще всего такие регистры строятся на базе D-триггеров. Количество триггеров, входящее в состав параллельного регистра определяет его разрядность. Схема четырёхразрядного параллельного регистра приведена на рисунке 1, а его условно-графическое обозначение - на рисунке 2.

Рис.1 Схема четырехразрядного параллельного регистра

Рис. 2. Условное графическое обозначение параллельного регистра

Принцип записи данных в регистр очевиден из рис.1. Так как D-триггер позволяет сохранить значение одного бита, то объединяя входы загрузки C для каждого разряда можно сохранить, таким образом, машинное слово. При этом способ синхронизации (статический, динамический, по фронту или срезу) определяется особенностями триггеров, входящих в состав регистра. На практике тип синхронизации оговаривается в документации к регистру. Так как инверсные выходы триггеров обычно используются редко, в регистре они не используются. Таким образом, буферный параллельный регистр (в англоязычной переводной литературе называется регистром-защелкой) представляет собой простейшую ячейку памяти емкостью в одно машинное слово. Такие регистры обычно используются в составе операционных блоков микропроцессора для хранения промежуточных данных (например, для хранения операндов для арифметико-логического устройства). Следует помнить, что назначение разрядов является условным. Это означает, что понятие старшего и младшего разрядов в регистрах не используется, а обозначение D0-D3 служит лишь для соответствия этим входам выходов Q0-Q3.

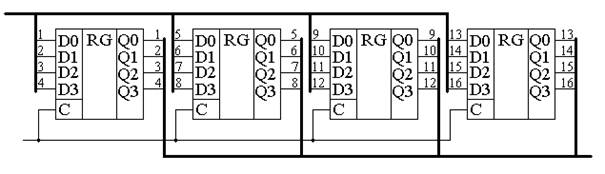

Если регистры используются как независимые устройства, они выпускаются промышленностью как 4-8- или 16-разрядные. При решении практических задач часто требуется разрядность параллельных регистров большая 8 или 16. В таком случае можно увеличивать разрядность регистров параллельным соединением готовых микросхем. Принципиальная схема параллельного соединения четырёх регистров приведена на рисунке 3.

Рис. 3. Увеличение разрядности регистра

Очевидно, что каждый из используемых 4-разрядных регистров хранит определенную часть машинного слова. В данном примере показано, что регистры 1-4 хранят 16 битное число (разряды 0-3, 4-7, 8-11, 12-15 соответственно). На рис. 4 показана временн а я диаграмма работы буферного регистра.

Рис. 4. Временная диаграмма работы регистра

Если C=0, на выходе Q регистра сохраняется значение, которое было загружено в регистр ранее. При этом, изменение состояния на входах, соответствующее М1, не приводит к изменению состояния регистра. По фронту на входе С производится защелкивание информации (М2) и сохранение ее до следующей перезаписи (М3). Существует модификация буферного регистра, имеющая название «защелка с просвечиванием». Данная модификация совмещает регистр со схемой «И» для каждого входа и входа С. При этом, если C=1 регистр работает как транслятор логических состояний (Q=D). Если происходит смена С=1 на C=0, данные в регистре защелкиваются.

Последовательные регистры можно условно разделить на три типа: последовательно-параллельные регистры, параллельно-последовательные регистры и универсальные сдвиговые регистры. Первые два типа отличаются друг от друга способом ввода и вывода информации. Последовательно-параллельный регистр принимает N-разрядное слово через специальный последовательный вход D и формирует на выходах Q машинное слово по мере поступления данных. На рис. 5 показана схема последовательно-параллельного регистра, на рис. 6 – его условное обозначение.

Рис.5. Схема последовательно-параллельного регистра

Рис. 6. Условное графическое обозначение последовательно-параллельного регистра

При подаче на вход С импульса сдвига производится передача текущего состояния триггера на вход последующего. При этом, на вход первого (младшего) триггера необходимо подать текущее значение загружаемого бита. Очевидно, что если требуется загрузить M-разрядное слово в N-разрядный регистр, потребуется N тактовых импульсов. При этом значение M не должно превышать N, в противном случае старшая часть слова будет потеряна. Следует учитывать, что триггеры в данном включении должны быть двухступенчатыми или динамическими. Это условие делает возможным корректную передачу бита от триггера к триггеру без возникновения эффекта «гонки сигналов». На рис. 7 показан пример загрузки 4-разрядного слова в 4-разрядный последовательно-параллельный регистр.

Рис.7. Пример загрузки слова в последовательно-параллельный регистр

Последовательно-параллельный регистр имеет важное свойство – при загрузке слова на каждом его выходе формируется последовательный код этого же числа, с задержкой. Например, на выходе Q1 формируется последовательность, соответствующая D, но с запаздыванием на 1 такт. На выходе Q2 – 2 такта и т.д. Если рассматривать регистр как устройство хранения битовой последовательности, то его можно назвать устройством магазинной памяти FILO (Firs Input – Last Output) – «первый вошел – последний вышел».

Параллельно-последовательный регистр работает следующим образом. Загрузка данных производится в параллельном виде, а передача данных на выход – в последовательном. Очевидно, что такой тип регистра более сложен, так как в его схемотехнике необходимо учесть как сдвиговые операции, так и операции загрузки. На практике такие регистры используются редко, так как реализация операций сдвига предусматривает также и операцию последовательной загрузки. Поэтому чаще всего используются универсальные регистры, которые позволяют загружать и выдавать данные в последовательном и параллельном виде. Для выбора операций предусмотрены дополнительные входы. На рис.8. показана схема универсального регистра. Принцип его работы заключается в следующем. На входе D каждого триггера выполнена логическая схема-мультиплексор. В зависимости от состояния V вход D каждого триггера логически коммутируется либо со входом DI для каждого разряда, либо с выходом предыдущего триггера. Например, если требуется загрузить параллельное число в регистр, а затем сдвинуть его на несколько разрядов, необходимо переключить мультиплексор (V=1), подать на входы число D0-D3 и подать на вход С тактовый импульс. Далее, необходимо переключить мультиплексор (V=0), при этом входы D0-D3 отключаются от триггеров и регистр превращается в последовательно-параллельный. Дальнейшая подача тактовых импульсов на вход C сдвигает число в регистре в сторону старших разрядов.

Рис. 8. Универсальный регистр

Условное обозначение универсального регистра приведено на рис. 9.

Существует ряд модификаций универсальных регистров. В частности, в некоторых случаях предусмотрен сдвиг не только вправо, но и влево, в сторону младших разрядов.

Рис. 9. Условное графическое обозначение универсального регистра

Регистры с Z-состоянием. В вычислительной технике часто возникает необходимость передавать данные от нескольких источников к одному или нескольким приемникам данных. Очевидно, что простое соединение выходов источников со входом приемника не является корректным, так как это может привести к короткому замыканию выхода с напряжением логической единицы на выход с логическим нулем. В англоязычной литературе такой процесс получил название «сквозной ток». Решение проблемы может быть реализовано в виде мультиплексора (рис. 10).

Рис. 10. Коммутация нескольких источников на один приемник

Если требуется подключить выход устройства У1 к линии P, необходимо подать на вход S единицу. В противном случае, к линии P подключается выход У2. Данное решение имеет ряд недостатков:

· реализация мультиплексора для устройств с количеством больше двух требует наличия дешифратора;

· коммутация многоразрядных сигналов требует применения многоразрядного мультиплексора, что представляет некоторую сложность;

· добавление нового устройства требует изменения схемы соединения, что делает систему принципиально нерасширяемой (системой с жесткой структурой).

Следует также отметить, что мультиплексорная коммутация выполняется на логическом уровне, оперируя исключительно с логическими уровнями.

Для исключения перечисленных недостатков в некоторых узлах ЭВМ используется Z-состояние (высокоомное, высокоимпедансное). Принцип Z-состояния показан на рис. 11.

Рис. 11. Применение Z-состояния для мультиплексирования

В состав каждого устройства входит аналоговый ключ, управляемый цифровым сигналом CS (Crystal Select, выбор кристалла). Если ключ замкнут (CS=1), то выход устройства У физически подключен к выходу P. Если ключ разомкнут (CS=0), то между выходом У и линией P создается высокое сопротивление, значение которого стремится к бесконечности и зависит от параметров аналогового ключа. Между линией P и общим проводом устройства также возникает сопротивление Z, величина которого стремится к бесконечности. Следует отметить, что при замкнутом ключе величина Z стремится к нулю, так как выход У имеет очень низкое выходное сопротивление. Таким образом, подключая поочередно У1 и У2 к линии P можно добиться эффекта мультиплексирования, показанного на рис. 10, но с гораздо меньшими аппаратными затратами, без мультиплексора MX. Для схем с Z-состояниями необходимо придерживаться следующих требований при разработке устройств на их основе:

· В каждый момент времени должен быть замкнут только один ключ SW (должно быть активно только одно устройство);

· Переключение устройств должно производиться через промежуточное состояние «все устройства отключены». Это исключает протекание сквозных токов через выходы устройств;

· Обращение к шине P должно производится в те моменты, когда к ней подключено хотя бы одно устройство. В противном случае Z-состояние будет восприниматься входом логического элемента некорректно, и может вывести последний из строя (например, для КМОП-технологии).

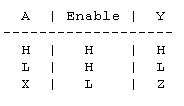

В среде Electronic WorkBench для моделирования Z-состояния используется элемент «Tristate Buffer», выполняющий роль ключа SW с входом разрешения «Enable», условное обозначение которого показано на рис. 12. При этом, H=1, L=0, Z – высокоомное состояние.

Следует учитывать, что логика элемента отличается от логики элемента «И», так как Z не является логическим уровнем.

Рис. 12. Условное обозначение элемента с Z-состоянием и логика его работы

При необходимости, можно создавать n-разрядные элементы, соединяя между собой входы EN. При этом, устройства можно объединять посредством n-разрядной шины (магистрали), как показано на рис. 13.

Рис. 13. Организация шины с помощью шинных формирователей

Если устройство имеет встроенные средства управления Z-cсостоянием, в условном обозначении присутствует знак « ». На рис. 13 показан пример, когда любое устройство может быть подключено к шине с помощью отдельного узла, имеющего название «шинный формирователь», выполненный на элементах, показанных на рис. 12. При этом, дешифратор кода устройства обеспечивает подключение к шине только одного из выбранных устройств, что исключает аппаратный конфликт.

». На рис. 13 показан пример, когда любое устройство может быть подключено к шине с помощью отдельного узла, имеющего название «шинный формирователь», выполненный на элементах, показанных на рис. 12. При этом, дешифратор кода устройства обеспечивает подключение к шине только одного из выбранных устройств, что исключает аппаратный конфликт.

2015-02-24

2015-02-24 3504

3504