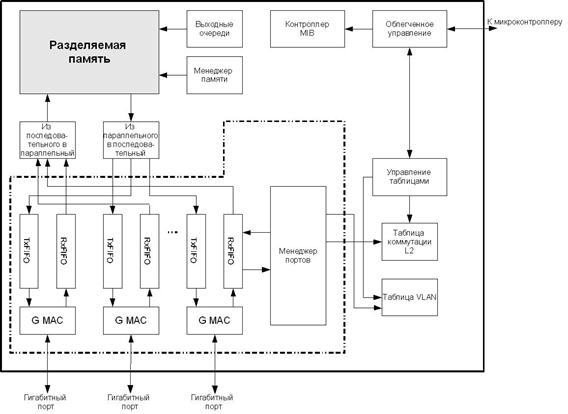

Улучшения архитектуры с разделяемой шиной привели к появлению высокопроизводительной архитектуры с разделяемой памятью (Shared Memory).

Архитектура с разделяемой памятью обычно основана на использовании быстрой памяти RAM большой емкости в качестве общего буфера коммутационной системы, предназначенного для хранения входящих пакетов перед их передачей. Память обычно организуется в виде множества выходных очередей, ассоциирующихся с одним из устройств ввода-вывода или портом. Для обеспечения неблокирующей работы полоса пропускания памяти для операции «запись» и операции «чтение» должна быть равна максимальной суммарной полосе пропускания всех входных портов.

Типовая архитектура коммутаторов с разделяемой памятью показана на рис. 1.12. Входящие пакеты преобразуются из последовательного формата в параллельный и затем записываются в двухпортовую память. Запись в память осуществляется по принципу мультиплексирования с разделением по времени (Time Division Multiplexing, TDM), поэтому в каждый момент времени только один входной порт может поместить кадр в ячейку разделяемой памяти. Заголовки каждого кадра передаются в контроллер памяти. На основе этой информации он определяет выходной порт назначения и выходную очередь, в которую необходимо поместить кадр. Порядок, в котором выходные кадры будут считываться из памяти, определяется контроллером памяти с помощью механизма арбитража. Считанные кадры отправляются на соответствующие выходные порты (выходные кадры демультиплексируются с разделением по времени таким образом, что только один выходной порт может получить доступ к разделяемой памяти), где они вновь преобразуются из параллельного формата в последовательный.

Одним из преимуществ использования общего буфера для хранения пакетов является то, что он позволяет минимизировать количество выходных буферов, требуемых для поддержания скорости потери пакетов на низком уровне. С помощью централизованного буфера можно воспользоваться преимуществами статического разделения буферной памяти. При высокой скорости трафика на одном из портов он может захватить большее буферное пространство, если общий буферный пул не занят полностью.

Архитектура с разделяемой памятью обладает рядом недостатков. Так как пакеты записываются и считываются из памяти одновременно, она должна обладать суммарной пропускной способностью портов, т.е. операции записи и чтения из памяти должны выполняться в N (количество портов) раз выше скорости работы портов. Т.к. доступ к памяти физически ограничен, необходимость ускорения работы в N раз ограничивает масштабируемость архитектуры. Более того, контроллер памяти должен обрабатывать пакеты с той же скоростью, что и память. Такая задача может быть трудно выполнимой в случае управления множеством классов приоритетов и сложными операциями планирования. Коммутаторы с разделяемой памятью обладают единой точкой отказа, поскольку добавление еще одного общего буфера является сложным и дорогим. В результате этого в чистом виде архитектура с разделяемой памятью используется для построения коммутаторов с небольшим количеством портов.

Рис. 1.13. Архитектура с разделяемой памятью

2015-02-24

2015-02-24 1769

1769