Сумматор -- электронное устройство, предназначенное для получения суммы кодов двух операндов (слагаемых). В данном разделе будем рассматривать только комбинационные схемы.

Сумматоры подразделяются на:

- одноразрядные и многоразрядные;

- последовательные и параллельные.

Последовательные сумматоры выполняют операцию последовательно над разрядами слагаемых, начиная с младших разрядов. При этом последовательно поразрядно осуществляется формирование переноса и его суммирование с последующими разрядными частичными суммами.

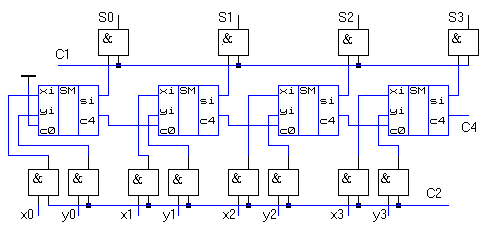

Параллельные сумматоры выполняют операцию одновременно над всеми разрядами слагаемых, однако, перенос, сформированный в младших разрядах последовательно суммируется со старшими частичными суммами.

Для повышения быстродействия при выполнении операций суммирования широко применяют параллельный сумматор. Отличительной особенностью такого сумматора является количество используемых схем ОС-3, которое равно количеству разрядов операндов с учетом знака и анализа переполнения

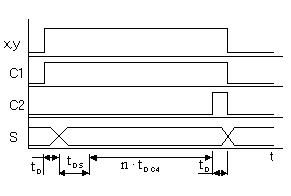

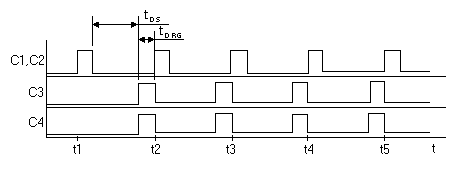

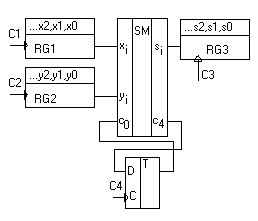

Последовательный сумматор предусматривает использование одного одноразрядного сумматора ОС-3 не зависимо от количества разрядов слагаемых. Схема состоит из двух сдвиговых регистров RG1 и RG2, предназначенных для хранения и сдвига операндов, последовательного регистра RG3 для записи и хранения суммы, одноразрядного сумматора ОС-3, устройства задержки переноса, и качестве которого лучше всего применить триггер. При выполнении разрядного суммирования сформированный перенос будет записываться в этот триггер, а использован перенос будет при выполнении суммирования в следующем старшем разряде. При поступлении младших разрядов операндов x0,y0 на входы сумматора начинается формирование суммы и переноса, которое заканчивается по истечении времени  . После этого можно подавать управляющие сигналы С3 и С4 для записи разрядной суммы в регистр суммы RG3 и переноса в триггер задержки, который будет хранить перенос до прихода следующего разряда операндов. По истечении времени необходимого для записи в регистр можно подавать сигналы С1 и С2 для сдвига операндов, т.е. для подачи на входы сумматора следующего разряда операндов. Быстродействие последовательного многоразрядного сумматора мало и он не находит применения в современной вычислительной технике.

. После этого можно подавать управляющие сигналы С3 и С4 для записи разрядной суммы в регистр суммы RG3 и переноса в триггер задержки, который будет хранить перенос до прихода следующего разряда операндов. По истечении времени необходимого для записи в регистр можно подавать сигналы С1 и С2 для сдвига операндов, т.е. для подачи на входы сумматора следующего разряда операндов. Быстродействие последовательного многоразрядного сумматора мало и он не находит применения в современной вычислительной технике.

2015-04-12

2015-04-12 1223

1223