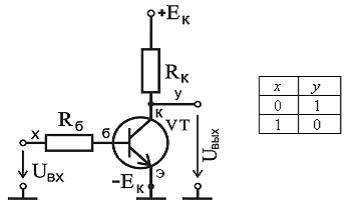

Логический элемент НЕ реализуется с помощью биполярного транзистора n-p-n cтруктуры. Принципиальная электрическая схема транзисторного логического элемента НЕ и его таблица истинности приведены на рис.10.7.

Схема работает следующим образом. Если на вход x логического элемента подать сигнал лог. 0, то транзистор VT будет закрыт и на выходе y появится сигнал лог. 1, так как всё напряжение будет падать на закрытом транзисторе. При подаче на вход x логического элемента сигнала лог. 1, транзистор VT открывается и на выходе y появится сигнал лог. 0, при этом всё напряжение падает на резисторе Rк.

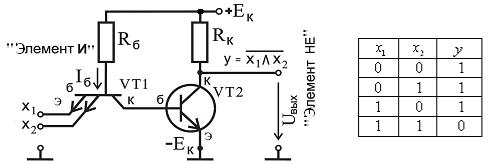

При использовании логических элементов транзисторно-транзисторной логики, построенной с помощью биполярных транзисторов n-p-n cтруктуры, реализуется операция И-НЕ. На рис.10.8 приведена электрическая схема логического элемента И-НЕ и таблица истинности. Схема состоит из двух логических элементов И и НЕ, соединённых последовательно. Транзисторный элемент И имеет несколько входов. На схеме рассматриваются только два из эмиттерных входов х1 и х2 транзистора VT1, коллектор которого соединён с базой инвертора, построенного на транзисторе VT2.

Рис.10.7. Принципиальная электрическая схема транзисторного логического элемента НЕ и его таблица истинности

Рис.10.8. Электрическая схема логического элемента И-НЕ и его таблица истинности

Схема работает следующим образом. Если на входы х1 и х2 транзистора VT1 поступают сигналы лог. 0 или на одном из этих входов присутствует сигнал лог. 1, то базовый ток  пройдет через сопротивление базы транзистора к эмиттерным входам (входу) от “+” источника питания к его “–“. При этом, транзистор VT2 будет закрыт и на его выходе y присутствует cигнал лог. 1. Если на входы х1 и х2 транзистора VT1 поступают положительные сигналы лог. 1, то в этом случае закрываются эмиттерные входы тразистора VT1 и базовый ток

пройдет через сопротивление базы транзистора к эмиттерным входам (входу) от “+” источника питания к его “–“. При этом, транзистор VT2 будет закрыт и на его выходе y присутствует cигнал лог. 1. Если на входы х1 и х2 транзистора VT1 поступают положительные сигналы лог. 1, то в этом случае закрываются эмиттерные входы тразистора VT1 и базовый ток  течет через коллектор тразистора VT1 к базе тразистора VT2, открывая его. При этом на выходе у тразистора VT2 появится синал лог. 0.

течет через коллектор тразистора VT1 к базе тразистора VT2, открывая его. При этом на выходе у тразистора VT2 появится синал лог. 0.

10.5. Логический элемент ИЛИ-НЕ эмиттерно-связанной логики

10.5. Логический элемент ИЛИ-НЕ эмиттерно-связанной логики

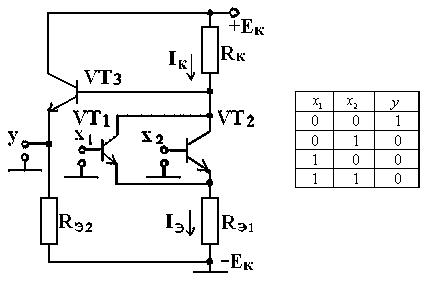

На рис.10.9 изображена электрическая схема логического элемента ИЛИ-НЕ, построенного на транзисторах n-p-n cтруктуры, и его таблица истинности. Если на

входах х1 и х2 транзисторов VT1, VT2 присутствуют входные сигналы лог. 0, то эти транзисторы будут закрыты и сопротивление между их коллекторами и эмиттерами будет бесконечным. При этом коллекторная цепь этих транзисторов будет иметь положительный потенциал, то есть инвертированный сигнал ИЛИ, который будет поступать на вход транзистора VT3. На выходе у транзистора VT3, работающего в режиме повторителя, появится сигнал лог. 1.

В случае поступления на входы х1 и х2 транзисторов VT1, VT2 положительных сигналов лог. 1 или на одном из этих входов присутствует сигнал лог. 1, то их коллекторные цепи будут иметь отрицательный потенциал. При этом транзисторы VT1, VT2 (или один из них) открываются, и сопротивление цепи коллектор-эмиттер будет равно нулю. Так как Rк>Rэ1, то на общем коллекторном выходе транзисторов VT1, VT2 появится отрицательный потенциал, который поступит на вход транзистора VT3 и закроет его. Сигнал на выходе y транзистора VT3 будет иметь лог. 0. Фактически транзистор VT3 является повторителем действия выходного сигнала транзисторов VT1 и VT2, работающих в режиме операции ИЛИ-НЕ.

Рис.10.9. Электрическая схема логического элемента ИЛИ-НЕ и его таблица истинности

2015-04-01

2015-04-01 8799

8799