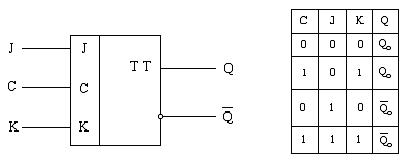

Условное обозначение и таблица истинности двухтактного синхронного

JK - триггера приведены на рис.10.18. Таблица истинности поясняет принцип действия триггера. На синхронизирующий вход С поступают чередующиеся сигналы лог. 0 и лог. 1. Входы J и K являются информационными входами. С прямого выхода Q снимаются двухтактные текущие логические сигналы  и

и  .

.

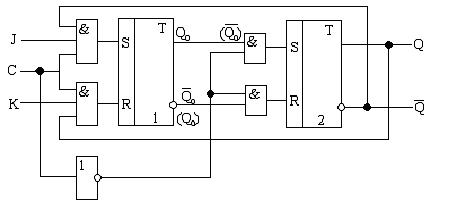

Принципиальная логическая схема JK – триггера (рис.10.19) состоит из двух асинхронных RS триггеров, управляемых через логические элементы И и НЕ.

При поступлении на входы С, J, K логических нулей происходит передача текущего сигнала Q0 с прямого входа триггера 1 к прямому выходу триггера 2.

Если на входы С и K поступают логические единицы, а на вход J логический нуль, то на прямом выходе триггера 2 информация сохраняется. При этом прямой выход триггера 1, по обратной связи, получит инверсный сигнал  0.

0.

Рис.10.18. Условное обозначение и таблица истинности двухтактного синхронного

JK - триггера

Рис.10.19. Принципиальная логическая схема JK – триггера

При поступлении на входы С и К триггера логических нулей, а на вход J логической единицы на прямом выходе триггера 2 появится инверсный сигнал  0, который сохранится при подаче на входы С, J, K единичных логических сигналов.

0, который сохранится при подаче на входы С, J, K единичных логических сигналов.

В результате происходит двухступенчатое запоминание информации.

2015-04-01

2015-04-01 3802

3802