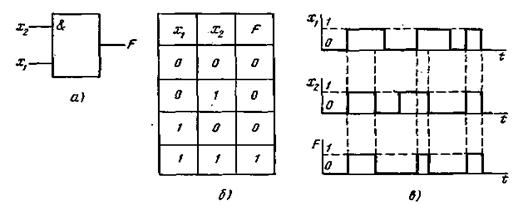

Логический элемент И также имеет несколько входов и один выход. Его условное обозначение показано на рисунке 5.5, а.

Логический элемент И выполняет операцию логического умножения (конъюнкции):

F =x1 · x2 · x3 ·…·xn (5.3)

Здесь функция F = 0, когда хотя бы один из ее аргументов равен нулю, и F =1 при всех аргументах, равных единице.

Работу схемы двухвходового логического элемента И иллюстрируют таблица истинности и временные диаграммы, приведенные на рис 5.5, б, в. Элемент И является схемой совпадения: сигнал "1" на выходе появляется при совпадении сигналов "1" на всех входах.

Рисунок 5.5 - Условное обозначение логического элемента И (а), его таблица истинности и временные диаграммы (б, в)

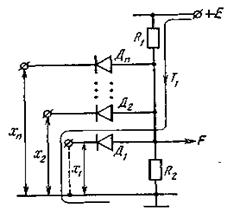

Простейшая схема элемента И на диодах приведена на рисунке 5.6. Отличие от схемы элемента ИЛИ (см. рисунке 5.4) заключается в изменении полярности включения диодов и наличии резистора R1, подключенного к шине "+" источника питания.

Рисунок 5.6 - Схема логического элемента И на диодах

Схема работает следующим образом. При всех входных сигналах, равных единице, на катодах диодов имеется положительный потенциал относительно общей точки и все диоды закрыты. На выходе схемы создается напряжение Е·R2 / (R1 + R2 ), определяющее F = 1. При нулевом значении сигнала хотя бы на одном из входов соответствующий диод будет проводить ток и шунтировать резистор R2, выполняющий, как и резистор R в схеме на рисунке 5.4, роль нагрузки. Напряжение на выходе при этом определяется падением напряжения на открытом диоде и близко к нулю (F = 0). На рисунке 5.6 показан вариант, когда х1 = 0 и проводит ток диод Д1. Увеличение числа входов с нулевым значением сигнала приводит только к увеличению числа проводящих диодов, а функция F остается равной нулю.

В случае применения логического элемента И, имеющего число входов, большее количества входных сигналов, неиспользуемые входы элемента соединяют с шиной "+" источника питания (подают сигнал логической «1»). Диоды неиспользуемых входов будут находиться в закрытом состоянии. Это уменьшает вероятность прохождения помех на выход элемента И от наводок по неиспользованным входам. Состояние выхода логического элемента будет зависеть от комбинации входных сигналов в соответствии с таблицей истинности (рисунок 5.5, б).

2015-04-01

2015-04-01 709

709