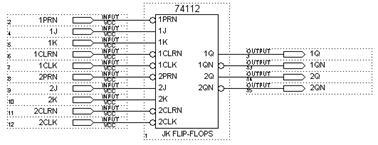

Модуль 74112 (рис.3.1) – двойной JK-инверсный регистр с входами предварительной установки и сброса, состоит из двух JK-триггеров, все входы и выходы которых отдельные. Данный модуль содержит:

ü инверсные входы предварительной асинхронной установки CLRN и сброса PRN;

ü информационные входы J и K;

ü входы синхронизации CLK (синхронизация осуществляется отрицательным фронтом импульса);

ü выходы прямые Q и инверсные QN

Рис. 3.1. Двойной JK-инверсный регистр с входами предварительной установки и сброса

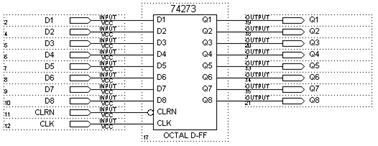

Модуль 74273 (рис.3.2) - регистр с параллельной записью информации, состоит из восьми D-триггеров с общими для них входами установки и синхронизации. Модуль содержит:

ü восемь информационных входов D;

ü вход установки CLRN;

ü синхронизирующий вход CL K.

Рис. 3.2. Регистр с параллельной записью информации

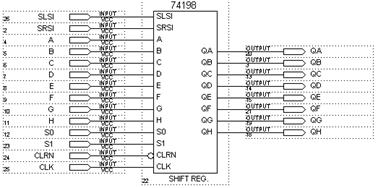

Модуль 74198 (рис.3.3) – регистр с последовательным и параллельным вводом информации, представляет собой 8- разрядный реверсивный регистр сдвига. Модуль содержит:

ü вход установки CLRN;

ü синхронизирующий вход CLK.

ü входы выбора режима работы S1 и S0;

ü последовательные входы приема данных SLSI (сдвиг данных влево)и SRSI (сдвиг данных вправо);

ü параллельные входы приема данных A, B, C, D, E, F, G и H;

ü выходы QA, QB, QC, QD, QE, QF, QG и QH.

Рис. 3.3. Регистр с последовательным и параллельным вводом информации

Регистр обеспечивает функционирование следующих режимов, устанавливаемых с помощью входов S1 и S0, при CLRN=1:

ü  хранение данных (блокировка) (S1=0, S0=0, CLK = и при S1=Х, S0=Х, CLK=0);

хранение данных (блокировка) (S1=0, S0=0, CLK = и при S1=Х, S0=Х, CLK=0);

ü  сдвиг вправо (S1=0, S0=1, CL K=);

сдвиг вправо (S1=0, S0=1, CL K=);

ü  сдвиг влево (S1=1, S0=0, CLK =);

сдвиг влево (S1=1, S0=0, CLK =);

ü  параллельная загрузка (S1=1, S0=1, CLK =).

параллельная загрузка (S1=1, S0=1, CLK =).

При подаче низкого уровня на вход CLRN выходывсех триггеров устанавливаются в состояние низкого уровня вне зависимости от логических значений на других входах.

В работе регистр исследуется как преобразователь параллельного кода в последовательный (для этого используют режим параллельной загрузки входной информации, а вывод осуществляется через выход QH или QA), а затем как преобразователь последовательного кода в параллельный (в этом режиме ввод информации производится через последовательный вход, а вывод осуществляется в виде параллельного кода).

При преобразовании последовательного кода в параллельный входной сигнал подается на один из последовательных входов (SLSI или SRSI). Возможны два варианта подачи сигналов:

ü  входной сигнал подается на вход SRSI, тогда S1=0, S0=1, CLK = (сдвиг вправо) и выходной сигнал формируется начиная с QA;

входной сигнал подается на вход SRSI, тогда S1=0, S0=1, CLK = (сдвиг вправо) и выходной сигнал формируется начиная с QA;

ü  входной сигнал подается на вход SLSI, тогда S1=1, S0=0, CLK = (сдвиг влево) и выходной сигнал формируется начиная с QН.

входной сигнал подается на вход SLSI, тогда S1=1, S0=0, CLK = (сдвиг влево) и выходной сигнал формируется начиная с QН.

2015-04-08

2015-04-08 2753

2753